采用交错正激三电平技术的48 V输入电压调节模块研究

2017-11-03章艳

章 艳

(1.江苏大学电气工程学院,江苏 镇江 212013;2.南京信息职业技术学院,南京 210023)

采用交错正激三电平技术的48V输入电压调节模块研究

章 艳1,2

(1.江苏大学电气工程学院,江苏 镇江 212013;2.南京信息职业技术学院,南京 210023)

48 V输入电压调节模块是一种直流-直流供电电源,主要用于计算机微处理器供电。基于三电平变换器理论,提出了一种交错正激式三电平直流变换器,并使用这种结构设计了输入电压为48 V的电压调节模块。分析了这种变换器的工作过程、三电平工作的环境,并与普通的交错并联型Buck变换器进行比较,构建了一个输出0.8 V/100 A 80 W的模型样机并进行了试验验证。实验表明,这种变换器提高了电压调节模块的动态响应速度,减小了输出滤波电容器的大小,有广泛的应用价值。

电压调节模块;三电平直流变换;48 V输入

伴随低压集成电路(IC)制造技术尤其是在微处理器领域的迅猛发展,IC对供电要求呈现下列趋势[1]:工作电压越来越低,未来的IC工作电压将降低到1 V以下;电流越来越大,由于微处理系统处理容量的巨增,从而使得总功耗激增,IC的供给电流将会超过100 A;负载变化率越来越高,由于为了节能而采用电源管理功能,就使微处理器成为一个电流变化率很高的di/dt>150 A/μs)非常动态的负载[2]。通常,专为微处理器设计的供电单元是电压调节模块(VRM),上述因素都将对VRM的设计提出全新的挑战。

早期VRM的电源是采用5 V直流母线直接供电的,为了提高转换效率,在笔记本电脑上VRM采用了直接将输入电压提高到16 V~24 V,再变换到1.5 V输出。但无论采用5 V或者12 V输入,其电路拓扑结构基本采用的都是Buck变换器,并采用同步整流技术用以提高其转换效率[3]。但上述电路的缺点是采用非隔离的Buck电路,其输入电压变化也是从低到高,Buck电路显然不能适应未来VRM发展的需要,因而采用隔离型DC/DC变换已经成为必然趋势[4]。未来随着微处理器功率的逐渐增大,致使CPU所需电压降低、电流增大,采用5 V或12 V输入电压作为VRM的输入电压仍显得不够高,因此需要继续提高VRM输入电压。目前,VRM把输入母线电压提高到48 V已成趋势[5]。48 V输入母线电压带来的好处有:可有效减小引线电流从而降低引线损耗,提高效率;提高负载动态响应能力;大大减小输入滤波器体积。提高VRM动态特性的重要策略是减小输出滤波电感,传统的两电平电压变换器只有通过提高开关频率才能满足这一要求,而三电平电压变换器有利于减小VRM输出滤波电感,从而提高其动态响应速度[6]。

基于上述原因,本文给出了一种新的交错正激式三电平直流变换器和使用这种结构设计的48 V电压调节模块。文章分析了这种变换器的工作过程、三电平工作的环境,并与普通的交错并联型Buck变换器相比较,进行试验验证,得到了电源转换效率较高、负载动态响应好的设计结果。

1 VRM主电路设计

目前较为流行的各种VRM拓扑[7-8],其输出滤波电感器的供电波形均为二电平波形,为了将动态响应速度提高,一般使用的方法是:通过提高主电路的工作频率来减小后级滤波电感量,但受系统效率因素的制约开关频率一般不能太高;二是多路并联交错电路使得其等效输出电感减小。但采用多路交错并联一方面使得磁性元件个数增加,控制复杂,成本提高;另一方面加在每路电感上的纹波较大,不利于效率提高。

三电平变换器理论[12]用三电平代替二电平通过输出滤波电感给负载供电,可以有效的减小输出滤波电感[9-10]。基于此,本文设计出了输入电压为48 V的VRM拓扑——“正激式交错并联三电平”型VRM。

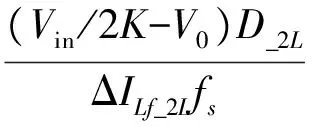

正激式交错并联的三电平变换器的结构见图1。Cd1、Cd2为两个分压电容,容量大且同值。VCd1=VCd2=1/2Vin。

图1 交错并联正激式三电平变换器

Q1和Q3同相位工作,Q2和Q4同相位工作,但这两组开关功率管分开交替工作,驱动信号相角差180°。为分析方便,把Q1和Q4叫做下管,Q2和Q3叫做为上管。因变压器复位影响,Q1~Q4开关功率管的最大占空比均是0.5。同时变换器在不同的工作状态时的工作模式亦会不同,当下管Q1、Q4的占空比D≠0时变换器工作在三电平模式3L_Mode(Three-Level Mode),当下管Q1、Q4占空比D=0时,变换器工作在两电平模式2L_Mode(Two-Level Mode)。

2 参数设计

2.1 变压器变比K

在正激式交错三电平变换器在3L_mode时,其输入端和输出端电压的关系为[12]:

V0=[(0.5+D_3L)Vin]/k

(1)

因此变压器的变比K为:

K_3L=[(0.5+D_3L)Vin]/V0

(2)

变换器工作在2L_mode时输入端和输出端关系为:

V0=(D_2LVin)/K

(3)

因此变压器的变比K为:

K_2L=(D_2LVin)/V0

(4)

2.2 输出滤波电感Lf的设计

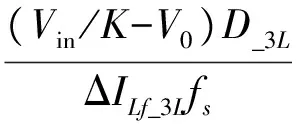

3L_mode时,Lf电流脉动值:

ΔILf_3L=[(Vin/K-V0)D_3L]/Lffs

(5)

(6)

2L_mode时,Lf电流脉动值:

ΔILf_2L=[(Vin/2K-V0)D_2L]/Lffs

(7)

(8)

2.3 输出滤波电容Cf的设计

VRM常工作在负载变换率大、动态速度要求快的场合,其输出滤波电容Cf的设计与常规应用场合的设计有所不同。

对VRM来说,其输出电容是按照满足负载突变的要求设计,可按下式[13]计算:

(9)

式中:Td为瞬态过程中时间延迟;ΔI0为负载电流突变量;ΔV0为输出纹波电压;SR(IL)为有效电感电流变化率。

在开关工作频率比较高的情况下,控制环路合理设计时,Td对Cf数值大小所产生作用可以忽略不计。为设计简便,省去上式右面第一项,则有:

(10)

3 控制方案

VRM经常被用于低压大电流输出的场合,常规的快速二极管和肖特基二极管由于管压降太大已不适用于VRM中副边整流和续流用。目前VRM中一般在副边使用同步整流管,正常情况下用低压大电流MOSFET,它的通态阻抗Rds(on)很小。图2是使用同步整流管的正激交错三电平变换器,Q5、Q6、Q7是同步整流管。设置控制电路时,必须保证该变换器可以在3L模式和2L模式之间自由切换。

图2 使用同步整流管的正激交错三电平变换器

图3 变压器原边和输出滤波器上的电压波形

4 实验结果与分析

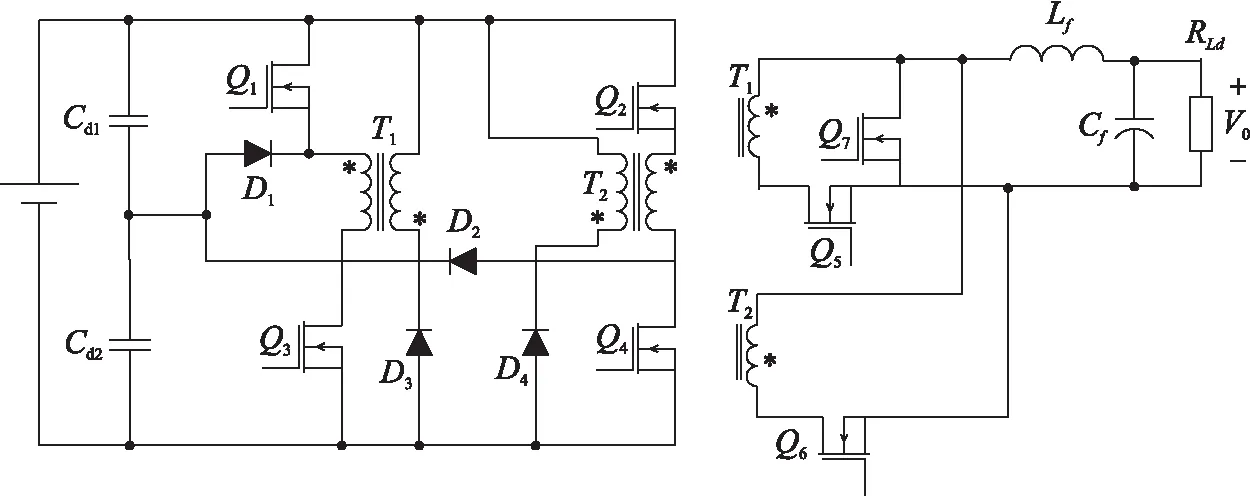

利用上面的计算方法所得参数,试制了一台输出0.8 V/100 A的模型样机,来证明正激式并联交错三电平变换器的工作原理。该样机的主电路板用10层PCB板,变压器和输出滤波电感均采用平面磁芯,其绕组直接印制在PCB板上,以减少变压器漏感和主电路副边的连接点,从而提高变换器效率。实验所用的数据为:

输入直流电压:Vin=36 V~72 V

输出滞留电压:V0=0.8 V

输出电流:100 A

开关频率:fs=300 kHz

输出滤波电感:Lf=100 nH(Philip EI32 Core)

输出滤波电容:Cf=6 890 μF(8x 4SP820和15x 22μF ceramic cap.)

开关功率管Q1、Q4:Si4486EY

开关功率管Q2、Q3:Si4488DY

输出同步整流管(Q5、Q6、Q7):STV160NF02L(2只并联)。

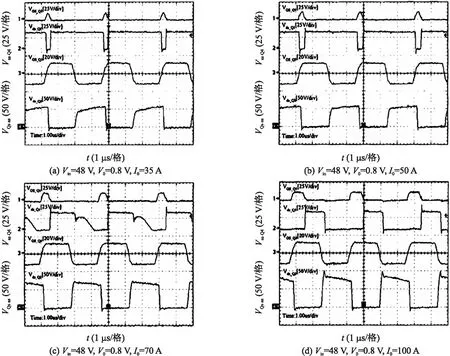

其系统的主要实验波形如图3所示。图3显示了Vin=36 V~72 V条件下,主变换器的变压器T1原边和输出滤波器上的电压波形。波形显示在I0=100 A,输入36 V及48 V时系统均工作在三电平模式,而且Q1和Q4占空比在Vin=36 V时较大(D=0.5),在Vin=48 V时则较小,如图3(a)、图3(b)所示。在I0=100 A,Vin=72 V时变换器为两电平工作模式,如图3(c)所示。图3(d)则显示了48 V输入,I0=50 A时T1原边及输出滤波器上的电压波形,由图3可见,控制策略的结果和设计完全的相同,并得到了完整的三电平波形。

图4 主要开关驱动波形(Vin=48 V,V0=0.8 V,I0=100 A)

图4给出的是Q1~Q4的驱动波形。图4(a)波形为Q1、Q3和Q5管上的驱动信号。Q2、Q4和同步管Q6相对应的开关功率管驱动与前者完全相似,仅仅是相位不同而已。图4(b)显示了并联的两路T1原边主功率开关的驱动信号相位关系,驱动相差为180°。

图5 主开关漏源极间电压波形

图5是在不同负载状态下主开关功率管上的Vds电压波形。此处仅给出了Q1、Q3的Vds电压波形,Q2、Q4的Vds电压波形基本相同。从图中可知,由于存在D1的箝位作用,使Q1在关断时的反向电压VdsR1=VIN/2。而Q3的VdsR3则会随负载的变化而稍有变化,当I0=35 A及50 A时小于理论值3VIN/2,当I0=70 A时基本与分析值3VIN/2相同,当I0=100 A时却大于3VIN/2。这种变化的原因主要来源于原边电压复位时,其VdsR3随负载变化而稍有变化,并不是整个复位期间始终保持在3VIN/2。

图6是在给定输入和输出时,有均压电路和无均压电路时变换器原边电压波形情况比较。图6(a)未加均压电路时,Vcd1、Vcd2的值不相等,Vcd2比VIN/2大得多,Vcd1要比VIN/2小得多。图6(b)在加入了均压电路后,两个电容电压基本都为VIN/2。

图6 均压电路的效果比较

5 结论

本文通过对一种新型正激式并联交错三电平变换器工作过程的分析讨论,并定量的分析设计了输出滤波电感和输出滤波电容的参数,将其应用到VRM中,得到的优点是可以极大的减小输出滤波电容和电感。同时用一个输出0.8V/100A 80W的模型样机试验,得出的实验结果证明了变换器的先进性与分析的准确性。

[1] 张晓峰,冯浩. 一种新型的双频VRM电路[J]. 第三届中国高校电力电子与电力传动学术年会,2010.

[2] Antonietta De Nardo,Nicola Femia,Giovanni Petrone.Optimal Buck Converter Output Filter Design for Point-of-Load Application[J]. IEEE Transactions on Industrial Electronic,2010,57(4):1330-1341.

[3] David Reusch,Fred C Lee,Doug Sterk.Improved Transformer Design for High Frequency VRM Applications[J]. IEEE Center for Power Electronics Systems.2008:1483-1489.

[4] 付兴武,周洁,叶菁源,等. 三相VRM集成电感的稳态性能研究[J]. 电力电子技术,2014,48(1):88-90.

[5] Seiya A,Masahiko H,Masahiko S,et al. Optimal Intermediate Bus Capacitance for System Stability on Distributed Power Architecture[C]//Proc.IEEE PESC,2008:611-616.

[6] 梁锦桃,王志强. 适用于48 V供电系统的VRM拓扑分析[J]. 电力电子技术,2014,48(1):88-93.

[7] Ke Jin,Yi Sun,Ming Xu,et al. Integrated Magnetic Self-Driven ZVS Nonisolated Full-Bridge Conveter[C]//IEEE Transactions on Industrial Electronic.2010,56(5):1615-1623.

[8] Xia C L,Gu X,Shi T N,et al. Neutral-Point Potential Balancing of Three-Level Inverters in Direct-Driven Wind Energy Conversion System[J]. IEEE Transactions on Energy Convers,2011,26(1):18-29.

[9] 贺明智,陈骞,郑琼林. VRM动态响应特性的研究[J]. 北京交通大学学报,2011,35(2):88-90.

[10] 单国栋. 三电平Buck直流变换器控制策略研究[D]. 重庆大学,2012.

[11] 罗怀,黄子珍,单国栋. 定频滑模控制三电平Buck变换器研究[J]. 电气技术,2015,16(1):40-43.

[12] 唐立华,陈昭炜,单国栋,等. 一种新型零电压转换三电平Buck变换器的研究[J]. 电器与能效管理技术,2012,24(21):21-25.

[13] 李江达,何颖,,杨兵,等. 一种四相交错并联Boost DC/DC变换器的设计[J]. 电子与封装,2013,13(11):13-16.

AStudyof48VInputVoltageRegulatorModuleBasedonStaggeredForwardModeThreeLeverDC

ZHANGYan1,2

(1.College of Electrical and Information Engineering,Jiangsu University,Zhengjiang Jiangsu 212013,China;2.Nanjing College of Information Technology,Nanjing 210023,China)

The voltage regulator module(VRM)is a DC to DC power supply,which is mainly used to power for microprocessors. A staggered forward mode three lever DC converter is presented based on the theory of three lever convertor. Compared with an interleaving Buck converter,a 48 V input voltage regulator module is designed based on this new structure,where the working processes of this convertor and the environment of the three level DC are analyzed and simulated. Furthermore,a 0.8 V/100 A 80 W-output prototype is demonstrated and experimented. The experiment results are shown that the respond speed is improved and the output filter capacitor is decreased.

voltage regulator module(VRM);three level DC converter;48 V input

10.3969/j.issn.1005-9490.2017.05.020

2017-08-08修改日期2017-08-23

TN713.1

A

1005-9490(2017)05-1151-05

章艳(1979-)女,汉族,江苏省,江苏大学电气工程学院,硕士(高校教师),主要研究方向电气传动与直流变换技术,Zhangy_zk@njcit.cn。