一种基于测例层模型的功能验证方法*

2017-11-03王明江雍珊珊王新安

谢 峥,王明江*,雍珊珊,王新安

(1.电子与信息工程学院,哈尔滨工业大学深圳研究生院,广东 深圳 518055;2.信息工程学院,北京大学深圳研究生院,广东 深圳 518055)

一种基于测例层模型的功能验证方法*

谢 峥1,王明江1*,雍珊珊2,王新安2

(1.电子与信息工程学院,哈尔滨工业大学深圳研究生院,广东 深圳 518055;2.信息工程学院,北京大学深圳研究生院,广东 深圳 518055)

针对集成电路功能验证的完整性和重用性问题,使用测例层模型,构建协议功能完整覆盖的验证计划,并使用UVM验证方法和库函数搭建验证环境,对一款符合GJB 800/900 MHz RFID芯片系统的设计进行功能验证。所提出的测例层模型具备通用性。填充协议内容后的模型,在满足相同协议的设计之间可重用,在相似协议或非完整协议的设计中也可重用,即面向协议的测例层VIP及其构建方法。最终保证了GJB协议芯片的验证覆盖率,在TSMC 0.18 μm工艺流片成功。

功能验证;测例层模型;RFID;UVM

随着超大规模集成电路制造工艺技术向14 nm、10 nm[1]、甚至7 nm[2]的进步,集成电路设计复杂度也不断提高,SoC的验证工作已经占据了约70%的设计时间[3],迫切需要功能验证方面新方法学的指导。从2000年的e语言的诞生,到eRM可重用方法学、基于vera语言的RVM方法学、基于SystemVerilog和SystemC的AVM方法学、VMM方法学、URM方法学、OVM方法学,再到现在主流公司全部支持的UVM方法,可以看出以重用性来提高功能验证效率的方法得到了较好的发展。然而验证重用性仍然具有3个纬度的发展空间:从SoC到衍生产品的重用;从IP到SoC的重用;不同抽象级别在架构、设计、软件、验证等混合平台上的重用[4]。

功能验证的本质是保证设计功能的正确性,由于设计的复杂度限制了完整功能描述的形式化定义,以及形式验证方法对其进行检查的范围,所以需要“完整”的功能测试集合的支持。然而“完整”的功能测试集合实际中是以约束随机和定向相结合来实现的。基于仿真的验证,包括testcase和testbench,基于UVM的方法在testbench层较好的支持了各细分层次(场景层、功能层、命令层、信号层等)的组件以及功能覆盖率的定义和收集过程,形成了较完整的框架结构。testcase层是面向内容的层次,直接和功能测试用例、功能覆盖点、功能参考模型相关。在基于标准协议的设计中使用黑盒验证的方式时,testcase层的内容具有在3个纬度上更广泛的重用性。

本文提出了在testcase层的模型,通过对模型进行协议内容的填充和建模,产生完整的功能测试用例、完整的功能覆盖点、完整的功能参考模型。首先对自然语言的功能描述或标准协议向模型进行填充和映射,再从模型向验证环境中的相关组件进行内容上的映射和转化,从而实现了对功能验证完整性和重用性的保证。再配合testbench层的UVM方法,在GJB 800/900 MHz RFID芯片系统设计项目中,保证了流片的成功。

1 功能验证的基本原理

待验证设计(DUV)的功能模型是一个功能集合F,由fi函数作为元素组成,其中fi以输入集合U为参数,U由变量uj组成,对于fi函数可以使用U的子集Ui,如式(1)~式(3)。

F={fi(U)},i∈{1,…,I}

(1)

U={uj},j∈{1,…,J}

(2)

fi(Ui),Ui⊆U

(3)

在输入集合为非离散的或离散的巨大空间时,对函数fi的输入遍历在基于仿真的验证中是不实际的。从功能角度,功能覆盖矩阵(FCM)是覆盖率驱动的验证(CDV)的基础。功能覆盖率矩阵的关键在于切分和组合。对变量uj的取值集合Sj进行划分,划分成Dj个子集。那么对于拥有L个变量的fi函数的组合数就有C(fi)个,如式(4)、式(5)所示。

Sj=Sj(1)∪Sj(2)∪…∪Sj(Dj)

(4)

(5)

当验证fi函数时,测例遍历所有C(fi)个组合。对于其中一种组合Vk(fi),其各变量uj的值为v(uj),v(uj)从Sj(d(k))子集中随机选择,且d(k)是Vk(fi)这种组合与变量uj的取值集合Sj的分组之间的关系。在约束随机验证中,d(k)是一种约束,如式(6)~式(7)。

Vk(fi)={v(uj)},uj∈Ui,k=1,…,C(fi)

(6)

v(uj)=rand(Sj(d(k))),d(k)=1,2,…Dj

(7)

在细化的过程中,U对应testbench中的组件,比如driver、receiver、stimulator、responder等[5]。文献[5]中使用了简单的线性划分器,使各子集的大小相等,即

Sj(a)∩Sj(b)=φ,a,b=1,2,…Dj, ifa≠b

(8)

如果输入存在相关性,对变量uj的取值集合Sj的划分则不严格遵守式(8),遵守式(4),在这种情况下一些组合成为非法的,所以

(9)

功能集合F对fi(U)函数的选择是对DUV的配置,带有分段函数的特点。下标i在fi(U)中可以被看作是输入集合U的一部分。在分层的验证环境的顶层,其表现为场景的设置过程。

根据抽象层次,输入集合U演变成了transaction或信号中的参数或者向量。DUV的功能模型可以被扩展出一个顺序性的维度,或一个结构性的维度。当引入时间参数t后,式(1)被描述成

F(t)={fi(U)},i∈{1,…,I}

(10)

当t被忽略时,F是一个用来处理应用数据包的算法模型,或一个处理总线transaction的程序设计员视角的模型,由transaction事件触发。当t被粗略的时间化后,F(t)成为了一个总线周期精确的模型,或程序设计员视角加时间的模型。当t被周期精确化后,F(t)成为一个周期精确的模型,由时钟信号触发。所以式(6)可以转化为

Vt,k(fi)={v(uj)},

uj∈Uik=1,…,C(fi)t=t1,t2,…

(11)

式中:时间点基于触发事件。一个输入序列Seq表示为

Seqt1,tn=Vt1,k(fi),Vt2,k(fi),…,Vtn,k(fi)n=1,2,…

(12)

=>F(t1),F(t2),…,F(tn)n=1,2,…

(13)

=>Sample(t1),Sample(t2),…,Sample(tn)

n=1,2,…

(14)

组合Vt,k(fi)的排序相当于DUV功能模型的顺序性维度,代表了功能之间的切换。同时Sample(tn)是监控过程收集的结果,一个Seq可以混合Vt,k(fi)和子序列Seqsub,如式(15):

Seqt1,tn=Vt1,k(fi),Vt2,k(fi),…,Seqsub,…

(15)

原则上系统不停止,Seq可以是无限的。但是实际系统中,在序列Seq中具有相关性的Vt,k(fi)之间的跨度是有限的。如1-2相关,跨度为1,可表示Vt1,k(fi)和Vt2,k(fi)存在相关性。扩展顺序性维度后,FCM的核心又扩展到序列Seq中组合Vt,k(fi)之间相关性的种类。

在一个实际的实现implementation中,一个变量uj可以通过一个或多个接口(interface)的相关序列Seq(intf)来表示,且满足规则r(u,Seq(intf))。同样,组合Vt,k(fi)和序列Seqt1,tn也可以根据规则r(V,Seq(intf))和r(Seq,Seq(intf))来通过和接口相关的序列Seq(intf)进行实现。

v(uj)=>Seqt1,tn(intfm),m=1,2,3,…n=1,2,3,…

r(u,Seq(intf))∈R(16)

Vt,k(fi)={v(uj)}=>{ Seqt1,tn(intfm)}

r(V,Seq(intf))∈R(17)

变量集合Sharedua_b表示b模块的输入变量且来源于a模块的输出变量,则有式(24)~式(26)。

DUV可以被看作是一个状态机通过输入触发,其输出函数仅由当前输入或输入和当前状态决定。当前状态又由初始状态和输入序列决定。在模块化设计中,系统被分割成了很多模块,系统功能集合Fsystem通过多模块的协同工作实现,如式(27):

Fsystem=Fmodule_1×Fmodule_2×…×Fmodule_nn=1,2,3,…

(27)

模块级验证中模块a的输入直接被testbench控制。在系统级验证中,testbench直接控制顶层输入,此时模块a的输入被间接控制。对模块a的间接控制通过顶层输入和其他模块,如式(28):

Fmodule_a=Fsystem/(Fmodule_1×Fmodule_2×…×Fmodule_n)n≠a

(28)

实际的模块设计,特别是IP设计时,模块的功能定义可能超出系统要求范围或对模块的原始功能需求描述,所以模块a实现的功能集合Imp(Fmodule_a)可能会大于系统分配给该模块的功能要求Ori(Fmodule_a):

Ori(Fmodule_a)⊆Imp(Fmodule_a)

(29)

在文献[6]中,丢失的规格要求被发现来源于两个连接模块YοX中Y模块的输入域和X模块的输出域的失配。如果验证Y通过控制X的输入,那么对Y的验证可能会存在一个漏洞。即相连的模块X和模块Y即使原始定义中没有出现失配,但是在实现时也可能存在失配现象,表示为式(30)、式(31):

Domain_mis_o_i(Ori(Fmodule_X), Ori(Fmodule_Y))=φwhen SharedintfX_Y≠φ

(30)

◇∃Domain_mis_o_i(Imp(Fmodule_X),Imp(Fmodule_Y))≠φwhen SharedintfX_Y≠φ

(31)

模块验证应该在系统验证之前完成,但是即使如此,模块功能也应该服务于系统需求,所以模块间的失配并不一定是bug,可能是issue,这就意味着集成验证或系统验证时,模块验证组件的重用需要修改,比如覆盖点。

但是如果原始分给a模块的功能不在实现功能之中,或输入输出域不在实现之中,则必然存在bug,表示为

when Ori(Fmodule_a)¢Imp(Fmodule_a)or

Domain_i(Ori(Fmodule_a))¢ Domain_i(Imp(Fmodule_a))or Domain_o(Ori(Fmodule_a))¢ Domain_o(Imp(Fmodule_a)),□∃a bug

(32)

2 测例层模型

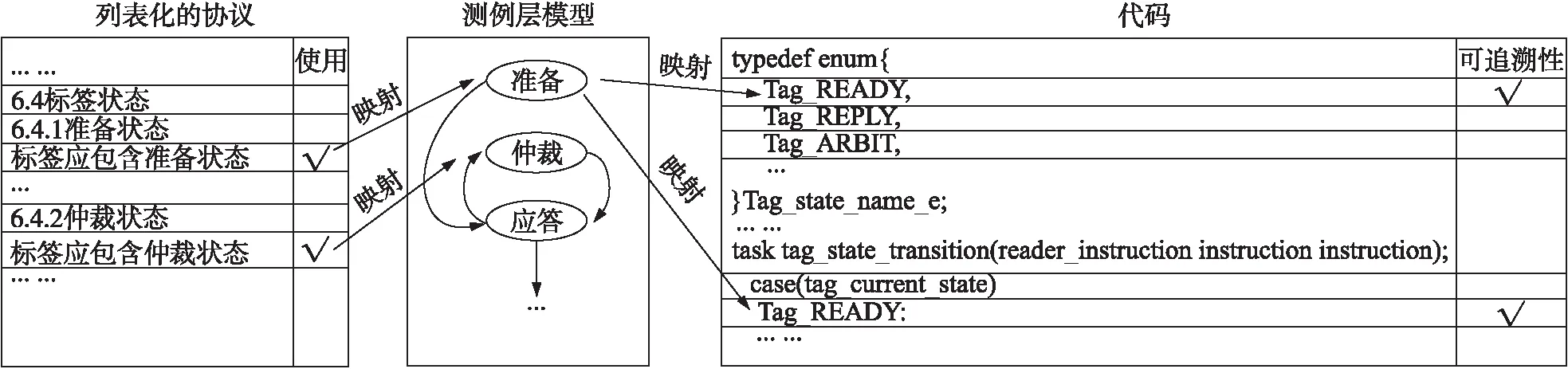

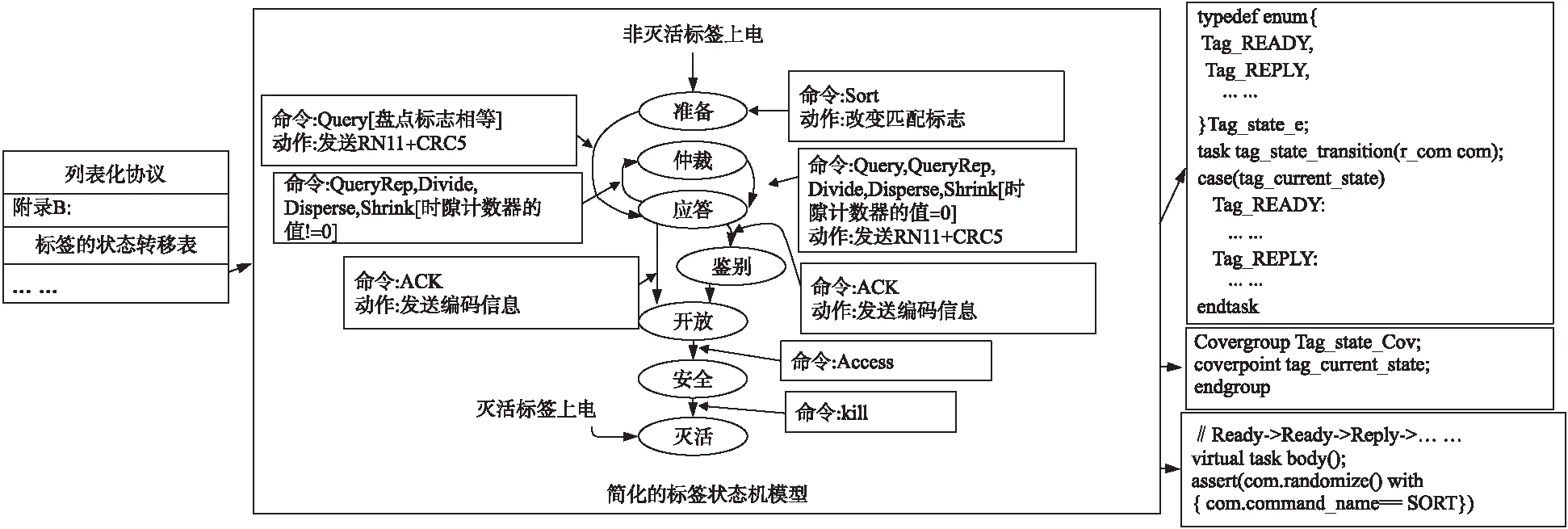

由上述功能验证的基本原理可知,不论使用何种语言进行验证,不论使用何种验证方法学或何种验证组件构成的验证环境,对功能的全面梳理最为重要。对于遵循标准协议的设计,功能验证的重点是基于协议或规格,所以验证组件的开发应该是一个梳理、理解、提取和转换协议的过程。除了文字描述,协议还经常以波形图、流程图、状态机图、序列图等表示。波形图强调信号在时钟周期级别的细节描述。流程图聚焦于某一流程中面向不同中间结果的操作步骤。状态机致力于其自身状态转换的描述。序列图用于描述不同模块之间的交互的场景。流程图模型、状态机图模型、序列图模型都属于测例层的模型,以描述协议中的事务。同时类模型被用来记录包结构和通用操作。协议中不好归属上述模型的,使用列表模型将其记录,实现对协议的完全分解。自然语言描述存在随意性和模糊性,形式语言描述对操作人员要求较高,测例层的模型是一种半形式化的方法适合理解和复查[7]。对协议进行列表化,将列表化后的协议向测例层模型进行映射,以检查协议使用是否有疏漏,将测例层模型向代码进行映射以检查代码中的漏洞,从而减少了人为引入的错误,并提高了代码的协议可追溯性,如图1所示。

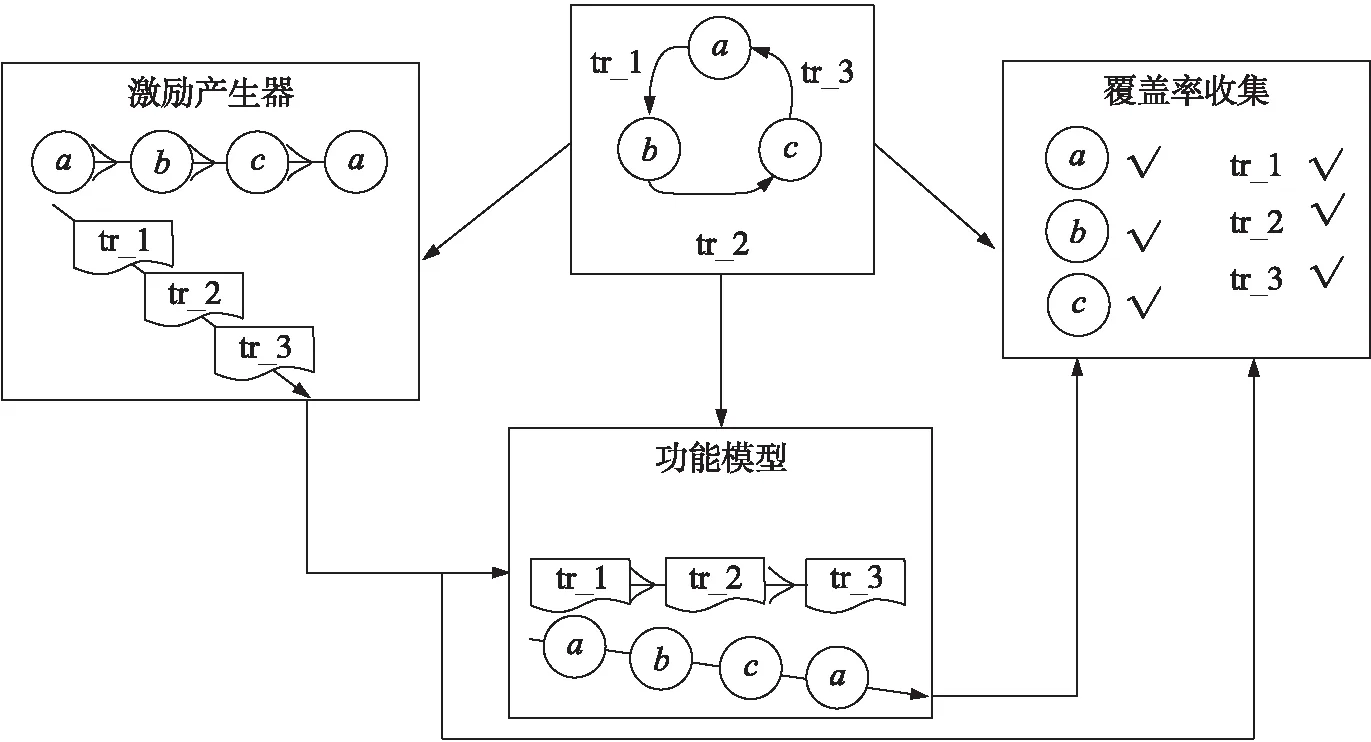

映射过程需要量化协议,增加可数性。在协议中数据结构的量词对应类和变量,描述操作的动词转化成任务和函数,对象的形容词转化成枚举类型。通过分散的应用场景和通信场景聚合成一个完整的模型。不论全功能模型(FFMs)或总线功能模型(BFMs),功能模型应包括式(1)中功能集合F所涉及的所有功能,如图2所示。

图1 相关性映射

图2 分散场景聚合为完整模型

图3 验证组件的同源性

激励产生器、功能模型、覆盖率收集是同源的,如图3所示,它们是对协议特征的不同种表述形式。协议被列表化和模型化以后,属性和断言的提取变得更简单,特别对于BFMs模型。类似图形化的语言[8],模型提供了一个通过模板自动转化为所需描述语言的机会,同时图形化的模型便于分析[9]、评估[10]和遍历[11]。由于功能与实现的分离,测例层的模型在作为一种黑盒方法应用时,可以面向满足相同协议的任何设计。基于测例层模型的driver可以通过算法遍历模型中的所有需要的路径,以重建测点和覆盖率,从而弥补原始协议中可能未提出的盲点和缺陷。与形式化方法不同,其遍历路径后仍需要仿真验证,针对的多为事务级处理对象,且可以根据需要遍历具有特定特征的路径。对于一个类模型,通过域的交错来构建覆盖点。对于一个流程图模型,从起点到终点的所有路径构成了各种测试场景。对于事务级状态机模型,状态的覆盖点、状态转移的覆盖点、状态转移序列的覆盖点被建立。对于序列图模型,所有多对象之间可能的通信可以被找到。这些都提高了验证的完整性。功能模型作为一个可执行的协议,将通信和计算分离更适合重用、调试和性能评估。

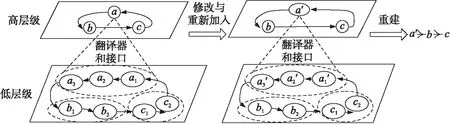

不论是自顶向下还是自底向上的重用,不论是同一个设计不同阶段的重用还是满足同一个协议的不同设计之间的重用,对现存验证资源的合理的调整方法是重用效率的保证。对于测例层模型的调整,使得代码可以通过模板自动匹配模型而产生更改[12]。验证技术管理中,对主特征,非主特征,边角特征和不同优先级的划分可以适应快速验证和详尽验证的需求,这些需求可以在列表模型中实现。对于协议需要一个详尽可配置的模型,再根据设计需求、不同的验证级别和验证组件,在该模型上进行选择和定制化。在验证的不同阶段,模型需要不同的翻译器和接口来针对不同抽象级别或不同接口协议之间进行转换。对于局部特征的修改,通过修改模型中的节点来重新加入模型和重建组件,其复杂度和所修改模型节点的粒度相关,如图4所示。

图4 模型节点修改与重建

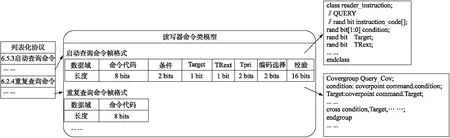

图5 类模型构建读写器命令类及覆盖率

3 GJB RFID的设计验证

GJB RFID协议的工作频率为840 MHz~845 MHz和920 MHz~925 MHz,频带内40个信道。读写器使用TPP基带编码,标签使用FM0和Miller编码。作为命令应答型系统,读写器和标签都有启动、初始化、处理命令、接收信号、传送信号的过程。在事务级,接收和传送命令的功能在编解码之前。加解密功能需要鉴别。标签的初始化流程导入参数来设置4个逻辑存储区,信息区、编码区、安全区和用户区,预设各种标志位,比如灭活位、灭活使能位、锁定使能位、安全模式。标签类有3个状态机模型,表述标签状态的转换、FM0编码和Miller编码。前导码与命令码的处理过程分离。容差管理在接收和传输信号的过程中进行。读写器具有防碰撞DDS-BT机制,以及和上位机的通信。

读写器命令集分为盘点组命令和访问组命令,包括分类命令(Sort)、启动查询命令(Query)、重复查询命令(QueryRep)、分裂命令(Divide)、分散命令(Disperse)、收缩命令(Shrink)、编码获取命令(ACK)、应答错误命令(NAK)等。对命令的验证使用约束性随机验证,并配合需要的场景。覆盖率包括命令域值和交错域,如图5所示。

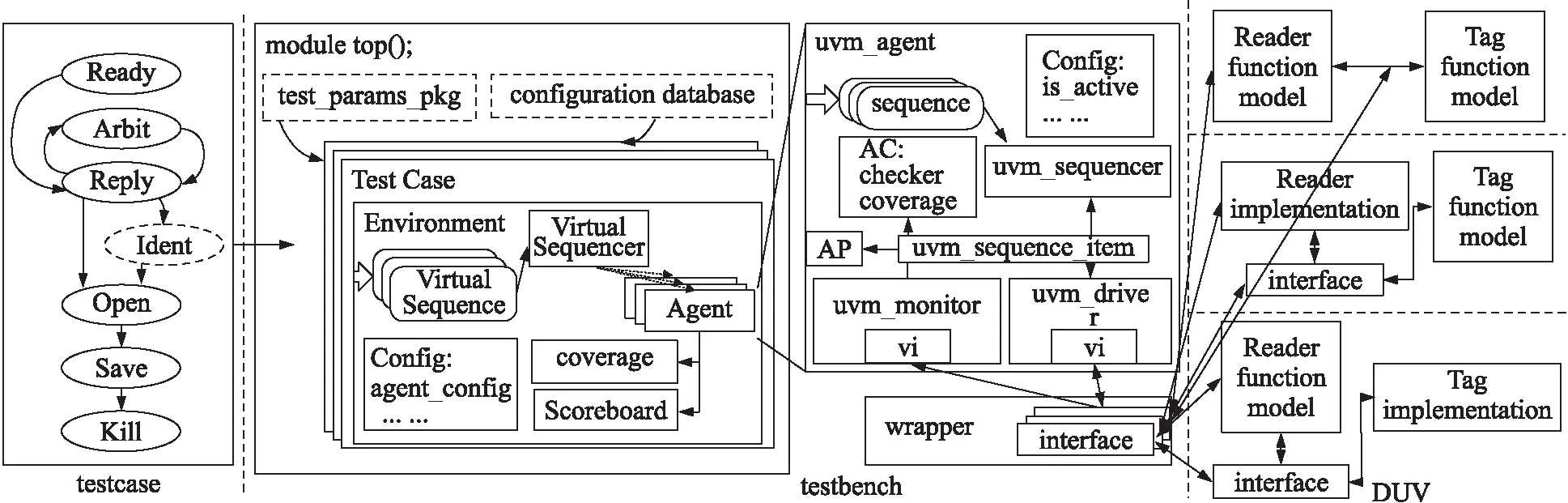

根据协议附录B,可以构建出完整的标签状态机模型,并映射功能模型和覆盖率,如图6所示。流程图模型在防碰撞机制的验证,以及序列图在安全鉴别协议的验证中都有良好的验证辅助效果。验证平台testbench基于UVM方法学及其组件,如图7所示。根据测例层模型产生的testcase,通过调整testbench参数和握手接口,重用在了RFID验证流程对标签的验证、对读写器的验证以及它们内部的模块验证。Wrapper被用在了testbench与实现之间不同的通信需求上,比如取代接口、事务与信号的转换、增加配置阶段等。

图6 状态机模型构建标签状态转换的功能和覆盖率

图7 测例层模型与UVM结合的验证环境

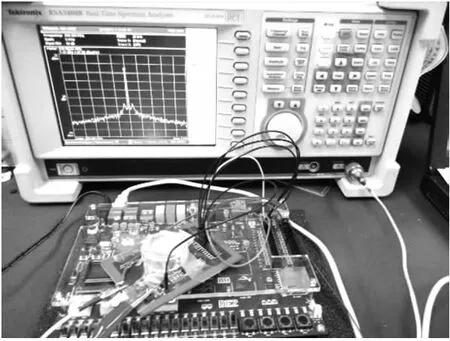

最终通过测例层模型与UVM方法的配合,保证了GJB协议芯片的验证覆盖率,在TSMC0.18μm工艺流片,并测试成功,如图8所示,为该类芯片的进一步改进和相关协议如ISO18000-6C协议芯片的开发积攒了大量可重用验证组件,特别是与testcase层相关的组件。

图8 流片与测试

4 结论与展望

本文通过详细分析功能验证的基本原理,同时基于近年来功能验证在testbench可重用性上的发展情况,以及面向更多纬度上的重用性要求,提出了基于测例层模型的验证。测例层模型是针对testcase层面建立的通用模型,包括类模型、列表模型、流程图模型、状态机图模型、序列图模型等,在实际应用中,根据具体的协议内容进行建模和填充,之后可以用于功能验证的各个阶段,形成了基于协议的测例级VIP。以UVM方法及其组件搭建验证环境架构,将模型内容映射到验证环境中进行功能验证。以可数性、可追溯性的方式诠释功能验证的完整性。并以GJB RFID的设计验证为例进行了说明。本文提出了较为通用的测例层模型,在实际应用中,面向特定结构或需求的验证,比如cache一致性的验证等,仍然可以在测例层探讨更多的模型,以实现更广范围的验证可重用性。

[1] Marella S K,Trivedi A R,Mukhopadhyay S.Optimization of FinFET-Based Circuits Using a Dual Gate Pitch Technique[C]//2015 IEEE/ACM International Conference on Computer-Aided Design(ICCAD),Austin,TX,2015:758-763.

[2] Clevenger L. Technology and Design Architectures and Process Innovations for 7 and 5 nm BEOL Interconnects[C]//2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference(IITC/AMC),San Jose,CA,2016:11-11.

[3] Chitti S,Chandrasekhar P,Asharani M. Ethernet MAC Verification by Efficient Verification Methodology for SOC Performance Improvement[C]//Proceedings of 3rd International Conference on Advanced Computing,Networking and Informatics,ICACNI 2015,Volume 2:117-123.

[4] Drechsler R,Chevallaz C,Fummi F. Panel:Future SoC Verification Methodology:UVM Evolution or Revolution[C]//2014 Design,Automation and Test in Europe Conference and Exhibition(DATE),Dresden,2014:1-5.

[5] Nahtigal T,Puhar P,Žemva A. A Systematic Approach to Configurable Functional Verification of HW IP Blocks at Transaction Level[J]. Computers and Electrical Engineering,2012,38(6):1513-1523.

[6] Rodrigues C L,Silva K R G D,Cunha H N. Enhancing IP Cores Specifications Using Hierarchical Composition and Set Theory[J]. Des Autom Embed Syst,2011,15(3):225-245.

[7] Xie Z,Wang X A,Lian Z B. A Novel Intelligent Verification Platform Based on a Structured Analysis Model[J]. Sci China Inf Sci,2013,56(6):1-14.

[8] Zhar N,Ali M A,Eleuldj M,et al. VIP DESIGN:Graphical Language for Image and Video Processing Embedded Systems Design[C]//2012 International Conference on Complex Systems(ICCS),2012,229(5):1-6.

[9] Huzurbazar A V. Flowgraph Models:A Bayesian Case Study in Construction Engineering[J]. Journal of Statistical Planning and Inference,2005,129(s 1-2):181-193.

[10] Tan A T,Zainol Z,Budiarto R. Flowgraph Models for Estimating Total Time of Authentication Process in RFID System[J]. Journal of the Franklin Institute,2013,350(5):1298-1311.

[11] Li Q P,Xie Z,Su J T. UVM-Based Intelligent Verification Method for UHF RFID Tag[C]//2014 IEEE International Conference on Electron Devices and Solid-State Circuits(EDSSC),Chengdu,2014:1-2.

[12] Xie Z,Wang X A,Lian Z B. A Novel Reuse Technology of Extended Finite State Machine at the Transaction Level Based on UVM[J]. Advances in Electrical and Electronics Engineering,2014:305-314.

AFunctionVerificationMethodBasedontheModelsatTestCaseLevel*

XIEZheng1,WANGMingjiang1*,YONGShanshan2,WANGXin’an2

(1.Shenzhen Graduate School,Harbin Institute of Technology,Shenzhen Guangdong 518055,China;2.Peking University Shenzhen Graduate School,Shenzhen Guangdong 518055,China)

Aiming at the completeness and reusability in the integrated circuit function verification,the models at the test case level are proposed to build a protocol-oriented verification plan with complete functional coverage.The models cooperate with a verification environment built by UVM method and UVM library for an 800/900 MHz RFID system complied with GJB protocol. The models at test case level have generality. The models filled with protocol content meet the reusability between designs complied with the same protocol and the reusability between similar or nonholonomic protocols. That is a protocol-oriented VIP at the test case level and its construction method. Finally the models guarantee the verification coverage of the GJB protocol chip to tape out successfully in TSMC 0.18 μm.

function verification;model at test case level;RFID;UVM

10.3969/j.issn.1005-9490.2017.05.001

项目来源:深圳市科技计划基础研究项目(JCYJ20150403161923540)

2016-08-24修改日期2016-11-21

TN47

A

1005-9490(2017)05-1053-07

谢峥(1985-),男,汉族,山东人,哈尔滨工业大学深圳研究生院博士后,主要研究方向为集成电路设计验证与智能硬件,xiezhengde@126.com;

王明江(1968-),男,汉族,黑龙江人,哈尔滨工业大学深圳研究生院教授,主要研究方向为集成电路与音视频嵌入式系统研究,mjwang@hit.edu.cn。