基于地磁场信号采集电路的Σ-Δ型ADC设计*

2017-11-03刘志文张晓明马喜宏

刘志文,张晓明,马喜宏

(中北大学电子测试国家重点实验室,太原 030051)

基于地磁场信号采集电路的Σ-Δ型ADC设计*

刘志文,张晓明*,马喜宏

(中北大学电子测试国家重点实验室,太原 030051)

为了满足大动态范围、高精度、低噪声地磁数据采集的发展需求,采用一种24位Σ-Δ型ADC7192用于三路数据采集的方法。该方法通过使用可编程增益阵列调理交流放大部分减小了整体电路规模和功耗。针对野外等特殊应用场所引入二次数字(模拟)电源、自校准、满量程校准和ADC内部滤波器,降低其噪声的同时又抑制了50 Hz工频干扰。后期硬件测试对采集数据进行了对比分析,功耗为4.35 mA、测量精度可达70μG的技术指标。

数据采集;Σ-Δ型ADC;模数转换;高精度;低噪声;低功耗

地磁场是地球的基本资源之一,在航空航天、交通通讯、国防建设等领域有着重要的应用。随着科技的飞速发展,磁传感器技术日趋完善,量程和精度都能满足科学研究的要求,但是磁场采集系统容易受测量背景以及测量环境的影响,尤其是高动态范围、高精度、低成本的地磁采集系统成为数据采集的发展方向。现有的采集方案大多存在精度不高、噪声大、电路规模大等问题。本采集电路在众多模数转换器类型中选用Σ-Δ型ADC7192,内置滤波器可消除不同工作环境温度变化和电源电压变化的情况下产生的任何偏移误差,同时也能去除一些低频的噪声。可编程增益阵列替代了调理电路中的交流放大部分减小电路规模的同时减少成本[1]。

1 主要器件选择

本文选用ADI公司的AD7192作为系统的模数转换芯片,其内置可编程增益放大器(PGA)、数字滤波器、时钟振荡电路。片内低噪声增益级,即直接输入小信号,减少了对弱信号放大的电路设计。AD7192芯片具有独立的模拟电源与数字电源[2]。一个5 V的低噪声稳压器用来确保系统获得低噪声模拟电源。此外,在稳压器输出端配有降噪电容。单片机MCU芯片的主要功能是实现对ADC的各项性能控制,最后将模数转换后的数据使用DMA的方式通过串行接口进行输出。

2 数据采集系统设计

本系统设计主要分为硬件设计与软件设计两部分。其中ADC硬件设计主要包括模拟电路部分和ADC的电源与接地组成部分;软件设计包括对ADC控制设计、单片机控制与数据串口传输设计[4]。

模拟电路部分包括信号调理电路和A/D转换电路。信号调理电路位于被测信号和模数转换器之间,被测信号通过差分放大和低通滤波与模数转换器相连。模拟电路每次上电后通过可编程控制对模数转换器进行外部满量程校准和外部零位校准,通过向对应寄存器写入校准字,芯片可以自动完成校准,来消除由于噪声引起的失调误差和增益误差。

为了提高数据采集的高精度要求ADC7192提供4种校准模式:内部零电平校准、内部满量程校准、系统零电平校准和系统满量程校准。失调误差典型值为150μV/增益,当改变增益时执行校准。零电平可将失调误差降至与噪声相当,校准之后,5V时的增益误差典型值为0.001%。

AD7192以伪差分模式采集外部的模拟信号。伪差分输入减小了信号源与设备的参考地电位(地环流)不同所造成的影响,提高了测量的精度[5]。AD7192与STM32之间通过SPI串行通信,从而保证系统能够高速工作。其中本采集系统与传统数据采集优势对比如图1所示。

图1 ADC功能结构图

通过对比可知本采集系统可将传统采集系统的增益放大、工频抑制和噪声抑制都集成到Σ-Δ型ADC中,减少了系统的整体电路规模、功耗和成本,同时又保持了低噪声、高精度、大动态范围的性能特点。

3 高精度多路采集系统的分析

3.1 ADC标定

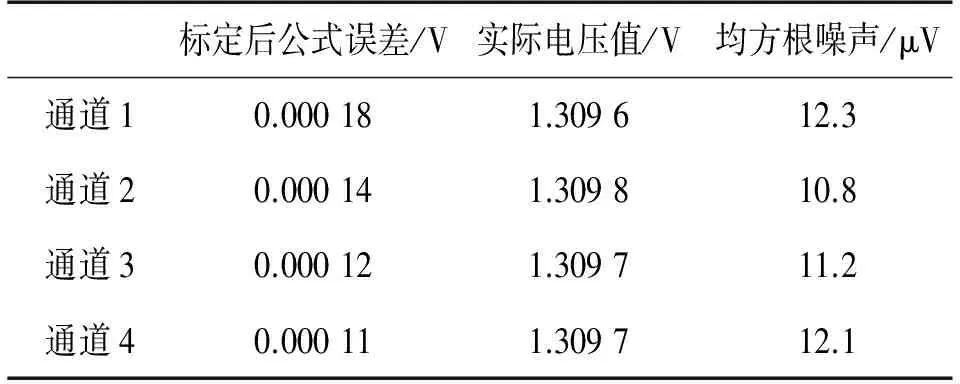

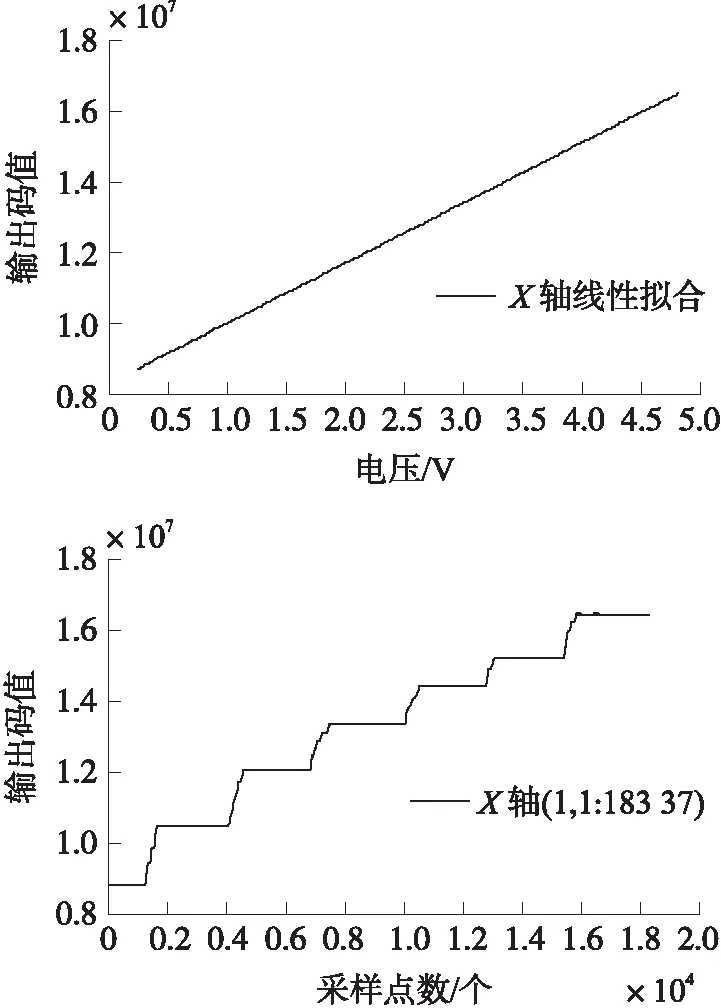

由于每个高精度ADC的制造工艺略有差异,当数据解码采用官方公式时会产生一定的误差,所以本设计采用重新标定的方式对ADC模拟量进行解算。具体通道的标定方法为利用平均值与电压值一一对应的关系对它们进行二次拟合,可得线性方程如下:

f(x)=p1x+p2

(1)

式中:p1=1.72×106,p2=8.33×106

对应关系图如图2所示。

图2

根据最小二乘法拟合出的线性方程,对输出进行解码,同时对比实际均方根噪声与官方均方根噪声[7]。数据对比如表1所示。

表1 数据对比

图3为输出数据时的噪声分布,这相当于22.5位有效分辨率或20位无噪声分辨率。

图3 噪声分布直方图

通过对ADC进行重新标定提高了采集系统精度,均方根噪声低于官方数据16.5 μV。且经过系统校准后,失调误差与选定的编程增益和输出数据速率所对应的噪声相当[8]。由此可得此系统可实现低噪声、多通道、高精度数据采集。

3.2 50 Hz工频干扰抑制

地磁场采集时是以高分辨率ADC测量大动态范围电平信号,如果测量装置工作在电源变压器或输电线路附近交流电干扰会带来严重问题,同时来自无屏蔽电缆或电气设备的辐射,该频率也会对电信号产生干扰,许多数据采集系统需要抑制其干扰。为避免使用低通模拟滤波器造成的高阶模拟滤波器从组件数量和电路板空间成本增加,截止频率容易发生漂移的问题,

本文中使用数字滤波器,这种滤波器可针对线路频率下的抑制进行优化,设备无需重新配置便可进行广泛使用[9]。正确配置后该内置滤波器可以有效抑制电力线路频率,同时仍保留足够带宽测量输入信号。SINC3滤波器的频率响应为:

ADC输出数据速率为:

fS=fCLK/(3×1 024×FS[9:0])

SINC3滤波器的建立时间更短,因此是用于低噪声调制器时是追求转换速度的绝佳选择,图4中显示的是SF=96(十进制)的频率响应曲线图,改变模式寄存器中REJ60为0,频率响应如图4所示。

图4 频率响应图

实际开发验证中输入信号收到工频干扰表现为50 Hz、100 Hz和150 Hz,即干扰幅度值较大为50 Hz和其倍频时产生,此时SINC3滤波器就能让某个梳齿对准50 Hz、100 Hz和150 Hz,抑制性能达到100 dB以上,从而提高了采集系统的抗干扰能力。

3.3 PGA增益级

AD7192中的缓冲器使能时,输入通道会驱动缓冲放大器的高阻抗输入级,此模式的绝对输入电压范围限制在AVDD +250 mV至AVDD -250 mV。增益级使能后,缓冲器输出将施加于PGA输入端。为了充分利用此ADC的大动态范围,系统按表2所示对信号进行自动放大。

PGA的存在意味着小幅度的地磁场信号可以自动在AD7192内被放大,同时此ADC可使能CHOP模式用来去除ADC的偏移误差,包括在温度变化情况下和电源电压变化的情况下产生的任何偏移误差,同时也能去除一些低频的噪声[10]。

通过对信号的自动放大,此系统的大动态范围可满足三维地磁场采集的发展需求。

表2 增益配置

4 实验数据验证

由于线性磁阻传感器的灵敏度高、适应频率和动态范围高,所以本地磁采集系统采用三维磁阻混合电路模块HMC2003,该芯片内部集成灵敏度温度补偿,具有良好的温度稳定性和电磁兼容性,适用于多种测试环境。其整个系统实物如图5所示,并给出了电路原理图。

图5

4.1 系统噪声验证

将系统置于磁屏蔽筒中,无矩线圈不施加电路,其筒内近似认为是“零磁场”空间,此时测得磁阻传感器的偏置电流对应的磁场。使用采集系统对磁传感器三轴输出数据进行求标准差的手段获得噪声的平均水平。对应三轴零磁场数据如图6所示。

图6中给出采集系统在零磁场的情况下测得的磁阻传感器输出,其为将三轴的直流分量补偿后磁阻传感器的噪声情况,噪声值都小于5 nT,优于常规的采集系统,达到了低噪声的设计要求。

图6 三轴噪声

4.2 非线性度验证

图7 采集系统输出

给采集系统加载0 V~5 V的电压值,对应的磁场值为-2 Gauss~2 Gauss,计数7个点,间隔一定的电压值,实时记录X轴向磁阻传感器输出,将在MATLAB中数据按最小二乘法直线拟合,得到拟合方程y=kx+b,某一点x值代入曲线得到y1值,则交叉拟合为N=|y-y1|max,在前面计算所得量程yF,则非线性误差ξL=(N/yF)×100%计算可以对比出非线性度[11]。对应电压梯度时的数据采集与对应线性拟合如图7所示。

N为最小二乘法拟合残差,三轴分别对应为10.340 mV、7.335 mV、3.745 mV由此可得三轴非线性误差分别为0.21%、0.15%、0.074%优于常规采集系统的非线性度。

4.3 地磁场采集验证

为验证ADC采集地磁场时的性能,对应采集当地静止地磁场三分量值。图8为HMC2003磁传感器经过消噪后的三轴输出。

地磁采集系统应用于不同环境可能出现大翻转的情况,因此有必要将采集系统置于转台以一定角速度旋转的情况下,测量系统输出的动态性能。图9为旋转时系统输出。

图8 静采时三轴输出

图9 旋转时三轴输出

由图9可得旋转时X、Y轴的磁场输出值呈三角函数变化,与理论值相符。由此可得采集系统具有良好的动态性能。

5 结论

本文是对大动态范围、高精度、低噪声地磁数据进行高精度、多通道同步数据采集系统的研究,介绍了系统的主要功能需求以及系统相应芯片的选择与特点,给出了硬件中采集、通信、传输以及必要的外围电路,并对其硬件功能进行了分析与测试,能够达到高精度、多通道、稳定的数据采集,同时通过可编程控制对其增益、输出速率、内部滤波器等参数进行实时配置,为降低功耗该系统均采用掉电工作模式,在不需要数据采集时处于睡眠模式,中断唤醒后进入全速工作模式,功耗仅为4.35 mA,测量精度可达70μG达到设计要求。本设计为不同应用场所下地磁场数据采集系统的进一步发展提供一定的借鉴。

[1] 宋华军,朱明,沈美丽. 高精度数据采集仪的实现与研究[J]. 电子器件,2007,30(1):93-96.

[2] ADI.AD7192DataSheet[EB/OL]. [2016-05-01]. http//www.AnalogDeviceslnc.com.

[3] 李多,叶桦. 基于STM32与FPC1011F的嵌入式指纹采集存储仪设计[J]. 电子器件,2015(2):362-367.

[4] 王静宜.多通道大容量高速数据存储系统设计[D]. 中北大学,2014,4(5):124-128.

[5] 朱欣华,夏云翔,万德钧. 分布式捷联姿态基准中数据采集系统的设计[J]. 传感技术学报,2006,19(3):741-745.

[6] 郭熙宝,曹大平. 24位高精度磁传感器数据采集系统的设计[J]. 电子技术应用,2014,35(5):56-60.

[7] 郑永秋,史赟,李圣昆.多通道高精度数据采集电路的设计与实践[J]. 电测与仪表,2011,48(9):86-89.

[8] BAKER B. ∑-Δ ADC工作原理[EB/OL]. [2016-05-01]. http//wenku.baidu.com/view/644870ccalc7aa00b52acb3f.html.

[9] 杜兵团,李斌.基于AD7738的高精度、多通道数据采集系统设计研究[J]. 电声技术,2007,31(7):128-132.

[10] 马忠梅,籍顺心,张凯.单片机的C语言应用程序设计[M]. 北京:北京航空航天大学出版社,1999:74-120.

[11] OTT H W.电子系统中噪声的抑制与衰减技术[M]. 王培清,李迪译.北京:电子工业出版社,2004:126-138.

FortheMagneticSignalAcquisitionCircuitofaSigma-DeltaADCDesign*

LIUZhiwen,ZHANGXiaoming*,MAXihong

(National Key laboratory for Electronic Measure Technology,Taiyuan 030051,China)

In order to meet the development requirements of large dynamic range,high precision and low noise data acquisition,a 24-bit sigma-delta ADC7192 is used for three-way data acquisition. The method by using the programmable gain array regulate AC amplifying section reduces the overall size and power consumption. For special applications like wild places introduced second digital analog power,self-calibration,full-scale calibration and ADC internal filter,its noise was reduced and the 50 Hz frequency interference was suppressed. The latter part of the hardware test on the collected data was analyzed and the power consumption obtained is 4.35 mA,measurement precision can reach 70 μG for the technical indicators.

data collection;sigma-delta ADC;analog to digital conversion;high precision;low noise;low power consumption

10.3969/j.issn.1005-9490.2017.05.018

项目来源:国家自然科学基金项目(51375463)

2016-08-23修改日期2016-10-20

TP274

A

1005-9490(2017)05-1140-05

刘志文(1988-),男,硕士研究生,山西,主要研究方向为硬件电路设计,282838495@qq.com;

张晓明(1976-),男,副教授,山西,主要研究方向为动态测试及组合导航,zxm_auto@nuc.edu.cn。