埋氧离子注入对P型部分耗尽SOI电学与低频噪声的影响

2017-10-24陈海波吴建伟恩云飞

陈海波,刘 远,吴建伟,恩云飞

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.工业和信息化部电子第五研究所电子元器件可靠性物理及其应用技术国家重点实验室,广州510610;3.华南理工大学微电子学院,广州510640)

埋氧离子注入对P型部分耗尽SOI电学与低频噪声的影响

陈海波1,刘 远2,3,吴建伟1,恩云飞2

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.工业和信息化部电子第五研究所电子元器件可靠性物理及其应用技术国家重点实验室,广州510610;3.华南理工大学微电子学院,广州510640)

针对抗辐照SOIPMOS器件的直流特性与低频噪声特性展开试验与理论研究,分析离子注入工艺对PMOS器件电学性能的影响,并预测其稳定性的变化。首先,对离子注入前后PMOS器件的阈值电压、迁移率和亚阈摆幅进行提取。测量结果表明:埋氧化层离子注入后,器件背栅阈值电压由-43.39 V变为-39.2 V,空穴有效迁移率由127.37 cm2/Vs降低为80.45 cm2/Vs,亚阈摆幅由1.35 V/dec增长为1.69 V/dec;结合背栅阈值电压与亚阈摆幅的变化,提取得到埋氧化层内电子陷阱与背栅界面态数量的变化。随后,分析器件沟道电流噪声功率谱密度随频率、沟道电流的变化,提取γ因子与平带电压噪声功率谱密度,由此计算得到背栅界面附近的缺陷态密度。基于电荷隧穿机制,提取离子注入前后埋氧化层内陷阱态随空间分布的变化。最后,基于迁移率随机涨落机制,提取得到离子注入前后PMOS器件的平均霍格因子由6.19×10-5增长为2.07×10-2,这表明离子注入后器件背栅界面本征电性能与应力稳定性将变差。

绝缘体上硅;部分耗尽;低频噪声;离子注入

1 引言

SOICMOS器件具有功耗低、集成度高、抗单粒子效应强等优点,并彻底消除了体硅CMOS器件中所呈现的寄生闩锁等效应,因而在太空等极端环境中得到广泛应用[1]。由于SOICMOS器件埋氧化层较厚,其抗总剂量电离辐照能力较差;电离辐照在SOICMOS器件埋氧化层中将诱生固定电荷,这将使其背栅阈值电压漂移,并进而影响电路和系统的正常工作[2]。

为提升SOICMOS器件的抗总剂量辐照性能,业界常采用埋氧化层离子注入等方法[3~5],通过增加电子陷阱的形式对辐照诱生固定正电荷进行补偿,由此减少器件的背栅阈值电压漂移量。据文献[4]、[5]报道,Mrstik等通过采用Al、Si、P等离子对埋氧化层进行注入,已成功提升器件的抗辐照性能。

在埋氧化层离子注入过程中,注入离子不可避免地将对Si-SiO2界面造成一定损伤;此外,在埋氧化层中加入电子陷阱对器件本征性能与可靠性也将造成一定影响[6~8];Xiong H D 等的试验结果[7~8]表明:采用埋氧化层离子注入后的器件,其在长时间电应力下电学稳定性明显变差。因而,有必要选择合适的离子注量,在器件抗辐照性能、本征性能与可靠性之间进行一定折中,同时兼顾空间抗辐照能力与电路稳定工作两方面的需求。

本文针对埋氧化层离子注入前后部分耗尽SOI PMOS器件电学性能的变化展开试验与理论研究,分析离子注入对器件前栅与背栅界面性能、直流特性与低频噪声特性的影响。基于低频噪声的分析与参数提取结果,计算平带电压噪声功率谱密度,并进而获得界面附近的陷阱态密度;基于电荷隧穿机制,计算埋氧化层内陷阱态的空间分布;基于迁移率随机涨落机制,计算Hooge因子,定性分析器件的工艺质量并预测其可靠性。

2 器件结构参数与直流特性

2.1 器件结构参数

本文所用样品为部分耗尽结构SOIPMOS器件,器件结构如图1所示;其中前栅氧化层厚度tox为17.5 nm,埋氧化层厚度tbox为375 nm,有源层硅膜厚度tsi为205 nm;可计算得到器件前栅单位面积氧化层电容Cox为1.97×10-7F/cm2,埋氧化层单位面积电容Cbox为9.2×10-9F/cm2。试验所用器件宽长比(W/L)为 8μm/1.6μm。

在器件制备过程中,拟采用三种离子注量对器件埋氧化层进行离子注入,以增加埋氧化层内的电子陷阱数量。未经受离子注入处理的器件在后文中将被命名为芯片A;而受到离子注入处理的器件则分别命名为芯片B、芯片C和芯片D。其中,芯片B中所受离子注入的注量最低,而样品D中所受离子注入的注量最高。下文将对芯片A至芯片D的直流特性与低频噪声特性进行测量与计算,定量分析离子注入前后样品质量的变化。

2.2 器件直流特性

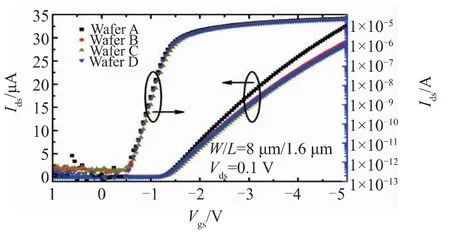

本节针对上述四款芯片(芯片A至芯片D),分别对其前栅、背栅转移特性曲线进行测量,结果如图2、3所示。

图1 部分耗尽SOIPMOS器件结构示意图

由图2可知,埋氧化层离子注入对器件前栅电学特性影响较少,芯片A至芯片D的前栅转移特性曲线较相似。其中,芯片A的前栅阈值电压(Vfg)约为-1.17 V,前表面空穴有效迁移率(μeff)约为98 cm2/Vs,前栅亚阈摆幅(SS)约为 0.115 V/dec。

由图3可知,离子注入对SOIPMOS器件背栅转移特性曲线影响较大。随着离子注量的增加,埋氧化层内电子陷阱数量随之变大,这使得背栅阈值电压向正方向漂移,绝对值减小。经参数提取,芯片A至芯片D的背栅阈值电压(Vfb)分别为-43.39 V、-40.25 V、-40.06 V与-39.2 V;背界面空穴有效迁移率分别为127.37 cm2/Vs、109.47 cm2/Vs、102.5 cm2/Vs、80.45 cm2/Vs;背栅亚阈摆幅分别为 1.353 V/dec、1.367 V/dec、1.691 V/dec、1.687 V/dec。分析上述数据可知,在埋氧化层离子注入后,随着离子注量的增加,背栅界面处缺陷密度增加,这使得空穴有效迁移率降低、亚阈摆幅变大,器件背栅界面处本征电学性能随之退化。

器件亚阈摆幅的变化(ΔSS)直接反应出离子注入处理前后器件背栅界面处界面态的变化;由文献可知,器件亚阈摆幅与界面态(Dit)之间关系为[9]:

式中,K为波尔兹曼参数、T为环境温度。由式(1)可分别提取得到离子注入在芯片B至芯片D中所诱生的界面态密度分别为1.35×1010cm-2eV-1,3.25×1011cm-2eV-1和 3.21×1011cm-2eV-1。由于 PMOS 器件的体电势(φp)约为0.38 eV,因而离子注入在芯片B至芯片D中所诱生的界面态数量(ΔNit=φpΔDit)[10~11]分别为0.51×1010cm-2,1.24×1011cm-2和 1.22×1011cm-2。

器件背栅阈值电压的变化通常由界面态和埋氧化层内电子陷阱所决定[12]:

基于器件背栅阈值电压与背栅界面态的变化量,可计算得到离子注入在芯片B至芯片D内引入的电子陷阱数量(ΔNbox)分别为 1.86×1011cm-2、3.15×1011cm-2和4.63×1011cm-2,这与样品离子注入处理过程中离子注量的变化趋势相吻合。

3 器件低频噪声特性与分析

噪声来源于物理量的随机起伏。半导体器件中的低频噪声主要包括热噪声、散粒噪声、产生-复合噪声(G-R噪声)与闪烁噪声(1/f噪声)。1/f噪声与G-R噪声的功率谱密度与频率有关,在低频情况下较为显著,故统称为低频噪声。由于1/f噪声由器件表面缺陷及氧化层陷阱电荷所引起,因而往往能反映器件内在质量和可靠性的优劣[1,12]。本节将针对SOIPMOS器件噪声特性、缺陷态与离子注量的相关性展开测量与分析。

3.1 低频噪声测量系统

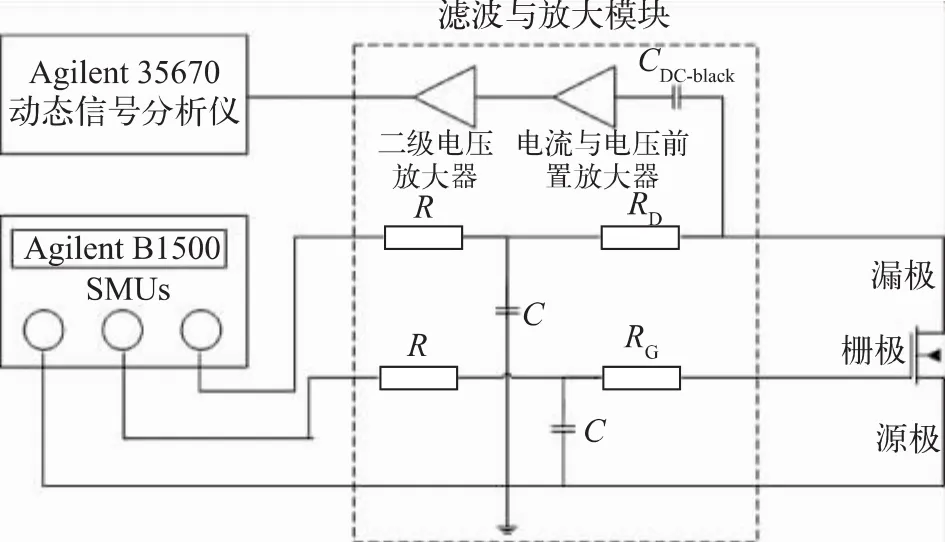

SOIPMOS器件低频噪声测量系统如图4所示。系统采用半导体参数测试仪AgilentB1500的SMU单元监控器件电学参数的变化,采用Agilent35670频谱分析仪测量器件沟道电流的噪声功率谱密度,采用AgilentE4727A构建噪声测量系统的滤波与低频噪声放大单元。为使得被测器件与低频噪声放大单元相匹配,需在器件栅极与漏极串联相应电阻RG与RD;由于器件栅极电阻较大,因而RG被设置为0Ω,RD则根据外界偏置情况选用33 kΩ或100 kΩ。

3.2 低频噪声特性

图2 部分耗尽SOIPMOS器件的前栅转移特性曲线

图3 部分耗尽SOIPMOS器件的背栅转移特性曲线

图4 SOIPMOS器件的低频噪声测量系统[1,12]

基于上述低频噪声测量系统,可对四款SOI PMOS器件中前栅、背栅工作条件下低频噪声特性进行测量与分析。在Vfg-Vtf=-3.7 V和Vds=-0.5 V条件下,所测量得到器件前栅低频噪声特性曲线(归一化电流噪声功率谱密度SID/ID2随频率f的变化)如图5所示;在Vbg-Vtb=-6 V和Vds=-0.5 V的条件下,所测量得到器件背栅低频噪声特性曲线如图6所示。

由图5可知,离子注入前后SOIPMOS器件前栅低频噪声特性曲线较相似,这再次说明离子注入对SOIPMOS前栅工作参数与电学特性影响较小。器件前栅低频噪声特性曲线呈1/fγ的变化趋势,其中γ约为1.12;这主要由前栅界面附近缺陷态捕获和释放载流子效应所决定。由文献[13]可知,γ因子反映了界面附近缺陷态的纵向分布;如果γ<1,则有源层内缺陷态密度将大于氧化层内陷阱密度;如果γ>1,则有源层内缺陷态密度将小于氧化层内陷阱密度。基于γ因子,可知SOIPMOS器件栅氧化层内缺陷态密度较多。

图6四类PMOS器件中背栅的低频噪声特性曲线

由图6可知,离子注入对SOIPMOS器件背栅低频噪声特性曲线影响较大;随着离子注量的增加,器件背栅噪声功率谱密度随之变大,这表明器件质量与电学特性变差。在四款芯片中,器件背栅低频噪声特性曲线仍呈1/fγ的变化趋势,但γ因子随离子注量的增加而变大,分别为1.13、1.33、1.29和1.44。由上文可知,γ因子体现出埋氧化层内电子陷阱的变化;随着离子注入后埋氧化层内电子陷阱的增加,γ因子呈变大趋势。

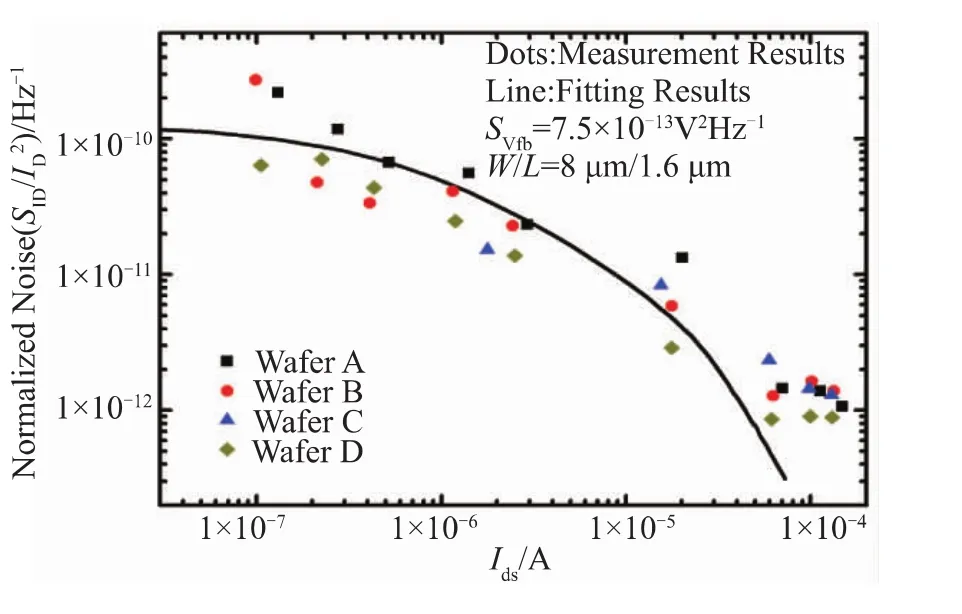

为进一步研究离子注入对SOIPMOS器件低频噪声的影响,器件归一化电流噪声功率谱密度SID/ID2随沟道电流ID的变化如图7、8所示。

基于传统的电子隧穿理论,归一化电流噪声功率谱密度与平带电压噪声功率谱密度(Svfb)之间的关系可表征为[9,12]:

式(3)中,gm为器件跨导。假定氧化层内陷阱态在能带中呈均匀分布,陷阱态密度与平带电压噪声功率谱密度之间关系为[12,14]:

式(4)中,Nt为氧化层内陷阱态密度(cm-3eV-1);λ为隧穿衰变距离,其值在SiO2中通常为0.1 nm。

基于式(3),可由图7所示低频噪声曲线中提取得到PMOS器件前栅平带电压噪声功率谱密度,其值约为7.5×10-13V2Hz-1。因而,器件前栅氧化层内陷阱态密度约为 1.39×1016cm-3eV-1。

此外,四款SOIPMOS器件背栅平带电压噪声功率谱密度亦可通过式(3)求解得到,其值(芯片A~D)分别为 7×10-10V2Hz-1、9×10-9V2Hz-1、1.7×10-8V2Hz-1和4.6×10-8V2Hz-1。因而,离子注入前后芯片A~D中埋氧化层内陷阱态密度分别约为2.85×1016cm-3eV-1、3.66×1017cm-3eV-1、6.92×1017cm-3eV-1和 1.87×1018cm-3eV-1,这些结果与上文中基于直流特性所提取得到埋氧化层内电子陷阱数量的变化趋势相吻合。

基于电荷隧穿机制,沟道反型层内电荷与埋氧化层内陷阱电荷的交互将主导SOI器件的低频噪声。由于电荷在氧化层内的隧穿距离受时间常数τ的影响,而τ=1/(2πf),因而电荷在埋氧化层内的隧穿距离与频率之间的关系为[12,15]:

图5 四类PMOS器件中前栅的低频噪声特性曲线

图7 四款PMOS器件中前栅归一化电流噪声功率谱密度随沟道电流的变化

式(5)中,τ0为氧化层界面附近电荷隧穿(小于5 nm)的时间常数,通常为10-10s;而x为陷阱电荷距二氧化硅-硅界面的距离(深度)。由式(5)可知,电荷的隧穿能力与其距界面的距离呈E指数减小。

图8 四款PMOS器件中背栅归一化电流噪声功率谱密度随沟道电流的变化

基于式(5),并结合器件低频噪声测量曲线,可提取得到离子注入前后埋氧化层内电子陷阱密度随空间的变化。由图9可知,电子陷阱密度将随离子注量的增加而增加,芯片A中埋氧化层内陷阱态密度仅为芯片D中埋氧化层陷阱态密度的百分之一。

图9 四款SOIPMOS器件中埋氧化层内陷阱态密度的空间分布

在传统MOS器件低频噪声模型中,Hooge的试验结果表明,PMOS器件低频噪声特性将更依赖于有源层内迁移率的随机涨落。在考虑迁移率随机涨落机制与模型的基础上,可提取Hooge经验因子,由此评估PMOS器件及其本征性能的优劣,并预测器件的电学稳定性。基于Hooge经验模型,器件噪声功率谱密度可表征为[16]:

式(6)中,αH为Hooge因子,可用于区分不同器件与材料低频噪声的大小。

基于式(6),由图9中可估算四类器件的平均Hooge 因子 αH分别为 6.19×10-5、1.28×10-3、1.55×10-3和 2.07×10-2,如图 10 所示。

由文献[17]可知,在 MOSFET 中,αH介于 10-6至10-4之间。由图10可见,芯片D的αH较芯片A大334倍,因而其背栅界面的本征电学性能与稳定性较芯片A会差许多;在经受同等外部应力的条件下,芯片D的电学稳定性也将较芯片A差许多。

图10 四款SOIPMOS器件背栅界面的Hooge因子

4 结论

本文针对抗辐照SOI PMOS器件的直流特性与低频噪声特性展开试验与理论研究。首先,针对离子注入前后器件的直流特性进行测量与分析;基于亚阈摆幅,提取离子注入前后器件背栅界面态的变化;结合背栅阈值电压的变化,定量分析离子注入在埋氧化层内引入的电子陷阱密度。随后,基于低频噪声测量与分析,提取γ因子与平带电压噪声功率谱密度,提取界面附近的缺陷态密度;结合电荷隧穿机制,提取埋氧化层内陷阱态随空间的分布。最后,结合迁移率随机涨落机制,提取霍格因子,定量评价离子注入前后器件工艺的差异性,并预测其质量与电学稳定性。

[1]Wang K,Liu Y,Chen H B,et al.Low frequency noise behaviors in the partially depleted silicon-on-insulator device[J].Acta Phys.Sin.2015,64(10):108501.王凯,刘远,陈海波,等.部分耗尽结构绝缘体上硅器件的低频噪声特性[J].物理学报,2015,64(10):108501.

[2]Schwank J R,Shaneyfelt M R,Fleetwood D M,et al.Radiation effects in MOS oxides[J].IEEE Trans.Nucl.Sci.2008,55(4):1833-1853.

[3]Nazarov A N,Gebal T,Rebohle L,et al.Trapping of negative and positive charges in Ge+ion implanted silicon dioxide layers subjected to high-field electron injection[J].J.Appl.Phys,2003,94(7):4440-4448.

[4]Mrstik B J,Hughes H L,McMarr P J,et al.Hole and electron trapping in ion implanted thermal oxides and SIMOX[J].IEEE Trans.Nucl.Sci.2000,47(6):2189-2195.

[5]Mrstik B J,Hughes H L,McMarr P J,et al.Electron and hole trapping in thermal oxides that have been ion implanted[J].Microelectron.Eng.2001,59(1-4):285-289.

[6]Schwank J R,Fleetwood D M,Xiong H D,etal.Generation of metastable electron traps in the near interfacial region of SOI buried oxides by ion implantation and their effect on device properties[J].Microelectron.Eng.2004,72(1-4):362-366.

[7]Xiong H D,Jun B,Fleetwood D M,et al.Charge trapping and low frequency noise in SOI buried oxides[J].IEEE Trans.Nucl.Sci.2004,51(6):3238-3242.

[8]Xiong H D,Fleetwood D M,Schwank J R.Low-frequency noise and radiation response of buried oxides in SOI nMOS transistors[J].IEEE Proc.Circuits Devices Syst,2004,151(2):118-124.

[9]Liu Y,Wu WJ,En Y F,et al.Total Dose Ionizing Radiation Effects in the Indium-Zinc Oxide Thin-Film Transistors[J].IEEE Electron.Dev.Lett,2014,35(3):369-371.

[10]Schwank J R,Fleetwood D M,Shaneyfelt M R,et al.A critical comparison of charge-pumping,dual-transistor,and midgap measurement techniques (MOS transistors)[J].IEEE Trans.Nucl.Sci,1993,40(6):1666-1677.

[11]Fleetwood D M,Shaneyfelt M R,Schwank J R.Estimating oxide-trap,interface-trap,and border-trap charge densities in metal-oxide-semiconductor transistors[J].Appl.Phys.Lett,1994,64(15):1965-1967.

[12]Liu Y,Chen H B,Liu Y R,etal.Low frequency noise and radiation response in the partially depleted SOIMOSFETs with ion implanted buried oxide[J].Chin.Phys.B,2015,24(8):088503.

[13]Jayaraman R,Sodini C G.A 1/f noise technique to extract the oxide trap density near the conduction band edge of silicon[J].IEEE Trans.Electron.Dev.1989,36(9):1773-1782.

[14]Ioannidis E G,Tsormpatzoglou A,Tassis D H,et al.Characterization of traps in the gate dielectric of amorphous and nanocrystalline silicon thin-film transistors by 1/fnoise[J].J.Appl.Phys,2010,108(10):106103.

[15]Tsormpatzoglou A,Hastas N A,Mahmoudabadi F,et al.Characterization of High-Current Stress-Induced Instability in Amorphous InGaZnO Thin-Film Transistors by Low-Frequency Noise Measurements[J].IEEE Electron.Dev.Lett,2013,34(11):1403-1405.

[16]Hooge F N.1/fnoise sources[J].IEEE Trans.Electron.Dev,1994,41(11):1926-1935.

[17]Vandamme L K J,Hooge F N.What Do We Certainly Know About 1/f Noise in MOSTs?[J].IEEE Trans.Electron.Dev,2008,55(11):3070-3085.

Dependence of Ion Implantation on the Electrical Characteristics and Low Frequency Noise in the P-Type PD-SOI Devices

CHEN Haibo1,LIU Yuan2,3,WU Jianwei1,EN Yunfei2

(1.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi214072,China;2.Science and Technology on Reliability Physics and Application of Electronic Component Laboratory,CEPREI,Guangzhou 510610,China;3.School of Microelectronics,South China University of Technology,Guangzhou 510640,China)

Electrical characteristics and low frequency noise of radiation harden partially depleted siliconon-insulator(PD-SOI)p-channel devices are discussed in the paper.The dependence of ion implantation on the electrical performance in the PMOS is studied.Firstly,threshold voltage,hole field effect mobility and sub-threshold swing are extracted.As ion implantation induces electron traps in the buried oxide and back interface states,back gate threshold voltage increases from-43.39 V to-39.2 V and hole field effect mobility decreases from 127.37 cm2/Vs to 80.45 cm2/Vs,while sub-threshold swing increases from 1.35 V/dec to 1.69 V/dec.Based on the variation of back gate threshold voltage and sub-threshold swing,the concentration ofelectron traps in the buried oxide and back interface states are estimated.Subsequently,low frequency noise characteristics are measured.The value of γ and flat-band voltage noise powerspectral densities in the PD-SOI devices with and without ion implantation are extracted,thus the average trap density in the buried oxide are calculated.Based on charge tunneling mechanism,the spatial distribution of electron traps in the buried oxide is extracted.At last,based on mobility fluctuation mechanism,the average Hooge's parameters are extracted which increase from 6.19×10-5to 2.07×10-2,indicating that the intrinsic electronic performances and stress inst abilities are degenerated after ion implantation.

Silicon on insulator;partially depleted;low frequency noise;ion implantation

TN305.3

A

1681-1070(2017)10-0036-06

2017-5-30

陈海波(1986—),男,河南商丘人,硕士,毕业于西北工业大学材料学专业,主要从事半导体集成电路工艺和器件可靠性研究。