基于Lutz模型的无线信道仿真器的FPGA实现

2017-10-20郭黎利刘麒麟

郭黎利,刘麒麟

(哈尔滨工程大学 信息与通信工程学院,黑龙江 哈尔滨 150001)

基于Lutz模型的无线信道仿真器的FPGA实现

郭黎利,刘麒麟

(哈尔滨工程大学 信息与通信工程学院,黑龙江 哈尔滨 150001)

无线信道仿真器,是对真实信道环境的拟合,可以提高通信系统的研发和测试效率,具有很强的现实意义。Lutz模型是一种非稳态信道,能够在良好信道状态和不良信道状态之间进行切换,并有效描述信道的变化特征。设计了一种基于Lutz模型的频率选择性信道,在FPGA中采用分模块进行实现,然后使用Modelsim和Maltab等工具进行验证,仿真结果表明无线信道仿真器的FPGA实现,满足信道特征的统计特性,可直接用来测试无线通信系统。

无线信道仿真器;Lutz模型;FPGA

0 引言

在无线通信系统中,无线信道作为信号传输媒介占据重要的一环。因此,对无线信道模型的研究,人们做了大量的工作。建立最优的、最拟合实际信道环境的模型,以及在此模型基础上实现的信道仿真器,是无线通信系统研发中比较重要的一部分[1]。专业的信道仿真器,由于价格昂贵,并且灵活性不够,掣肘着通信系统研发的效率。FPGA相比专业的信道仿真器,价格低廉,并且可以用编程语言,对内部资源灵活设置,因此,使用FPGA来仿真信道模型,是实现信道模拟器的一个最优选择[2]。

对于无线通信来说,单一某个信道模型是无法准确描述实际信道状态的。Lutz模型是一种非稳态信道,它可以在良好信道状态和不良信道状态之间进行切换[3]。本文设计了一种基于Lutz模型的频率选择性信道,在FPGA中采用分模块进行实现。

1 系统结构概述

本设计选用Xilinx公司出品的Virtex-5系列的XC5VSX95T芯片[4],总体实现框图如图1所示。图1实现了一种频率选择性信道,它是基于Lutz信道设计的。在图1中,首先由信号发生器产生30 MHz中频信号,经过AD芯片转换为数字信号,然后对其进行下变频,此时信号为数字基带信号,然后将该数字基带信号分两路,分别经过不同的延时之后,一路信号跟Lutz动态信道相乘,另一路跟高斯多普勒信道相乘,接着将两路信号相加,然后经过上变频、DA转换,再次成为了模拟中频信号,最后输出到示波器观察波形。

如图1所示,大部分模块将由FPGA来实现。AD和DA部分分别由ADI公司的ad6455和ad9777芯片来完成。本文采用模块化设计来实现仿真器的设计。

图1 信道仿真器的总体实现框图

2 Lutz信道的实现

Lutz模型提出了在存在视距分量的区域(良好的信道状态)和视距分量被遮挡的区域(不良的信道状态)之间进行切换。该切换是由一个两状态马尔可夫链控制的。在Lutz模型中,如果处于良好信道状态,则信号的衰落由瑞利过程描述。否则处于不良信道状态,则信号的衰落由Suzuki过程描述。

2.1 瑞利过程的实现

本文的瑞利过程,采用的是经典的Jakes模型[5-6]。

在FPGA中实现该Jakes模型,需要产生均匀随机数,还有余弦和正弦函数。余弦和正弦函数,可以采用直接数字频率合成法(Direct Digital Synthesis,DDS)算法产生[7],均匀随机数由m序列来实现[8]。

分别用Modelsim仿真Jakes模型的同向分量和正交分量,如图2所示。可将该图与MATLAB仿真曲线比较,进而来证明本次Jakes信道的硬件实现基本符合要求。

图2 Jakes模型的仿真

2.2 Suzuki过程的实现

Suzuki信道是在瑞利信道的基础上考虑阴影效应,即瑞利信道的平均功率呈对数正态分布,所以它的信道冲激响应,是瑞利信道乘以对数正态过程。本节来完成Suzuki信道的硬件实现。上节已经实现了瑞利信道,因而下文来完成对数正态过程的硬件实现。

实现对数正态过程,需要先分别实现高斯分布和指数函数。

2.2.1 高斯分布的实现

在硬件中均匀分布是容易实现的,而高斯分布不太容易直接实现。所以本文采用Box-Muller 算法来产生高斯噪声[9],它具有实现复杂度低、精确性高等特点。

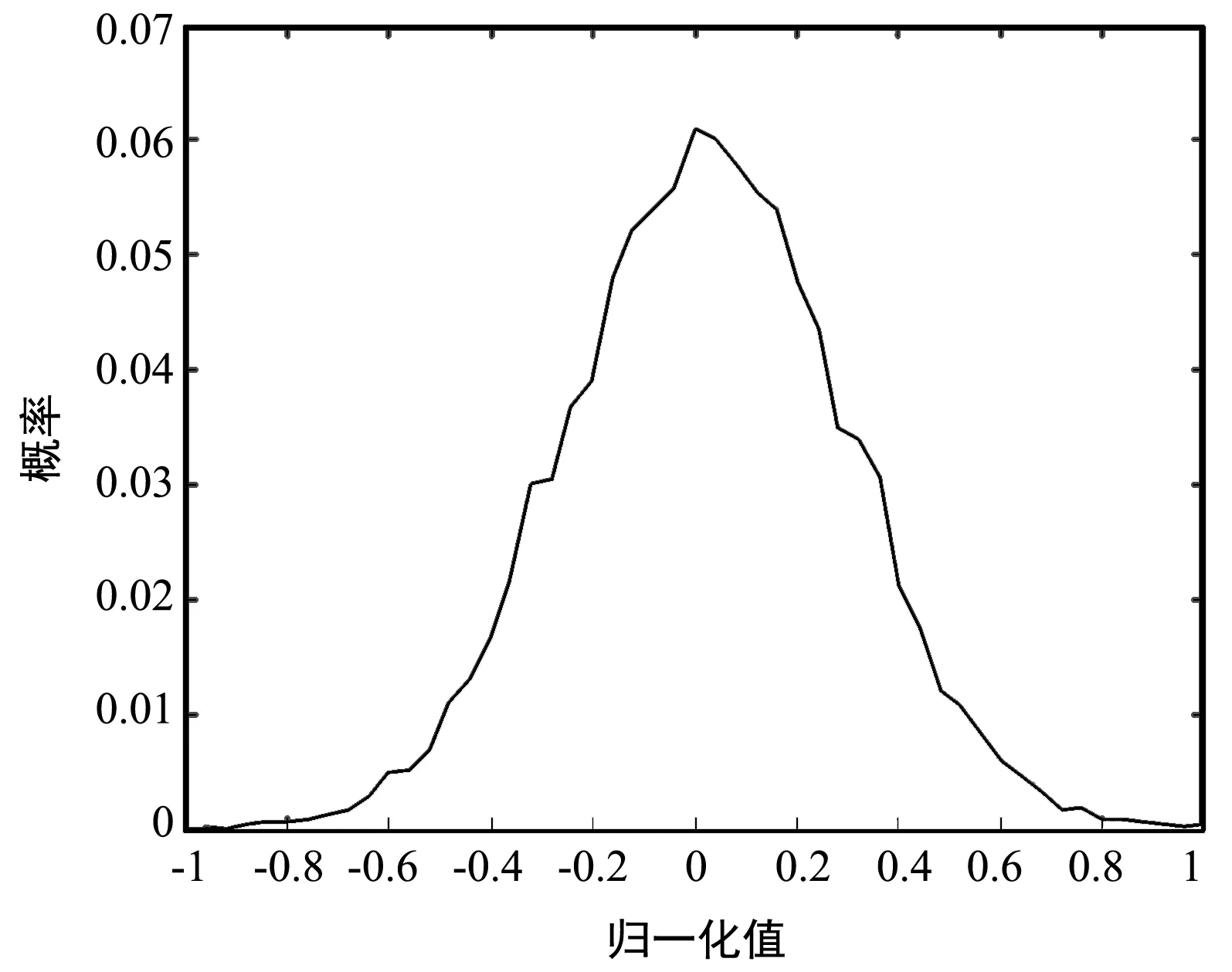

使用Box-Muller方法,在FPGA中硬件仿真,其高斯分布的Modelsim仿真波形如图3所示。从图中可以看出,该信号起伏无规律,并集中在平均值附近,这符合正态分布的时域特征,将该仿真数据进行采样,然后保存到TXT文档,使用Matlab计算概率密度函数,如图4所示。

图3 高斯信号仿真波形图

图4 概率密度函数

图4验证了此次仿真的数据,满足高斯分布。说明此次硬件实现的高斯分布基本正确。

2.2.2 指数函数的实现

在FPGA实现函数波形,一般有2种方法——DDS和坐标旋转数字计算方法(Coordinate Rotation Digital Computer,CORDIC)[10]。相比于DDS,CORDIC实现的精度较高,但耗费的资源较大。由于产生莱斯信道需要多路正弦和余弦波,为了节省资源,所以用DDS来产生它们。由于在高斯分布的实现中,只需要产生一路指数函数,考虑到实现的精度,本文采用CORDIC来实现指数函数。

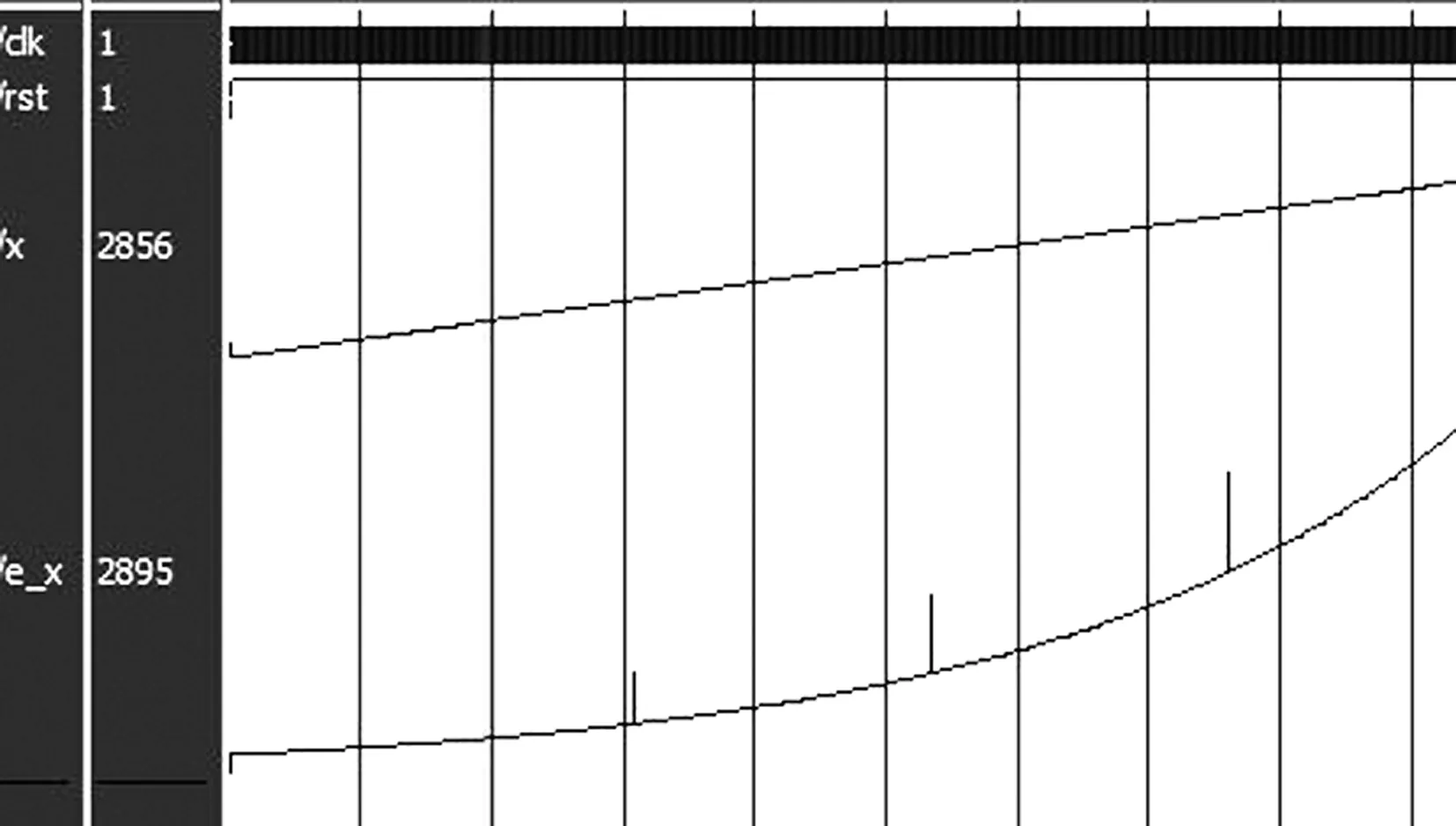

为了提高开发效率,本节使用Xilinx公司提供的CORDIC IP核。在该IP核设置选择输出"sinh and cosh",那么在两个输出端口分别是sinh和cosh函数,将两个端口相加即可得到指数函数[11]。在本次指数函数实现时,设置输入为16位,其中低13位为小数位,设置输出为16位,其中低11位为小数位。指数函数的Modelsim仿真波形如图5所示。

图5 指数函数的仿真波形

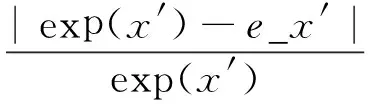

在图5中,仿真曲线基本符合指数函数逐渐递增的规律。为了计算误差,可以抽取波形中一个某个值进行误差计算,假如抽取图5中光标处的数值(x=2 856,e_x=2 895),根据本次设计中,则归一化之后的值为(x′=2 856/(213)= 0.348 6,e_x′=2 895/(211)= 1.413 6),因此该点处误差可由下式计算:

(1)

式(1)计算出的误差为2.5%,误差值较小。还可以将图5中的e_x值保存到文件,然后在MATLAB中分析,绘制误差曲线。经验证,本次在硬件中实现的指数函数误差较小,符合设计要求。

2.3 转移概率的实现

本节来介绍Lutz动态信道中,马尔可夫转移概率的硬件实现。

对于转移概率的取值,文献[3]是采用了一种最小平方拟合方法测量数据来决定的。文献[12-13]中利用最小均方误差准则以及最小均方误差法拟合出的模型参数来进行仿真,通过实际测试数据来确定状态转移概率:

(2)

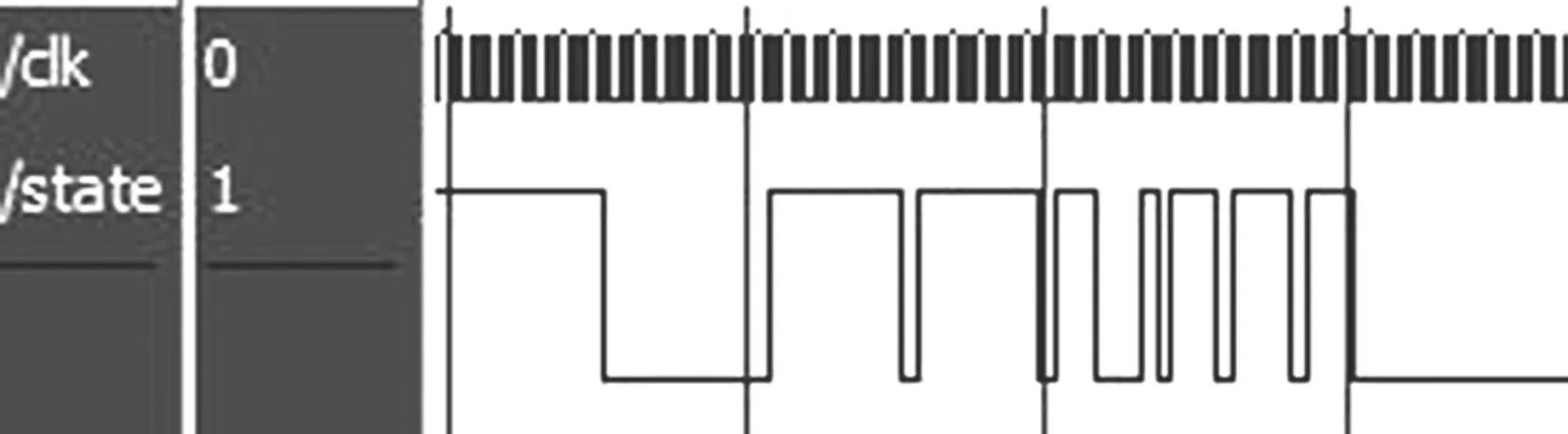

为了在硬件中实现式(2)的概率,采用上节中分析过的m序列。设定m序列为10位,则210*0.85=870,210*0.8=819,即设定一个两状态的状态机(0状态和1状态),当处于0状态时,判定m序列的值,小于870,则保持当前状态,否则跳转至1状态;当处于1状态时,判定m序列的值,小于819,则保持当前状态,否则跳转至0状态。Modelsim仿真如图6所示。

图6 信道状态转移仿真图

经过上文的分析和仿真,实现Lutz动态信道的各部分已完成,只需要对各个模块进行综合互联,即可完成Lutz动态信道的硬件实现。

3 高斯多普勒信道的实现

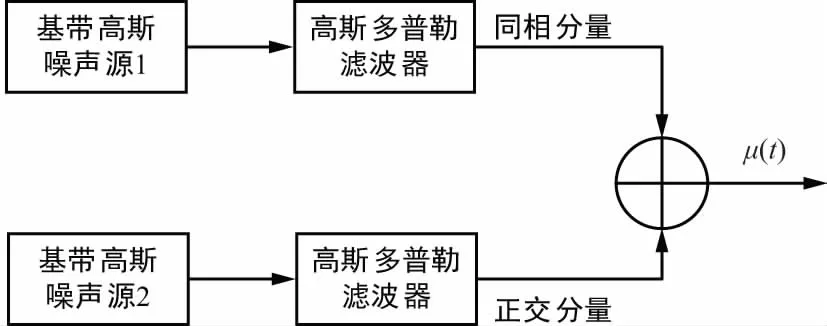

对于高斯多普勒信道的硬件实现,本文采用成型滤波法进行实现[14]。硬件实现框图如图7所示。

图7 高斯多普勒信道的硬件实现框图

由图7可知,同向分量和正交分量,它的时域和频域均呈高斯分布。

由于上文实现指数函数一节中,已经完成了在硬件中实现高斯分布的信号,所以本节只需要完成高斯多普勒滤波器即可。在设计高斯多普勒滤波器时,首先将高斯多普勒信道的时域自相关函数,使用MATLAB保存至coe文件,然后供Xilinx FIR IP核调用,该文件中的数据应按照FIR滤波器IP核所需格式进行保存。

将产生好的高斯分布的信号,经过该滤波器,得到的图形如图8所示。

图8 滤波前后对比图

从图8可以看出,经过滤波后的高斯信号,波形起伏急剧减小,这是因为高斯功率谱的滤波器相当于低通滤波,平滑了原先剧烈变化的波形。

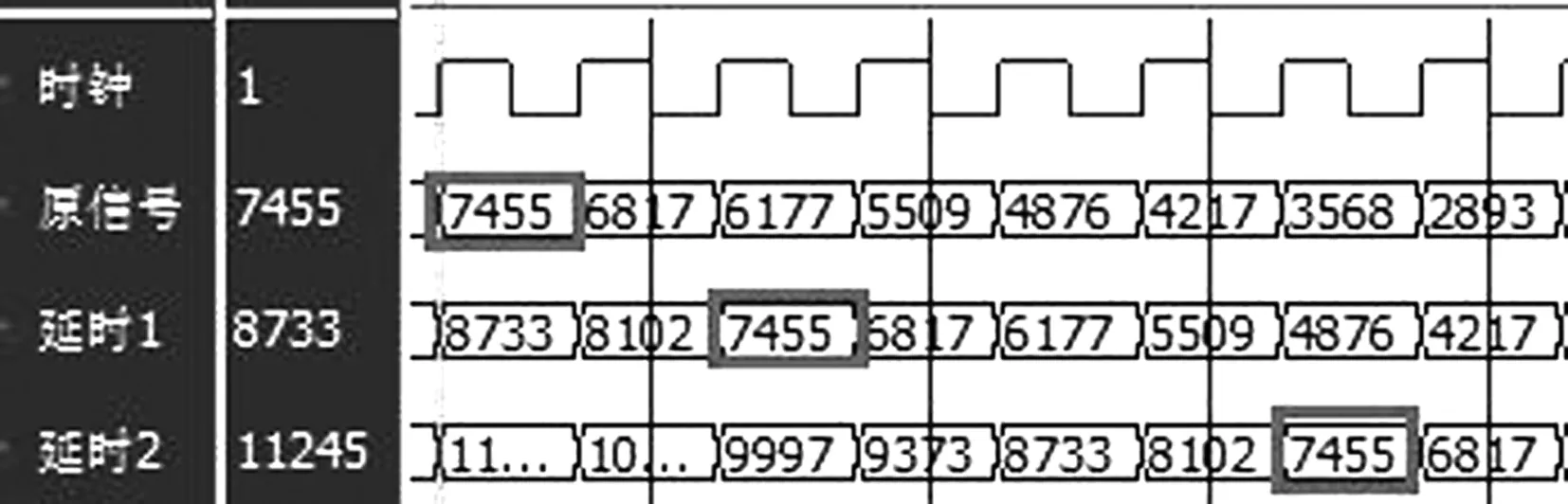

4 延时的实现

本文采用双口RAM来实现信号的延时[15]。本次仿真设定两路延时量分别为0.2 μs和0.6 μs。设定输入信号为cos(200 πt),系统时钟的频率为100 kHz,此时延时量分别为2个和6个时钟周期。其中设置数据宽度为16位,写地址和读地址位宽为8位。

为了达到延时的效果,需要首先将数据写入双口RAM,经过2个时钟和6个时钟后,再将该数据读出,即采用先写后读的方式。仿真结果如图9所示。

图9 信号的延时信息

在图9中对数据的延时进行显示,可以看出延时信号比原信号滞后2个时钟和6个时钟,如图中标记的数值7 455。

5 性能验证

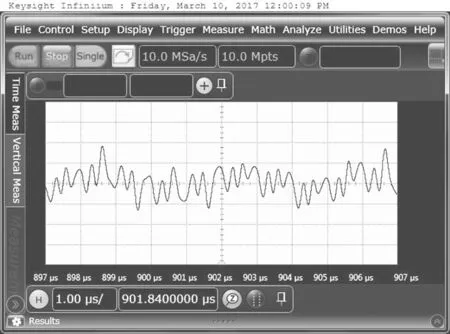

在图1信道仿真器实现框图中,将信号发生器产生的30 MHz中频模拟信号,经过AD变换和数字下变频,然后输入到由FPGA实现的信道仿真器中进行处理,接着对处理过的信号进行数字上变频,然后经过DA变换,最后将该模拟中频信号,输入示波器进行观察。

对FPGA实现的Lutz动态信道进行示波器观察,波形如图10所示。在图10中,可以看出Lutz信道的包络,明显有2个状态,验证了Lutz信道是由两状态随机切换的动态信道,表明本次Lutz信道硬件实现符合要求。

将Lutz信道的波形放大观察,如图11所示。该图的波形可以看成是多个正弦波的叠加的结果,也验证了本文中的平坦衰落信道是用正弦波叠加法实现的。

图10 示波器波形显示

图11 Lutz信道的波形

6 结束语

本文设计了基于Lutz信道的频率选择性信道,然后在FPGA中分模块实现。在Lutz模型实现时,瑞利信道采用Jakes模型,该模型中的正弦和余弦函数,采用DDS来产生。Suzuki信道的实现中,使用Box-Muller来产生高斯分布,使用CORDIC来产生指数函数,用m序列产生转移概率。高斯多普勒使用滤波法来实现,使用Xilinx FIR IP核进行设计。延时使用双口RAM来实现。数字上变频和下变频可以采用IQ解调和调制的方法实现。

在对该频率选择性信道实现后,使用Modelsim、Matlab和示波器等工具对已实现的硬件模块进行验证。结果表明,本次硬件实现的基于Lutz模型的频率选择性信道,符合理论要求,可直接用于实际通信系统的验证分析中。

[1] Patzold M. Mobile Radio Channels [M]. New York: Wiley,2011.

[2〗 Fard S F,Alimohammad A,Cockburn B F. An FPGA-Based Simulator for High Path Count Rayleigh and Rician Fading [J]. IEEE Transactions on Vehicular Technology,2010,59(6): 2725-2734.

[3〗 Lutz E,Cygan D,Dippold M,et al. The Land Mobile Satellite Communication Channel-recording,Statistics,and Channel Model [J]. IEEE Transactions on Vehicular Technology,1991,40(2): 375-386.

[4〗 田耘,徐文波. Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[5〗 Jakes W C. Microwave Mobile Communications [M]. New York: Wiley,1974.

[6〗 Zheng Y R,Xiao C. Improved Models for the Generation of Multiple Uncorrelated Rayleigh Fading Waveforms [J]. IEEE Communications Letters,2002,6(6): 256-258.

[7〗 Tierney J,Radre C M,Gold B. A Digital Frequency Synthesizer[J]. IEEE Transactions on Audio and Electroacoustics,1971,19(1):48-57.

[8〗 曾兴雯,刘乃安,孙献璞. 扩展频谱通信及其多址技术[M].西安:西安电子科技大学出版社,2014:39-57.

[9〗 Box P,Muller M. A Note on the Generation of Random Normal Deviates[J]. The Annals of Mathematical Statistics,1958,29 (2): 610-611.

[10] Volder J. The CORDIC Computing Technique [C]∥ Papers presented at the March 3-5,1959,Western Joint Computer Conference. ACM,1959: 257-261.

[11] Walther J S. A Unified Algorithm for Elementary Functions [C]∥ May 18-20,1971,Spring Joint Computer Conference. ACM,1971: 379-385.

[12] Fontan F P,Vazquez-Castro M,Cabado C E,et al. Statistical Modeling of the LMS Channel [J]. IEEE Transactions on Vehicular Technology,2001,50(6): 1558-1560.

[13] Prieto‐Cerdeira R,Perez‐Fontan F,Burzigotti P,et al. Versatile Two-state Land Mobile Satellite Channel Model with First Application to DVB-SH Analysis [J]. International Journal of Satellite Communications and Networking,2010,28(2): 291-315.

[14] Alimohammad A,Fard S F,Cockburn B F,et al. A Compact Single-FPGA Fading-Channel Simulator [J]. Circuits & Systems II Express Briefs IEEE Transactions on,2008,55(1): 84-88.

[15] 吴先芳. 基于FPGA的无线信道模拟器的实现及应用[D]. 大连:大连海事大学,2011.

[16] Fard S F,Alimohammad A,Cockburn B F. An FPGA-Based Simulator for High Path Count Rayleigh and Rician Fading [J]. IEEE Transactions on Vehicular Technology,2010,59(6): 2725-2734.

[17] Xiao C,Zheng Y R,Beaulieu N C. Statistical Simulation Models for Rayleigh and Rician Fading [C]∥ IEEE International Conference on Communications. IEEE,2003:3524-3529.

[18] Suzuki H. A Statistical Model for Urban Radio Propagation [J]. IEEE Transactions on Communications,1977,25(7): 673-680.

[19] 戴佳. 基于双跳频图案同步法的高速系统设计与实现[D]. 哈尔滨:哈尔滨工程大学,2016.

[20] Parsons J D,Bajwa A S. Wideband Characterisation of Fading Mobile Radio Channels [J]. Communications Radar & Signal Processing Iee Proceedings F,1982,129(2):95.

FPGAImplementationofWirelessChannelSimulatorBasedonLutzModel

GUO Li-li,LIU Qi-lin

(College of Information and Communication Engineering,Harbin Engineering University,Harbin Heilongjiang 150001,China)

The wireless channel simulator is a fitting of the real channel environment. It can improve the research and development (R&D) and testing efficiency of communication system,and has very strong practical significance. Lutz model,a non-steady channel,can switch between good channel state and bad channel state,and describe the changing characteristics of channel effectively. This paper describes the design of a frequency selective channel based on Lutz model,used in FPGA module,and then uses Modelsim and Maltab tool to verify the implementation of FPGA. The results show that the FPGA implementation of wireless channel simulator can meet channel statistical characteristics,and be directly used to test the wireless communication system.

wireless channel simulator; Lutz model; FPGA

TN911.251

A

1003-3114(2017)06-81-5

10. 3969/j.issn. 1003-3114. 2017.06.20

郭黎利,刘麒麟.基于Lutz模型的无线信道仿真器的FPGA实现[J].无线电通信技术,2017,43(6): 81-85.

[GUO Lili,LIU Qilin. FPGA Implementation of Wireless Channel Simulator Based on Lutz Model[J].Radio Communications Technology,2017,43(6):81-85.]

2016-05-25

国家自然科学基金项目(61271263)

郭黎利(1955—),男,教授,主要研究方向:现代通信系统理论与技术、通信信号处理技术。刘麒麟(1990—),男,硕士研究生,主要研究方向:无线信道模型、现代通信技术。