可防误翻转高精度欠压锁存电路设计

2017-10-12田磊姜振益

田磊,姜振益

可防误翻转高精度欠压锁存电路设计

田磊1, 2,姜振益1

(1. 西北大学现代物理研究所陕西西安,710069;2. 西安邮电大学电子工程学院,陕西西安,710121)

在分析传统欠压锁存电路(UVLO: Under voltage lockout)工作原理的基础上,利用VIS 0.4 μm BCD工艺设计一种具有防误翻转功能的高精度欠压锁存电路。该电路由3部分组成,以带隙比较器为核心,引入具有迟滞特性的防误翻转电路以保证欠压锁存信号能安全可靠地输出,并通过调整带隙基准的温度特性保证欠压锁存阈值精度,最后经过放大输出电路放大后,输出稳定的欠压锁存信号。采用Cadence软件对所设计的电路进行仿真。研究结果表明:在−40~125 ℃范围内欠压锁存阈值偏差最大为100 mV,阈值分辨率可达10−5V,在3~5 V工作电压下,防误翻转电路开启阈值为2.95 V,能有效防止欠压锁存电路误翻转。该电路的设计理念和仿真结果有助于后期电源芯片的开发。

欠压锁存;防误翻转;带隙比较器;高精度;BCD工艺

在电源管理芯片如功率因数校正控制器、电子镇流器、恒压恒流控制器中,当电源电压低于芯片的正常工作范围时,芯片内部某些电路会无法正常工作,并可能产生内部逻辑错误,从而使外部开关管处于不确定状态,有可能对外部电路和芯片造成损坏。因此,芯片内部必须加入欠压锁存电路。欠压锁存,即低电压锁存,可以提高芯片可靠性、安全性,对芯片输入电压进行检测,当输入电源电压过小时,能将芯片输出切断,使芯片内部保持在确定的安全状态,同时不会对外部器件造成损坏。欠压锁存电路用于芯片启动、关断过程,可以减小由于外部电源波动对芯片产生的影响。传统的欠压锁存电路集成了输入电压采样电路、电压基准源、迟滞比较器,以及外部电流偏置,这使得欠压锁存电路愈加复杂,版图面积和功耗也随之增加[1−4]。为了克服这些问题,本文作者在经典欠压锁存原理的基础上提出了一款改进型低电压启动工作,能检测高输入电源电压,并具有高精度带隙结构[5−7]和防误翻转功能[8−9]的欠压锁存电路。不仅具有精度极高的欠压锁存阈值和良好的温度系数[10−11],其安全可靠性也得到很好的保障。

1 电路工作原理及实现

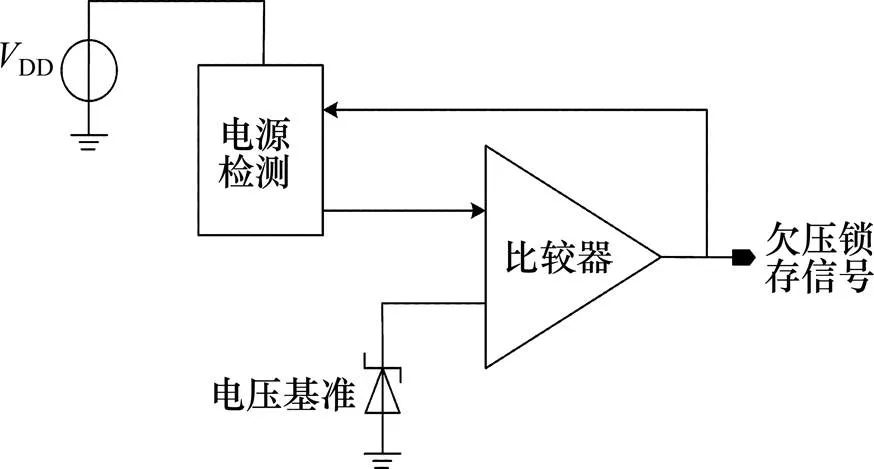

当电路中的电源电压DD从0电平逐渐上升时,电源检测电路模块将检测其变化情况,并不断将检测到的数值输入至后级的比较器中与电压基准进行比较,同时输出欠压锁存信号,将芯片锁定在安全状 态[12]。典型的欠压锁存电路结构如图1所示。

图1 欠压锁存原理图

当DD刚达到芯片开启阈值时,比较器两输入端达到平衡,输出即将翻转;随着DD上升,比较器输出电平立即翻转,芯片脱离锁定状态,开始正常工作,而此时欠压锁存信号反馈至电源检测电路,形成外部正反馈[13−14]。在芯片关断过程中,随着DD逐渐下降,会达到芯片的关断阈值,这时比较器输出锁存信号,将芯片锁定,直到电源电压下降至整个芯片停止工作。由于比较器和电源检测电路的正反馈特性,形成迟滞效应[15−16],使得芯片开启阈值和关断阈值不同,这样可以防止电源电压不稳定时芯片在欠压锁存阈值附近不断开启和关断。

2 改进后的电路实现

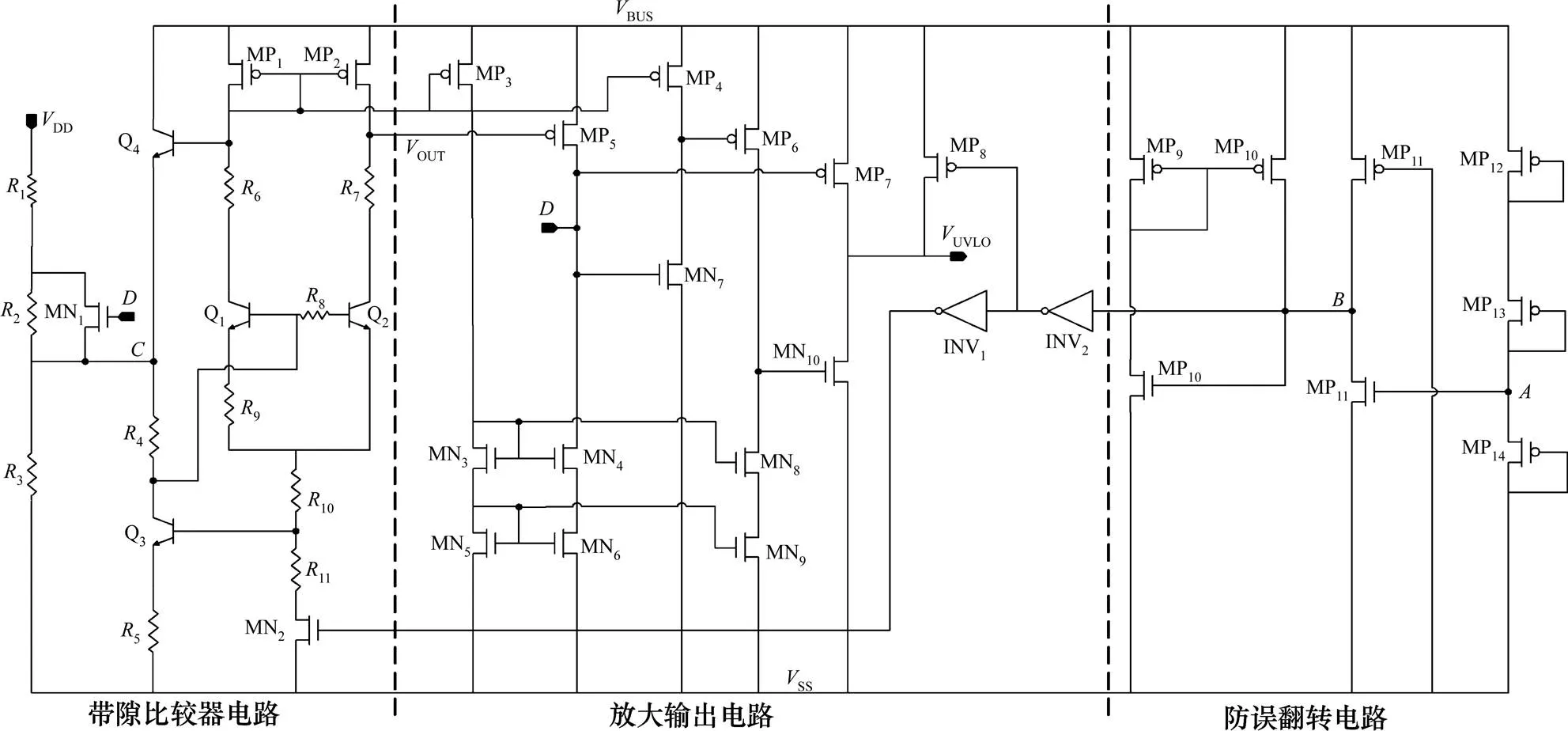

针对传统欠压锁存电路的缺点,提出了改进型的电路结构,改进型欠压锁存电路主要由防误翻转电路、带隙比较器电路和放大输出电路3部分组成。具体结构如图2所示。

图2 改进后的欠压锁存电路

2.1 防误翻转电路

此电路实质为MOS比较器,以MN11管的阈值作为参考电平。主要作用在于检测由电源电压DD(15~30 V)产生的内部低压电源BUS(3~5 V)是否已达到开启带隙比较器电路的稳定电压,只有当BUS稳定后,带隙比较器才能开始工作,欠压锁存信号开始正常输出,否则输出将会被锁定。MOS管MP12~MP14以二极管连接检测BUS,当BUS较低时,MN11关断,MP11开启,点输出高电平,经反相器输出将MN2关断,MP8开启,从而使UVLO输出为高,芯片处于锁定状态。随着BUS逐渐上升,MN11开启后将点拉至低电平,同时将MN2开启,MP8关断,欠压锁存电路开始正常工作。

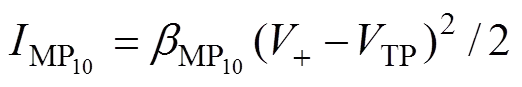

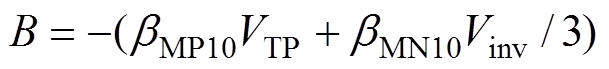

MP9,MP10与MN10对点构成正反馈。当MN11开启后,点降低,MN11的栅源电压GS进而下降,其漏端电流MN11随之下降,经MP9镜像,MP10和MN11支路电流下降,由沟道调制效应可知点电位将进一步降低,加速了防误翻转电路的输出速度,并形成迟滞效应。上阈值+的计算(VBUS上升阶段)为:

(2)

(3)

其中:GS11=+/3,GS10=DS=inv(反相器翻转门限),=Cox(/),整理得

(5)

根据实际的BUS,取合理范围内的解。

(7)

(9)

下阈值−的计算方法与上阈值相同,只是器件的状态改变相反。

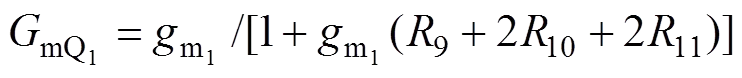

2.2 带隙比较器电路

BUS稳定后,带隙比较器开启,MN2作为开关管,其导通后DS电压可以忽略不计,电阻对电源DD分压采样,向Q1和Q2基极提供偏置,产生基准参考电压。根据带隙基准产生的原理,Q1发射极面积为Q2的4倍,由Q1,Q2和R9产生PTAT电流Q1,m1=4m2由于电阻9~11的射极负反馈作用,Q1和Q2等效跨导为:

(11)

由于m29>>1,所以m1<m2,即Q1集电极电流Q1变化率小于Q2集电极电流Q2变化率。当DD较小时,Q1<Q2,通过电流镜MP1镜像到MP2的PTAT电流小于Q2,Q2支路为了达到平衡,MP2进入线性区,OUT将输出高电平。

随着DD升高,Q1基极电位也逐渐增高,某一时刻Q1和Q2支路将达到电流相等的状态,OUT仍保持高电平,这时Q1基极电压为

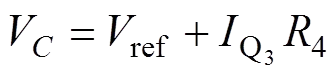

图2中三极管Q3,Q4与R4构成对基准电压ref的二阶温度补偿。8用于基极限流,减小基极电流对Q1和Q2集电极支路电流的影响。在温度以下,Q3关断,点电位即基准电压ref;随着温度上升,Q3开启,产生负温度系数电流Q3,流过电阻4与ref叠加得到补偿后基准电压及温度系数:

(13)

(15)

只需调整电阻4,5,9~11即可改进基准电压的温度特性。

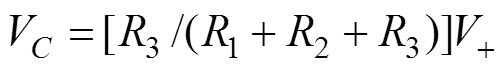

当DD继续升高后,Q1>Q2,MP1镜像到MP2的PTAT电流大于Q2,为了达到平衡,MP2将进入饱和区,OUT输出为低,同时UVLO发生翻转,可计算这时的上翻转阈值电压+。

电阻分压得到的点电压:

令式(14)等于式(16)得:

在DD达到正翻转阈值后,点MP5漏端电压输出为高,开关管MN1开启,将电阻2短路,这时点电压为

>(18)

由于V增大,加快了欠压信号翻转的速度,这个环路为正反馈,同时形成了迟滞。同理,在DD下降的过程中,下翻转阈值_为

(19)

迟滞区间为

(20)

2.3 放大输出电路

带隙比较器输出的欠压锁存信号(OUT)有可能因摆幅太小而无法使后级开关迅速开启和关断,因此添加放大输出级是必要的。由图2可知:此部分可以看作三级共源级和一个推挽输出级,主要由MP5~MP7,MN7与MN10完成对带隙比较器输出欠压信号OUT的放大过程。

当DD上升未达到上阈值前,OUT输出为高,点电位为低,MP5,MN7,MP6,MN10已关断,此时MP7处于开启状态,将UVLO输出拉至高电平BUS。

当DD达到上阈值后,OUT输出由高变低,MP5开启,将点上拉至高电平BUS,电阻2被短路,进而将MN7,MP6,MN10开启,而此时MP7被关断,UVLO输出由高变低,芯片脱离欠压锁定状态。

由于下阈值与上阈值具有迟滞量,因而DD必须下降到低于下阈值后UVLO才能翻转,这时OUT输出由低变高,将MP5关断,点被拉低至地,从而开启MP7,MN7,MP6,MN10都处于关断状态。随后UVLO将保持为高,一直到整个芯片关闭。

3 电路仿真结果与分析

3.1 仿真结果

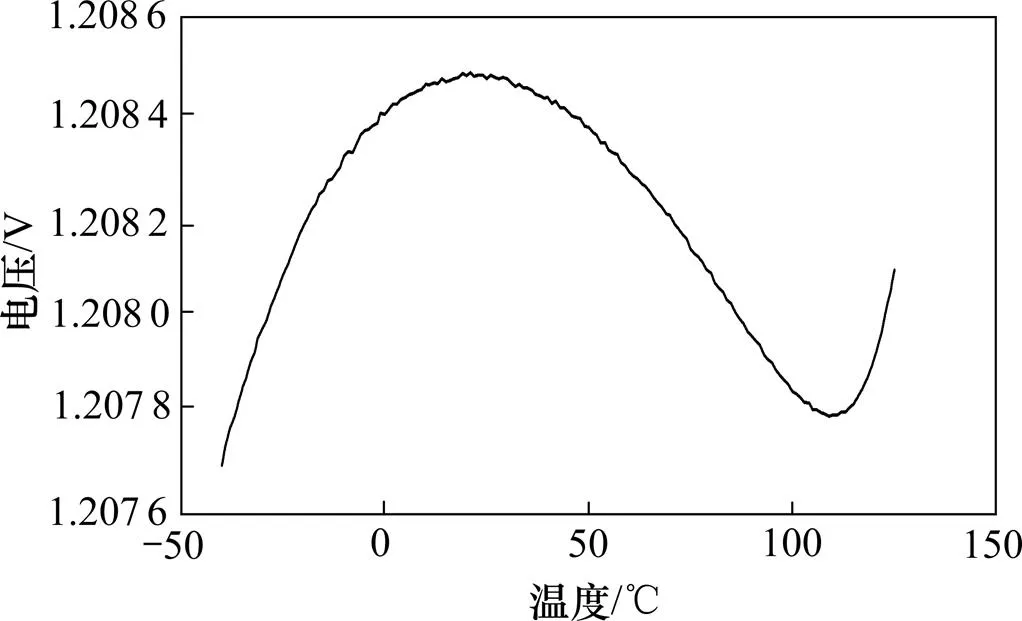

本文设计的欠压锁存电路多应用于电源工作范围在−0.3~20 V的PFC控制芯片中,为了更好地设计各项指标,本文针对改进的电路各模块采用Cadence进行仿真验证,器件模型采用VIS 0.4 μm BCD工艺的典型情况,温度设为−40~125 ℃。首先对带隙基准电路的温度特性进行仿真,其仿真结果如图3所示。

由图3可见:基准电压经过二阶温度补偿后稳定在1.208 V附近,温度系数可达到5×10−6℃−1,能够为后级的比较器提供稳定精确的参考电位,进而保证欠压锁存电路阈值电压的稳定输出。

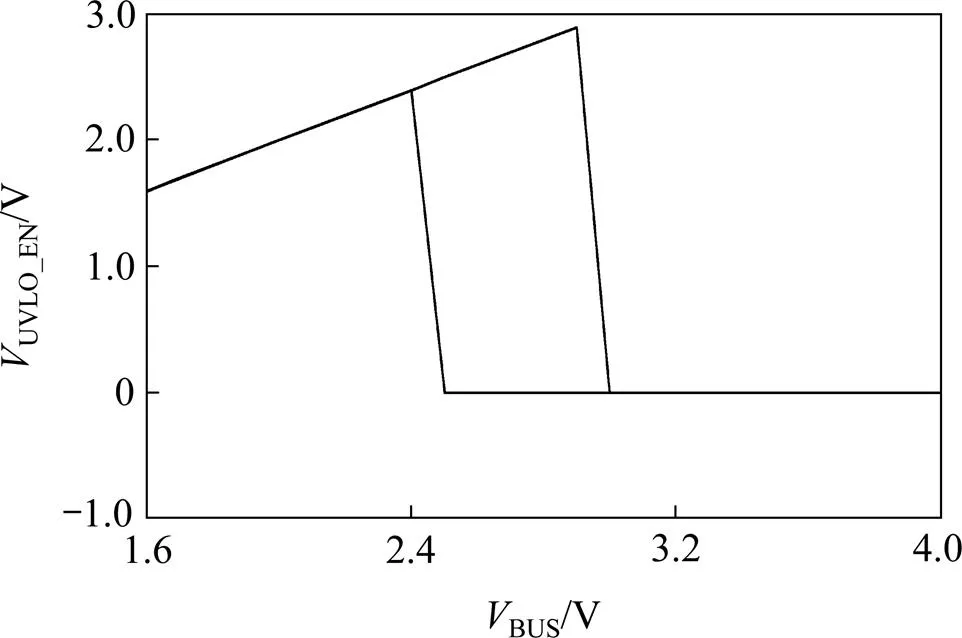

为了确保欠压锁存电路的输出信号安全,本文对后级的防止误翻转电路进行仿真,其直流特性曲线如图4所示。图中BUS是芯片内部的稳压电源,可以设置为3~5 V,在实际工作中,采用低电压供电可以减小芯片功耗和欠压锁存阈值的偏差。所以,防误翻转电路只需在BUS稳定建立时使后级输出脱离锁定即可,仿真结果表明上阈值为2.95 V,下阈值为2.5 V,这样即可确保欠压锁存电路安全输出。

图3 带隙比较器基准电压温度特性曲线

图4 防误翻转电路的直流特性曲线

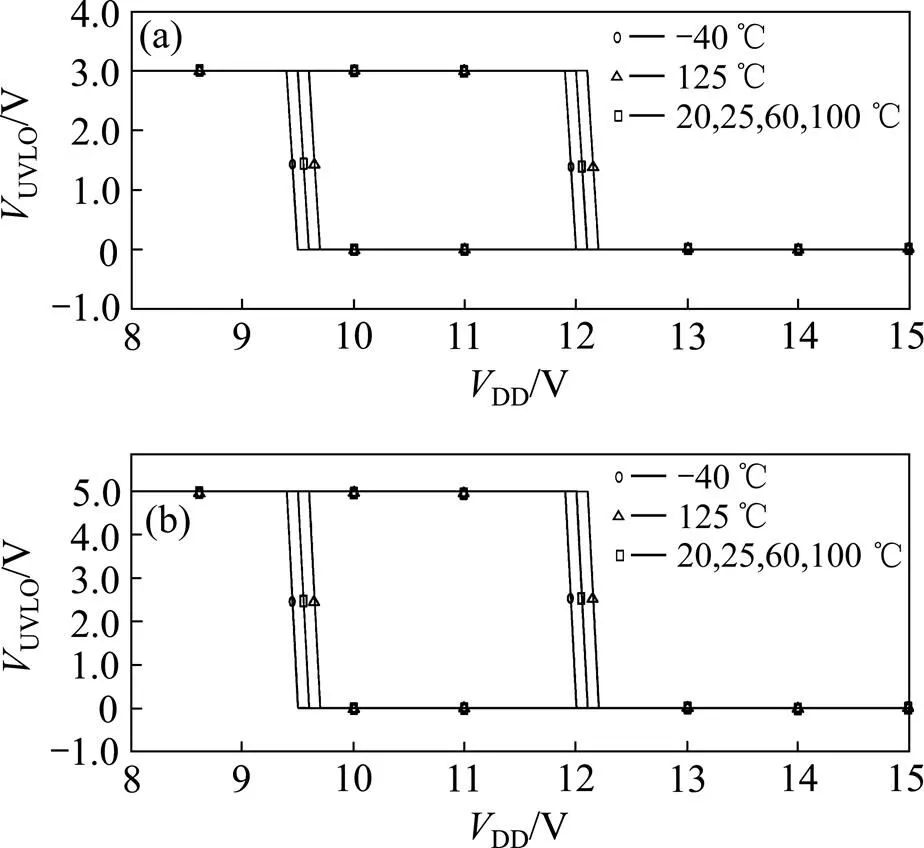

为了确定欠压锁存电路输出信号的温度特性,分别在不同电压的情况下,温度取−40,−20,25,60,100及125 ℃,对UVLO的输出进行仿真,结果如图5所示。

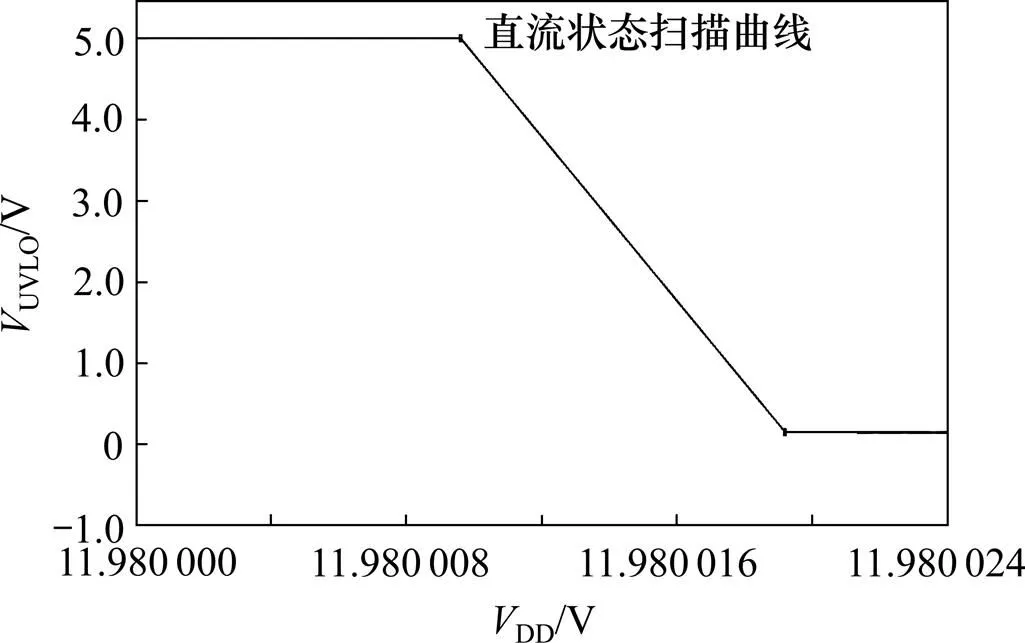

当电源电压DD选为8~15 V时,可看出25 ℃时翻转阈值为12.1 V与9.6 V,迟滞量2.5 V。阈值失真为±100 mV,在−20~100 ℃间阈值偏差几乎为0(图中曲线重合)且BUS取3~5 V电压对阈值无影响。在仿真条件不变的情况下,设置步长为10−6V,对DD进行11.9~12.1 V直流扫描,欠压锁存阈值精度的仿真结果如图6所示。

由图6可见:DD在11.980 010 V时UVLO为高,当DD达到11.980 021 V时,UVLO变低,分辨率为0.01 mV,精度完全满足电路要求。

VBUS/V: (a) 3; (b) 5

图6 欠压锁存阈值精度仿真曲线

3.2 实测与分析

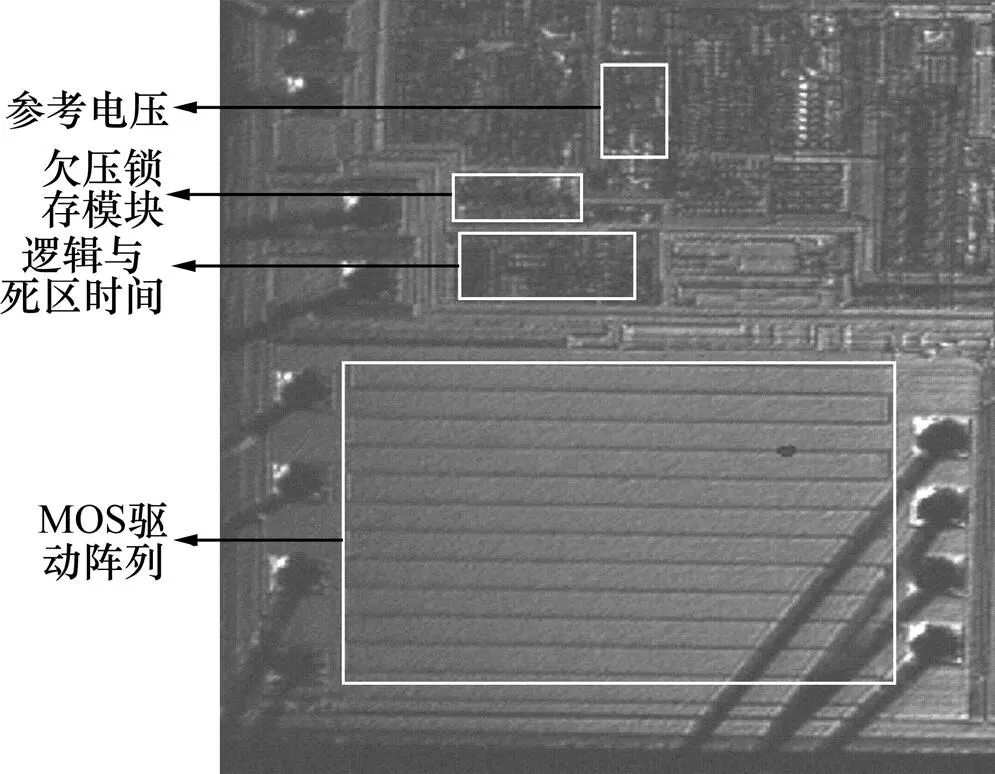

图7所示为所设计芯片的显微照片,裸片长×宽为1 313 μm×878 μm,基准和欠压锁存模块位置如图7所示。

使用泰克(Tektronix)TDS5104B示波器对流片后的芯片进行测试。当芯片内部输入电压为3~5 V时,实测结果如图8所示。

图8中,上电初始时刻,BUS小于阈值门限时,芯片的输出信号恒为逻辑低电平,当BUS上升至下阈值后,UVLO输出高电平,芯片正常工作;掉电初始时刻,BUS大于上阈值时,芯片仍可正常工作,当下降至上阈值,UVLO输出低电平,芯片不工作。由此可以看出,实测结果与仿真数据吻合,可以满足芯片实际工作的需求。

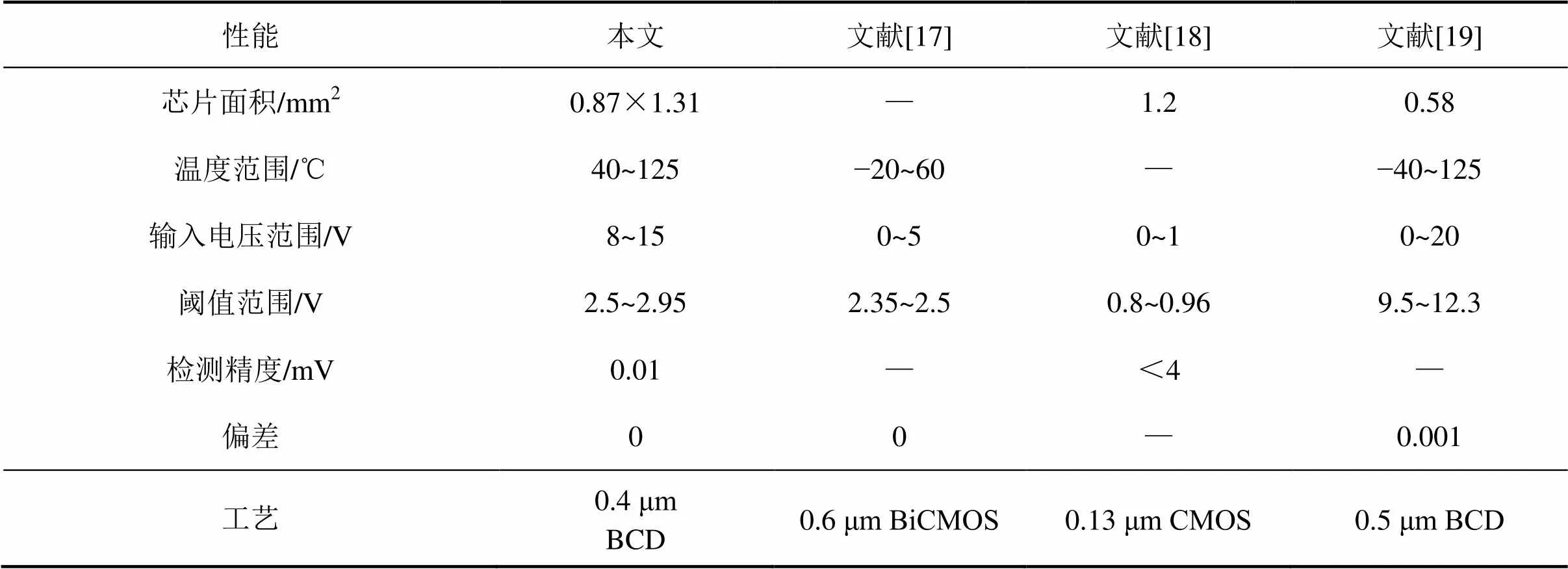

表1所示为本文设计的高精度欠压锁存电路模块与文献[17−19]中的欠压锁存电路性能参数的比较结果。由表1可以看出:本文所设计的欠压锁存电路具有较高的精度。

由此可见,本文设计的欠压锁存电路具有精度高,偏差小的特点,可以避免后即电路的误操作,能够完全满足开关电源后续的电路要求。

图7 芯片的显微照片

(CH1, VBUS为2 V/div; CH2为1 V/div)

表1 UVLO模块的性能对比

4 结论

1) 针对开关电源系统中必需的欠压锁存功能,在传统理论的基础上设计了一款改进型具有防误翻转功能的高精度欠压锁存电路。该电路可以工作在3~5 V电压下检测10~30 V的电源电压而不产生阈值失真,采用带隙比较器,使得欠压锁存阈值精度可达10−5V,且具有良好的温度稳定性,以25 ℃为参考,在−40~125 ℃范围内阈值失真为100 mV。

2) 加入防误翻转电路后,保证欠压锁存信号能在工作电压稳定后输出。该欠压锁存电路经过工艺和器件尺寸调整可应用于各种电源芯片中。

[1] 邹雪城,韩俊峰. 一种基于比例电流的欠压保护电路的设计和实现[J]. 华中科技大学学报(自然科学版), 2007, 35(10): 64−66.ZOU Xuecheng, HAN Junfeng. Design and implementation of an undervoltage lockout circuit base on proportional current[J]. Journal of Huazhong University of Science and Technology (Natural Science Edition), 2007, 35(10): 64−66.

[2] LIN R L, YEH P Y, LIU C J H. Positive feed-forward control scheme for distributed power conversion system with multiple voltage sources[J]. IEEE Transactions on Power Electronics, 2012, 27(7): 3186−3194.

[3] WU Xiaobo, ZHANG Yongliang, ZHANG Danyan, et al. Design of a monolithic hot swap controller IC with BCD technology[J]. Chinese Journal of Semiconductors, 2006, 27(5): 948−954.

[4] WOOD P N. Monolithic level-shifting MOS gate drivers cut parts count while providing added control functions[J]. Power conversion and Intelligent Motion, 1994, 20(8): 40−44.

[5] SHEN Z J, SABUI G, MIAO Zhenyu, et al. Wide-bandgap solid-state circuit breakers for DC power systems[J]. IEEE Transactions on Device and Circuit Considerations in Electron Devices, 2015, 62(2): 294−300.

[6] OSAKI Y, HIROSE T, KUROKI N, et al. 1.2 V supply, 100 nW, 1.09 V bandgap and 0.7 V supply, 52.5 nW, 0.55 V subbandgap reference circuits for nanowatt CMOS LSIs[J]. IEEE Journal of Solid-State Circuits, 2013, 48(6): 1530−1538.

[7] ZHANG Hualei, XIAO Zhibin, XI Tan, et al. Low-power sub-1-V compact bandgap reference for passive RFID tags[J]. Electronics Letters, 2015, 51(11): 815−816.

[8] CHUANG Y L, KIM S M, SHIN Y S, et al. Pulsed- latch aware placement for timing-integrity optimization[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(12): 1856−1869.

[9] LUO Yinhong, ZHANG Fengqi, GUO Hongxia, et al. Single-event cluster multibit upsets due to localized latch-up in a 90 nm COTS SRAM containing SEL mitigation design[J]. IEEE Transactions on Nuclear Science, 2014, 61(4): 1918−1923.

[10] LI Jinghu, ZHANG Xingbao, YU Mingyan. A 1.2 V piecewise curvature-corrected bandgap reference in 0.5 μm CMOS process[J]. IEEE Transactions on Very Large Scale Integration Systems, 2011, 19(6): 1118−1122.

[11] ZHOU Zekun, YUE Shi, ZHI Huang, et al. A 1.6 V 25 μA 5 ppm/℃curvature-compensated bandgap reference[J]. IEEE Transactions on Circuits and Systems Ⅰ: Regular Papers, 2012, 59(4): 677−684.

[12] 潘学文, 周继承, 郑旭强. 一种基于电平位移电路的低电压全摆幅CMOS运放[J]. 中南大学学报(自然科学版), 2010, 41(4): 1473−1477. PAN Xuewen, ZHOU Jicheng, ZHENG Xuqiang. A level-shifting circuit based on low-voltage rail-to-rail CMOS op-amp[J]. Journal of Central South University (Science and Technology), 2010, 41(4): 1473−1477.

[13] TIAN Lei, LAI Xinquan. Symmetrical structure strong drive capability optocoupler sensor[J]. Sensors and Transducers, 2013, 159(11): 319−323.

[14] ZHANG Yunwu, ZHU Jing, SUN Weifeng. A novel UVLO circuit with current-mode control technique for DC-DC converters[J]. Advanced Information and Computer Technology in Engineering and Manufacturing, Environmental Engineering, 2013, 765/766/767: 2534−2537.

[15] ANVARIFARD M K, OROUJI A A. Improvement of electrical properties in a novel partially depleted SOI MOSFET with emphasizing on the hysteresis effect[J]. IEEE Transactions on Electron Devices, 2013, 60(10): 3310−3317.

[16] RODRIGUES C R, MULLER C, MONTEIRO NETO D J. Hysteresis settling technique for CMOS comparators based on substrate voltage[J]. Electronics Letters, 2013, 49(1): 27−28.

[17] 王瑾, 田泽, 李攀, 等. 一种改进的BiCMOS工艺欠压锁存电路的设计[J]. 现代电子技术, 2007, 24(3): 182−184. WANG Jin, TIAN Ze, LI Pan, et al. Design of an improved under voltage lock out circuit based on BiCMOS process[J]. Modern Electronics Technique, 2007, 24(3): 182−184.

[18] 陈铖颖, 陈黎明, 范军, 等. 一种用于助听器SoC的上电复位及欠压检测电路[J]. 微电子学, 2015, 45(5): 607−610, 614. CHEN Chengying, CHEN Liming, FAN Jun, et al. A power- on-reset and brown-out circuit for hearing-aid SoC[J]. Microelectronics, 2015, 45(5): 607−610, 614.

[19] ZHAO Y R, LAI X Q. Novel bandgap-based under-voltage- lockout methods with high reliability[J]. Journal of Semiconductors, 2013, 34(10): 105008-1−8.

(编辑 赵俊)

Design of high precision undervoltage lockout circuit with function of anti-error flip

TIAN Lei1, 2, JIANG Zhenyi1

(1. Institute of Modern Physics, Northwest University, Xi’an 710069, China;2. School of Electronic Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121, China)

Based on the analysis of the traditional under voltage lockout theory, a high precision undervoltage lockout circuit with the function of preventing error flip was designed using the VIS 0.4 μm BCD process. The circuit was made up by three parts with the core of the bandgap comparator. The anti-error flip circuit with the hysteresis characteristics was designed to ensure that the UVLO circuit could output the safety signal. To guarantee the precise UVLO the temperature characteristic of the bandgap circuit was adjusted. At last, the output goes through the amplifier circuit to output the stable UVLO signal. The whole circuit was simulated in the Cadence software. The results show that the maximum threshold voltage distortion is only 100 mV and the threshold resolution ratio is 10−5V at −40−125 ℃. Working in the voltage from 3 V to 5 V, the turn-on threshold of anti-error flip circuit is 2.95 V. It could keep the whole circuit in safe. The circuit design and simulation results can help power supply chip late development.

under voltage lockout; prevent error reversal; bandgap comparator; high precision; BCD process

10.11817/j.issn.1672-7207.2017.09.019

TN432

A

1672−7207(2017)09−2396−06

2016−09−28;

2016−12−13

陕西省教育厅专项科研计划项目(15JK1676);西安市社会科学规划基金重点资助项目(2015EA03);西安邮电大学青年教师基金重点资助项目(101-0488) (Project(15JK1676) supported by the Shaanxi Provincial Department of Education Scientific Research of China; Project(21015EA03) supported by Key Project of Social Science Planning of Xi’an City; Project(101-0488) supported by the Youth Founded Project of Xi’an University of Posts and Telecommunications)

田磊,博士后,讲师,从事电源芯片、光电集成电路的研究;E-mail: tianlei@xupt.edu.cn