反应离子刻蚀硅槽工艺研究

2017-09-21赵金茹蒋大伟陈杰

赵金茹,蒋大伟,陈杰

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

反应离子刻蚀硅槽工艺研究

赵金茹,蒋大伟,陈杰

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

在CMOS多晶硅刻蚀工艺的基础上进行工艺开发,采用氯气和溴化氢气体进行硅槽刻蚀。通过对功率、压力、气体流量等工艺参数拉偏,用扫描电子显微镜观察硅槽侧壁形貌,分析各参数在反应离子刻蚀中所起到的作用,得到对硅槽形貌影响较大的因素,最终得到一种能够与CMOS工艺兼容的硅槽刻蚀方法。该方法能够制作出深度6 μm、深宽比4∶1、侧壁光滑的硅槽,可以用于光电继电器、硅电容等新型器件的研发。

硅槽刻蚀;氯气;溴化氢;反应离子刻蚀;光电继电器;硅电容

1 引言

随着集成电路的不断发展,硅槽刻蚀的应用越来越广泛,如硅槽隔离和电容的制作。传统平面电容工艺占用芯片面积大,电容容量有限。硅槽电容利用了硅槽的侧壁面,与平面电容相比,可大幅度降低硅片表面占有率,电容量亦有较大幅度的提高。集成电路中硅槽隔离具有许多优点,与常规的LOCOS隔离相比,芯片表面积占有率降低,可防止穿通和闭锁现象,有利于器件性能的改善和集成度的提高。与SOI材料应用结合可实现单个硅岛间的有效隔离,多个单元结构串联可形成光电池组,在光通信和光电开关领域应用十分广泛,硅槽的制作要求很高,对每一个硅槽都要进行精确的控制,既要有良好的硅槽形貌,又要保证一定的刻蚀深度,满足一定的深宽比。硅槽常用的等离子刻蚀技术可分为反应离子刻蚀(RIE)、微波电子回旋共振等离子刻蚀(ECR)和感应耦合等离子体刻蚀(ICP)。本文采用反应离子刻蚀设备,使用氯气和溴化氢气体刻蚀出简单的深硅槽,深宽比4∶1,槽深6 μm,可与传统的CMOS工艺线兼容,用于各类新型半导体产品如光电继电器、硅电容等的研究和开发。

2 硅反应离子刻蚀气体选择

硅的反应离子干法刻蚀是硅片制造中的关键工艺技术。反应离子刻蚀的两个主要硅层是制作MOS栅结构的多晶硅和制作器件隔离或电容结构中的单晶硅。

常用刻蚀硅的化学气体有两类,一类是氟基气体,包括CF4、SF6、NF3、CF4/O2、C4F8等,在刻蚀过程中氟原子起作用,但是刻蚀是各向同性的,图形尺寸较难控制,选择比一般。另一类与硅反应的化学气体是氯基气体和溴基气体,如氯气、溴气、溴化氢或氯气和溴气的混合气体等,刻蚀是各向异性的,并对SiO2、SiN的选择比较高,是CMOS工艺中多晶栅腐蚀常用的气体。反应离子刻蚀硅时采用的氟化物或氯化物气体,在辉光放电中分解出氟原子或氯原子,与表面硅原子反应生成气态产物,达到刻蚀目的。下面是硅的热力学自发反应方程式:

氟基气体最易与硅发生自发化学反应,氯基和溴基气体相对较难发生化学反应,因此氯基和溴基常用来进行各向异性刻蚀。同时,与氟基气体相比,氯基气体和溴基气体刻蚀生成物SiCl4、SiBr4相对难挥发,能在一定程度上保护刻蚀侧壁并对掩模层有较高的选择比,有利于陡直硅槽的获得。

3 实验

使用Precision 5000反应离子刻蚀设备平台,使用氯气、溴化氢刻蚀气体,以CMOS工艺中的多晶栅刻蚀菜单为基础菜单,进行实验调整,尝试6 μm深的硅槽刻蚀。基础菜单为功率250 W,压力75 mtorr,氯气流量50 sccm,溴化氢流量50 sccm,磁场30 gauss。对刻蚀菜单中的功率、流量、压力等参数进行窗口拉偏。

干法刻蚀过程中掩模的选择很重要,是影响刻蚀成功与否的重要因素。实验使用光刻胶和硅片衬底上的SiO2(SiN)膜层共同作为硅槽刻蚀的掩模。掩模制作过程为:第一步,在硅片衬底上生长一层SiO2(SiN),根据器件需要,厚度可在150~1 200 nm之间;第二步,涂2.7 μm厚的光刻胶掩模,曝光刻出需要的图形;第三步,进行SiO2(SiN)图形刻蚀,露出硅衬底。掩模制作完成,进行后续硅槽刻蚀。

3.1 功率拉偏实验

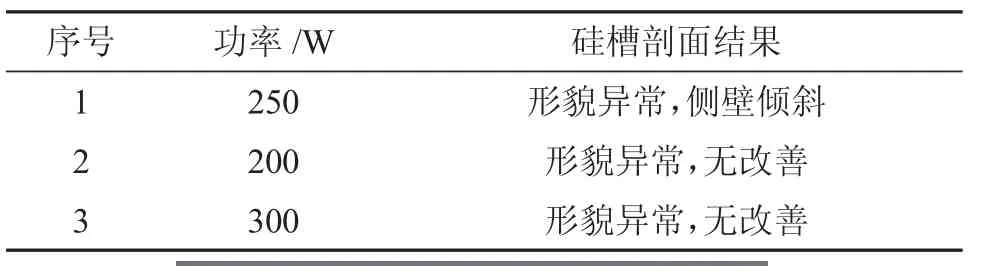

在原多晶栅基础菜单上增加和减少功率,实验条件以及结果见表1和图1。

表1 功率拉偏设计表

图1 硅槽剖面,侧壁倾斜

使用扫描电子显微镜测试硅槽剖面,实验结果显示减少和增加功率对硅槽侧壁形貌影响不明显。硅槽侧壁倾斜,硅槽右侧有凹角,侧壁垂直度不佳导致硅槽底部尺寸狭小,这不利于后续硅槽的填充,影响电学参数。

3.2 流量拉偏实验

表2 流量拉偏设计表

调整氯气和溴化氢流量比例,增加氯气流量,减少溴化氢流量,减少聚合物的生成,结果显示剖面形貌异常,没有改善。增加氦氧气体,硅槽侧壁没有改善,同时引入了侧壁毛糙的问题。

3.3 压力拉偏实验

表3 压力拉偏设计表

调整压力,压力由基础菜单的75 mtorr减少为50 mtorr,硅槽剖面形貌恶化十分严重,硅槽侧壁严重倾斜,硅槽底部只有一条缝,见图2。可见压力对硅槽的侧壁形貌起到重要的作用。增加压力至110 mtorr,硅槽形貌有改善,侧壁垂直度明显增加。继续增加压力至200 mtorr,硅槽形貌正常,侧壁垂直,剖面角度可达85°以上,见图3。最终硅槽刻蚀菜单为功率250 W,压力200mtorr,氯气流量50sccm,溴化氢流量50sccm,磁场30 gauss。该菜单对硅的腐蚀速率为380 nm/min,片内均匀性可达1%~3%。

图2 硅槽剖面侧壁严重倾斜

图3 硅槽剖面形貌正常

4 结果与讨论

硅槽刻蚀要求比较严格,既要保证较高的纵横比,满足刻蚀深度,又要有良好的硅槽侧壁形貌。对硅槽电容而言,一旦有侧壁不平整或尖角现象存在,会降低该处生长的SiO2质量,从而影响其电容特性。同样对于硅槽隔离而言,硅槽的剖面形貌也是影响隔离效果的重要因素。

反应离子刻蚀既有等离子体对被腐蚀材料的物理轰击,又有等离子体与被腐蚀材料的化学反应,刻蚀各项异性好。功率是用来产生等离子体及提供等离子能量的来源,功率越高,离子轰击能量越大,刻蚀速率相应提高,但同时也增加了对侧壁和掩蔽层的刻蚀,影响侧壁粗糙度和刻蚀选择比。压力同时影响等离子体密度及轰击能量,压力增大等离子浓度增加,硅的刻蚀速率增大,相应地影响了刻蚀形貌。硅槽刻蚀与多晶栅刻蚀的区别在于,硅槽有较高的纵横比,刻蚀反应物更难进入到硅槽底部进行反应,并且反应生成物难以逃逸,导致硅槽形貌难以控制。实验结果显示调整压力对硅槽侧壁形貌有明显的影响,通过增加压力可以改善硅槽侧壁垂直度。使用CL2和HBR气体刻蚀6 μm深的硅槽,当压力200 mtorr时硅槽侧壁光滑,剖面角度大于85°,基于现有设备平台实现硅槽刻蚀,不需要再引进硅槽刻蚀的专用设备。目前应用在硅电容和光电继电器研究中,硅电容能够实现电容值25 nF;光电继电器产品,硅槽刻蚀后硅槽填充形貌正常,见图4,实现了产品的硅槽隔离。

图4 光电继电器硅槽隔离图

5 结束语

硅槽的刻蚀深度和剖面形貌是影响产品性能的关键因素。在独立的反应离子刻蚀平台,氯基气体和溴基气体主要应用于多晶硅刻蚀和浅硅槽刻蚀,刻蚀出形貌良好的深硅槽具有极大的挑战性。本研究使用氯气和溴化氢气体成功制作出深宽比4∶1的6 μm深硅槽,硅槽的整体刻蚀速率会随着深宽比的增加而减少,对于深宽比要求不高的大尺寸硅槽,深度可在6 μm基础上继续加深。实验拉偏各刻蚀参数窗口,发现腔体压力对硅槽侧壁形貌起到决定性的影响作用,为利用氯气和溴化氢气体刻蚀深硅槽提供了一定的参考价值,目前已用于光电继电器和硅电容的产品生产研发中。

[1]李兴.超大集成电路技术基础[M].北京:电子工业出版社,1999:168-169.

[2]Michael Quirk Julian Serda.半导体体制造技术[M].韩郑生,等译.北京:电子工业出版社,2006:426-428.

[3]李祥.深硅槽开挖工艺[J].微电子学,1993,23(2):39-43.

[4]赵玉印,欧文.深硅槽的刻蚀研究[C].北京:2003年10月第十二届全国电子束、离子束、光子束学术会议,2003:242-243.

[5]唐滨.用于MEMS封装的深硅刻蚀工艺研究[D].天津:天津大学,2012:9-10.

[6]王清平,苏韧.硅槽刻蚀技术中的源气体选择[J].微电子学,1994,24(6):65-68.

Trench of Reactive Ion Etching Technology Research

ZHAO Jinru,JIANG Dawei,CHEN Jie

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

The purpose of the study is to develop the process based on polysilicon etching process,Using CL2and HBR gas for trench etching.With experiments,adjusting the power,pressure,gas flow process window. with the helping of scanning electron microscope,checking the shape of the sidewall of the trench,analysis of the function of each parameters,the factors of affecting trench are obtained.Finally,a trench etching method which can be compatible with CMOS is obtained,successfully produced the depth of 6 μm,sidewall smooth trench,reseachedfor Semiconductorssuchasphotoelectric relayandsiliconcapacitor.

trenchetching;CL2;HBr;reactive ionetching;photoelectric relay;siliconcapacitor

TN405.98+3

:A

:1681-1070(2017)09-0041-03

2017-5-24

赵金茹(1983—),女,辽宁省海城人,2006年毕业于辽宁大学,现为中国电子科技集团公司第五十八研究所二部腐蚀工艺工程师,主要从事刻蚀工艺的研究与开发。