多主干鱼骨型时钟树结构的设计方法及优化

2017-09-11袁书伟钟传杰朱兆伟

袁书伟,钟传杰,朱兆伟

(江南大学 物联网工程学院,江苏省无锡214122)

多主干鱼骨型时钟树结构的设计方法及优化

袁书伟,钟传杰,朱兆伟

(江南大学 物联网工程学院,江苏省无锡214122)

为了使鱼骨型时钟树这种先进的时钟结构应用到大尺寸集成电路设计当中,针对现有鱼骨型时钟树存在的局限性和不足,总结出新的多主干混合型鱼骨型时钟结构设计方法和具体实现步骤。提出一种消除伴随鱼骨型时钟树存在的串扰噪音,并且尽可能减少时钟抖动的方法。结果显示多主干混合型鱼骨型时钟树性能比传统鱼骨型时钟树时钟偏差减少大约30%,主干周围的串扰噪声几乎能够完全消除,时钟抖动有明显改善。将多主干鱼骨型时钟树结构应用在大尺寸集成电路设计当中,不仅能够减少时间偏差从而更好地收敛时序,同时还能够节约大量绕线资源、降低噪音。

多主干;时钟偏差;时钟抖动;串扰;鱼骨型;噪音

1 引言

随着工艺尺寸的日益减小、功能的日益复杂,芯片中门的数目也呈指数增长。由于负载的增加,传统的二叉型时钟树无法满足芯片的时序要求,直接影响到芯片性能[1]。芯片能达到的最高工作频率与时钟网络构架的好坏息息相关。二叉型时钟树是过去多年使用最频繁的时钟网络[2],它具有实现时间短,操作方法简单的特点。但要实现二叉树时钟树,会在时钟树网络结构中插入大量缓冲器,而且布局比较分散,这样会带来高功耗的问题[3],更重要的是OCV(On Chip Variation)难以避免会发生[4],这会增加各条时钟通道的不确定性,导致时序不能收敛。为了避免以上缺点,有人提出了鱼骨型时钟树的概念,该方法是指用大量驱动器形成的multidriver并行驱动主干,再由主干驱动支干,最后由支干驱动整个设计模块的负载[5]。后来为了鱼骨型时钟树能更为灵活地运用在各种设计模块中,又有人提出了混合型时钟树的概念,即将鱼骨型时钟树和二叉树性时钟树相结合[6]。但是随着芯片门数以及面积的增加,负载的分布更加分散,同一条支干上的cell时钟延迟相差较大,传统的鱼骨型时钟树不再适合,于是在现有鱼骨型时钟树特点的基础上提出了多主干鱼骨型时钟树的概念。由于鱼骨型时钟树主干本身具有极强的电流,极容易对其附近的金属线产生串扰噪音,所以一般在设计的时候,鱼骨型时钟树主干周围50μm不会布线,降低了芯片面积的利用率,在多主干鱼骨型时钟树的框架下,这种弊端尤为明显,因此提出了降低串扰影响的方法。

2 改进后的多主干鱼骨型时钟树

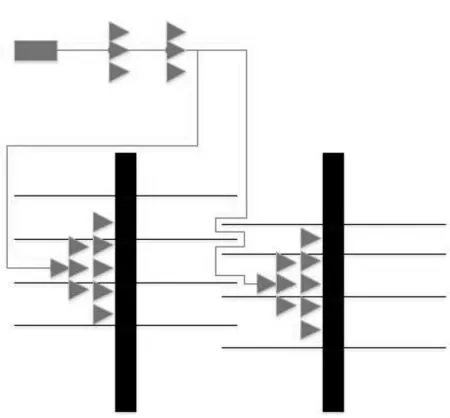

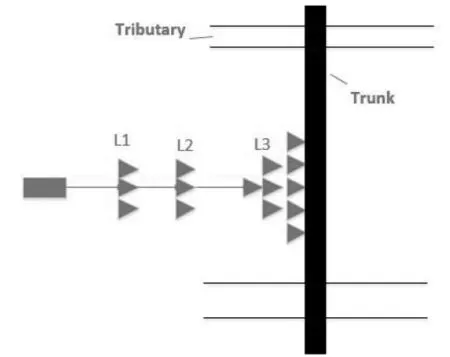

结构如图1,多主干鱼骨型时钟树是在传统单骨干的基础上再增加多条金属主干,这样能够在覆盖所有负载的同时,把支干控制在500μm以内,减少同一条支干上负载的时钟延时差。只有在设计模块足够大的时候,多主干型的结构才显得非常有必要。当设计模块过小时,多主干结构反而会严重增加功耗,而对于时钟性能没有明显提升。

图1 多主干鱼骨型时钟树

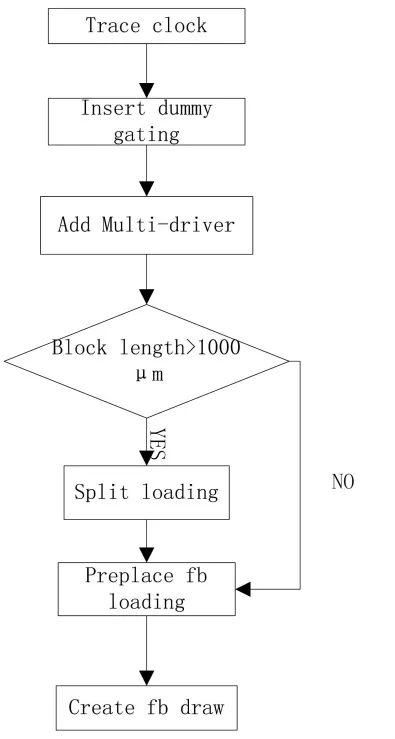

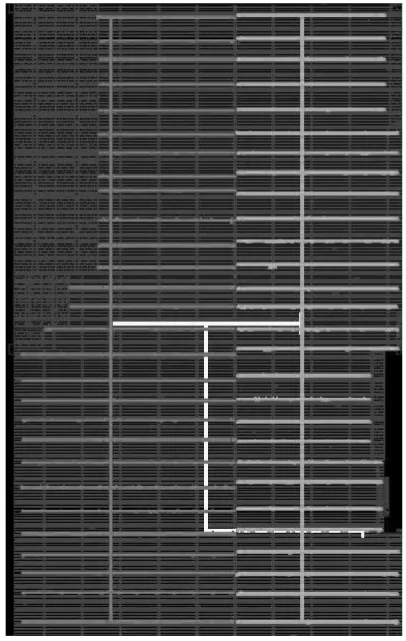

图2 多主干鱼骨型时钟树的实现流程

3 多主干鱼骨型时钟树的实现

实现步骤如图2所示。

(1)利用pritime time软件trace clock,将时钟结构画出来,找出网表中最长的clockpath的flipflop(触发器)级数,这里以最长4级为例。

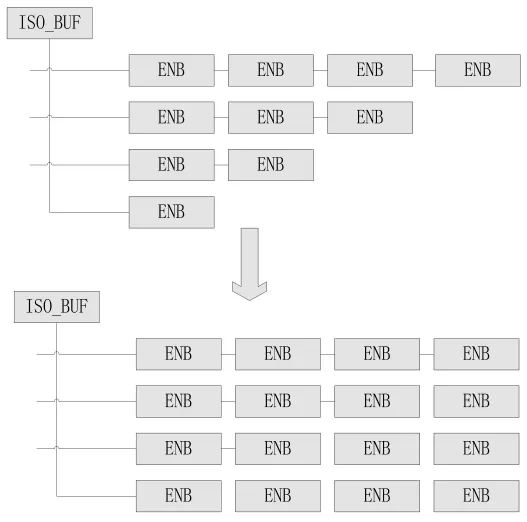

(2)在不足4级的flipflop前面插上dummy gating,这里使用BUF_X1B_A8TR作为dummy gating。为了保证从iso_buf到每个flipflop的时钟延迟相差最少,减少由于级数不同造成的skew,如图3。

图3 insert dummy示意图

图4 添加multidriver示意图

(3)添加 multidriver

如图4,Multidriver采用多个缓冲器并联的方式驱动主干,在获得足够驱动能力的同时又能将缓冲器固定在同一个区域,减少OCV的影响。由图中可以看出本设计采用的是三级驱动,L1由7个缓冲器组成,L2是8个,L3则是15-60个,具体取决于负载(loading)的大小,通常需要从库文件中提取寄生参数计算而得[7]。

(4)split loading

在设计模块长度大于1000μm时,可以考虑采用多主干鱼骨型时钟树,那么在此之前需要先按照负载在设计模块中的位置将负载分离开,根据就近原则选择连到不同的主干上。

(5)preplace fb loading

将分布在各个区域的负载拉到支干周围,方便连接。

(6)create fb draw

画出fishbone的金属层。到这里就完成了整个鱼骨型时钟树的绘制。由于主干和支干较长,为了避免同一条主干或者支干时钟延时差异过大,绘制过程中各个主干的宽度应该至少是信号线宽度的4倍,支干的宽度至少是信号线宽度的2倍,以此提高传输速度。如图5

图5 鱼骨型时钟树绘制后效果图

4 多主干鱼骨型时钟树crosstalk的优化

由于FB trunk上的强电流会对周围的信号线产生串扰干扰[6],多主干鱼骨型尤为明显。传统的处理方案有两种:

(1)将trunk放在没有signal绕线的power层。

(2) 在 trunk周围 1.5μm之内打上 routing blockage,阻止信号线绕在blockage内部。

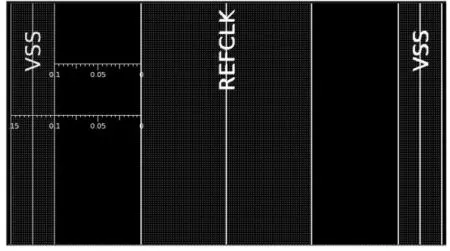

在多主干情况下,第一种方法会影响到电源的输入,造成IR drop问题,进而影响门的逻辑关系[9],造成Formality失败;第二种方法会严重浪费绕线资源。这里提出一种新的方法:在trunk周围打上一层接地的VSS线,作为时钟主干的保护环,同时也保护了环之外的信号线,如图6。这样可以有效减弱串扰带来的影响,同时不浪费绕线资源。图中可以看出主干外0.2μm就可以绕线了,比不打VSS环的1.5μm节省了1.3μm的绕线空间,这在当今14nm工艺尺寸下是非常宝贵的。

图6 VSS ring的布线示意图

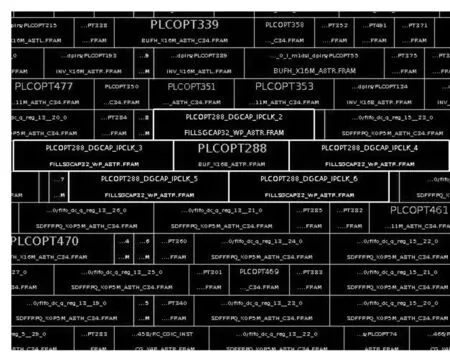

图7 cap cell放置示意图

5 对于FB结构时钟抖动的优化

对于时钟来说,jitter(抖动)不可避免,但jitter的存在会增加时钟的不确定性,可能造成时序紊乱等结果[10],这里提出一种方法可以有效减少clock jitter。由于FB(鱼骨型时钟树)结构中buffer大多堆积在一起,增加了这种方法的可行性。如图7,在所有的clock buffer周围放置一圈Cap cell。

6 仿真结果及分析

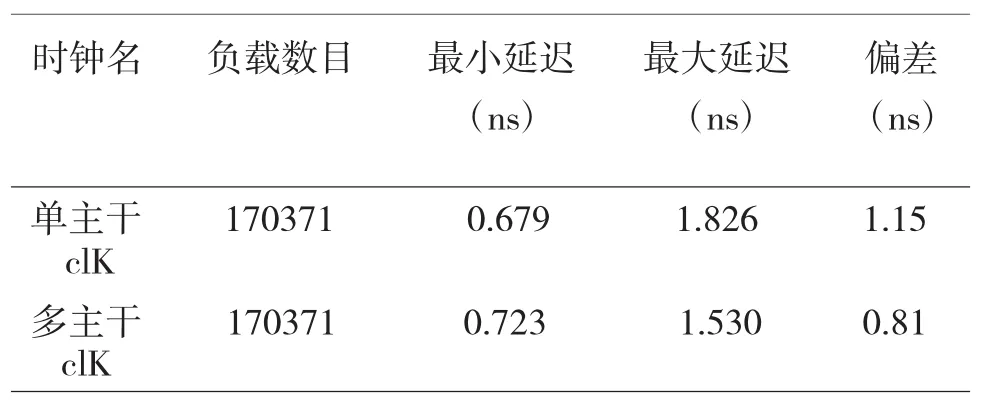

在一个1000*1000的block中,尝试了单主干和多主干两种FB结构,并且使用primetime软件得出两种时钟架构下的时钟偏差(skew),如下表可见,多主干型结构clock skew比单主干结构优化了接近30%。

表1 多主干与单主干时钟树性能比较表

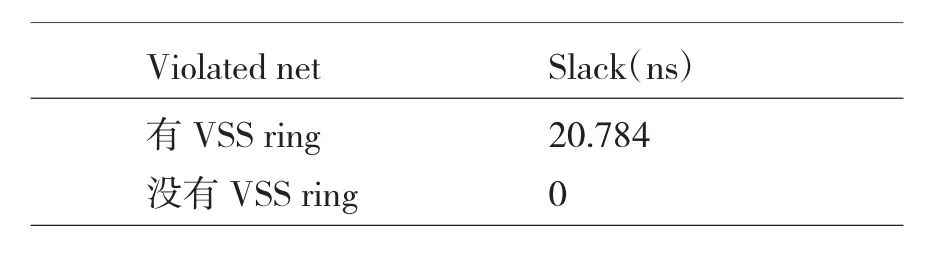

表2是在主干打上接地的VSS环前后,一根距离主干0.2 μm处线的cross talk情况:

表2 画VSS ring前后结果对照表

由表可知,VSS ring可完全消除距离主干0.2μm处的crosstalk。

7 结束语

在较大设计模块中,多主干鱼骨型时钟树能将时钟偏差减少30%,对于整个涉及模块后面的时序收敛大有裨益,有很高的实用价值。同时VSS环的布置能有效减少多主干带来的强电流串扰噪声的影响,从而节约绕线资源。

[1]崔茜,于忠臣.多时钟源分割方法在时钟树综合中的应用[J].中国集成电路,2014,06:32-36.Cui Xi,Yu Zhongchen.The Method of Multisource Using in Clock Tree Synthesis[J].China Integrated Circuit,2014,06:32-36.

[2]Hong-Ting Lin ,Yi-Lin Chuang ,Pulsed-Latch Utilization for Clock-Tree Power Optimization.IEEE Transactions on Very Large Scale Integration(VLSI)Systems[J],2014;22(4):721-733.

[3]阳若宁.一种低功耗集成电路的时钟分布策略[J].中南林业科技学报,2011,31(12):192-196 Yang Ruoning.A Low Power Clock Distribution Scheme on ASIC[J].Journal of Central South University of Forestry&Technology,2011,31(12):192-196

[4]陈祺,林平分,张玥.超大规模集成电路基于OCV的时序收敛方法[J].电子科技,2009,22(7):30-33.Chen Qi,Lin Pingfen,Zhang Yue.A Method of Timing Closure Based on OCV in the VLSI Design[J].Electronic Science and Technology,2009,22(7):30-33.

[5]陈菲菲,王振宇,严伟.鱼骨型时钟树的快速实现方法[J].微电子学与计算机,2014,02:153-156.Chen Feifei,Wang Zhenyu,Yan Wei.Fast Implementation of Fishbone Structure [J].Microelectronics& Computer,2014,02:153-156.

[6]杨贺,严伟.点接鱼骨型时钟网路设计[J].微电子学与计算机,2016,33(7):11-14.Yang He,Yan Wei.Fishbone of Built on Clock Network Points[J].Microelectronics&Computer,2016,33(7):11-14.

[7]张岩,杨银堂.一种新型分布式互连线功耗优化模型[J].西安电子科技大学学报,2014,04:36-40.Zhang Yan,Yang Yintang.Novel Distributed Optimal Interconnection Power Model[J].Journal of Xidian University(Natural Science),2014,04:36-40.

[8]张玲,王澧.百万门系统级芯片的时钟树设计[J].电子与封装,2014,12:21-24.Zhang Lin,Wang Li.Clock Tree Design Process for SoC[J].Electronics and Packaging,2014,12:21-24.

[9]何湘君.基于SOC低功耗设计的IR drop分析[D].西安:西安电子科技大学,2015.He Xiangjun.Reasearch on IR Drop Analyse of SOC Low Chip Design[D].Xidian University,2015.

[10]杨小军,陈曦,张庆民.时钟抖动对ADC变换性能影响的仿真和研究[J].中国科学技术大学学报,2005,32(1):66-73.Yang Xiaojun,Chen Xi,Zhang Qingmin.Simulation and Research of the Effect Caused by Clock Jitter on ADC Conversion[J].Journal of University of Science and Technology of China,2005,32(1):66-73.

Design and Optimization of Multi-trunk Fishbone Clock Tree Structure

Yuan Shuwei,Zhong Chuanjie,Zhu Zhaowei

(School of Internet of Things,Jiangnan University,Wu Xi 214122,China)

To apply fishbone structure in some big size chips,on the weakness of existed fishbone clock structure,the thesis concluded a new multi-trunk fishbone clock structure and design steps.Then it proposed a way to eliminate crosstalk noise between nets,and reduce clock jitter.The result shows the clock skew from this new multi-trunk can improve about 30%and crosstalk can be removed the mostly.Applying the fishbone structure in big size chip can decrease clock skew to meet timing,meanwhile can save a lot of routing resource and lower noise.

Multi-trunk;Clock skew;Clock jitter;Crosstalk;Fishbone;Noise

10.3969/j.issn.1002-2279.2017.04.005

TN4

A

1002-2279-(2017)04-0016-04

袁书伟(1990—),男,江苏省南通市(海安县)人,硕士研究生,主研方向:数字集成电路物理设计。

钟传杰(1959—),男,江苏省徐州市人,教授,博士,主研方向:新型半导体器件,微电子系统及专用集成电路设计。

2016-11-08