基于J750的MCU芯片测试程序开发与调试

2017-09-11谭雪,金兰

谭 雪,金 兰

(北京确安科技股份有限公司,北京 100094)

基于J750的MCU芯片测试程序开发与调试

谭 雪,金 兰

(北京确安科技股份有限公司,北京 100094)

Teradyne J750测试系统功能强大、测试精度高,是全球装机量最大的自动测试设备。以一款MCU芯片的晶圆级测试为例,主要阐述了其在美国Teradyne公司生产的J750大规模集成电路测试系统上的测试方案开发与实现。介绍了J750测试系统的主要特点,开展晶圆级测试开发的一般步骤:包括测试设备评估、测试适配器加工、离线程序编写、在线测试程序调试等。程序部分主要关注功能项和频率计数测试,对调试异常情况进行研究等。通过开展16site并完成整枚晶圆的测试,根据探针台生成的Map文件,可以查看到该圆片的批号、片号、测试坐标及对应管芯的测试结果表征值,即Bin值。

MCU芯片;J750测试机;晶圆;TDS软件;功能测试;频率计数

1 引言

目前MCU芯片广泛应用在各个领域中[1],为保证芯片的质量和可靠性,需要对其电学特性和逻辑功能等进行测量和检验。这里以一款MUC芯片为例,开展晶圆级测试,介绍其在Teradyne J750平台上的测试方案的开发与实现。

2 测试系统及芯片介绍

Teradyne J750是全球装机量最大的自动测试设备。它具有丰富的数字通道资源,最高时钟频率150MHz,100MHz全格式化的驱动和接受能力[2];最大配置有512个通道或1024个通道,一块电路板上集成有64通道;每通道为每引脚提供独立的驱动时序和电平;每通道有4M或16M字节的图形存储深度;扫描深度是769M位或3G位;每通道配备独立的参数测量单元;配有高压驱动通道;支持32site并测[3]。在软件方面,Teradyne J750选用微软公司的通用Windows NT平台,及Excel软件和Visual Basic语言,开发成功IG-XL测试软件包。Teradyne J750测试系统可以进行多种测试,例如:扫描测试、A/D和D/A测试、RFID测试等[4]。

本MCU芯片是一款8位高性能、高效率的混合信号微控制器。MCU核具有8位8051兼容的MCU,运行速度比标准的8051快3倍。4个时钟长度的指令周期,相对标准8051,平均指令执行时间缩短2.5倍。双数据指针。位操作指令。内部存储有可编程的4K Byte OTP ROM。芯片IO端口具有上拉功能,同时芯片还有外部ADC输入、内部电池检测,内部和外部双时钟系统等。本次主要开展晶圆级测试,主要关注功能测试和频率计数测试。

3 晶圆级测试步骤

开展晶圆级测试的步骤包括:测试设备评估,测试适配器加工,离线程序编写,在线程序调试,验证开发结果等。下面分别进行介绍。

3.1 测试设备评估

本芯片开展晶圆级测试,将要用到测试机和探针台两种设备,测试之前需评估将要使用的测试机及探针台资源是否满足该管芯测试,这里选用J750测试机和UF3000探针台,采用将测试机直接扣在探针台上的连接方式,即Direct docking,进行16site并测。

3.2 测试适配器加工

探针卡在晶圆级测试中用于连接测试机电路和管芯上的Pad,使测试机的信号通过弹簧针连接到探卡底部的Pad上,再由探卡上的布线连到被测的管芯上[5]。测试负载板是一种连接测试机的测试头和被测器件的接口板,被固定在探针台上。这里以中测探针卡为例设计加工J750测试适配器、探针卡和测试负载板。考虑到出针分层与制作难度等因素,探针卡为1×16排列方式的悬臂探针卡。

3.3 离线程序编写

3.3.1 使用TD S转换成A TE可用的向量

根据被测芯片的测试规范编写离线测试程序,这里主要关注功能测试及频率计数测试。编写功能测试项前,因ATE测试向量与EDA设计仿真向量不同,首先需要利用TSSI软件将原始波形文件转换成能被测试机接受的波形文件。

TSSI测试软件目前有TDS系列(命令行界面),TD(图形界面),DVT,TVT几款产品。这里使用TDS进行向量转换,因其功能强大,可依需求调整仿真波形图以符合测试机的要求,经过良好转换的向量格式,可以被相应的测试机接受。

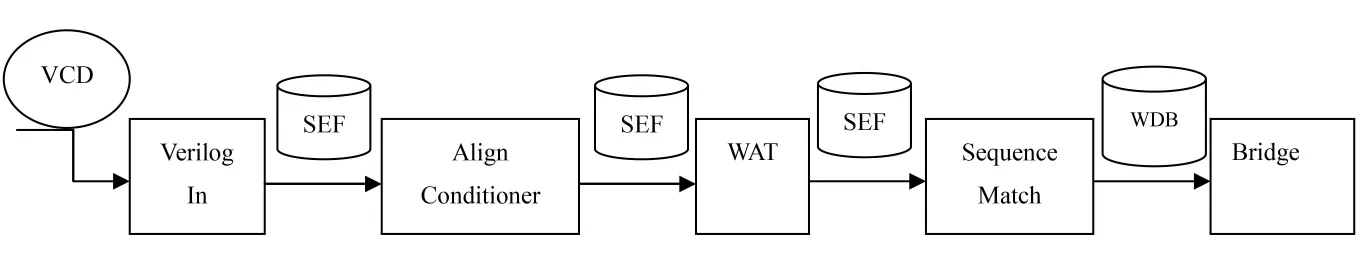

使用TDS进行转换步骤:使用Verilog仿真得到VCD格式的文件,需要先对齐边沿,例如只有一种时间集合测试机,在一对驱动和比对事件间会有一周期的高阻时间,如果测试机没有抑制返回功能,那高阻时间就需要与测试机的周期边界对齐。WAT是波形分析工具,它能使仿真数据可视化,它也会自动生成时间模板。当主要的时间模板通过WAT生成后,需要将输出连到序列匹配以生成一个完整的WDB用于最后转成目标测试机的格式。WDB是一组TSSI二进制波形数据集,包含信号、时钟、波形、向量等信息。经过以上步骤可以得到符合测试机的向量。使用TDS进行转换的流程如图1所示:

图1 使用TDS进行转换的流程

3.3.2 编写探针台程序

用探针台进行晶圆测试时,还要设定探针台的工作参数,编写探针台程序。如:晶圆直径、测试方式,Z方向的分离高度等,使用户可以通过软件界面控制测试设备,操纵探针的升降和移动等。

3.4 在线测试程序调试

3.4.1 搭建测试环境

当测试机、探针台、探卡和程序就位后,就可以开始使用样片进行在线程序调试。首先将测试机与探针台连接,再将探针卡放在测试负载板上进行TDR以保证在信号传输路径上阻抗的连续性,避免信号产生大的反射。接着把晶圆安装在晶圆承片步进台上,晶圆承片步进台将进入探针测试台中心,经系统的CCD显微摄像装置扫描找准后,X-Y二维步进工作台移动定位到测试探针阵列对准晶圆上芯片的位置,升降Z轴,使探针和芯片接触。然后,探针台受启动测试信号的控制,就可以测试晶圆了。

3.4.2 功能测试

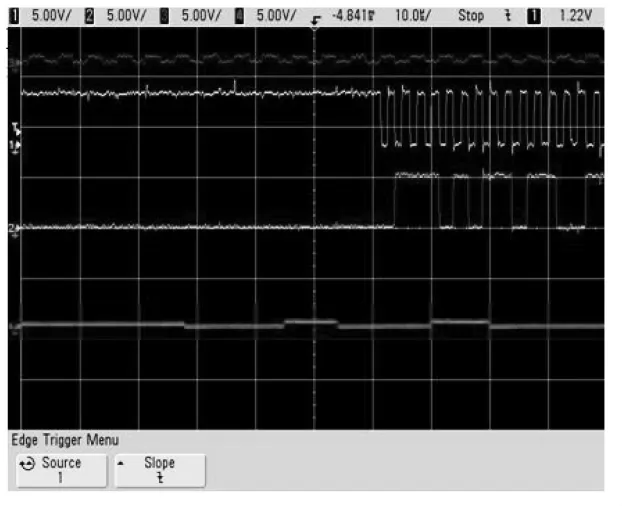

功能测试主要测试一个端口的脉冲从而检测ADC功能。所用pattern为使用TDS转换后的pattern。图2为程序调试后在示波器上观察到的输入和输出信号的波形,其中,紫色波形代表CPU时钟,黄色波形代表PCK,绿色波形代表数据流,红色波形为输出端口的波形。CPU时钟同步于PCK,频率为PCK的二分频。从开始工作到PCK的输出,CPU时钟输出的时钟个数应该为4倍个PCK的时钟周期。这样一来,4个时钟长度的指令周期,相对标准8051,平均指令执行时间缩短2.5倍。串行指令数据流从显示绿色波形的端口输入,串行指令数据流的同步时钟从PCK端口输入。指令数据为3个8位二进制为一组,双数据指针,位操作指令,运行速度比标准的8051快3倍。在指令数据中将高低电平测试、频率计数测试和检测ADC状态的功能测试整合到一起。在不同的位置设置不同的指令,如在指令开始时先为控制ADC的指令,主要启动ADC工作。红色波形为输出信号的波形,从波形图上看,采集到了正确的波形,运行pattern后,此测试项调通。

图2 调试中在示波器上观察到的输入、输出信号的波形

3.4.3 频率计数测试

频率计数测试通过VBT代码实现。代码包含初始化频率计数器和测量频率两部分内容。其中,初始化频率计数器在pattern运行前起清空及初始化计数器的作用。测量频率则将读回测试结果,计算频率并记录结果。

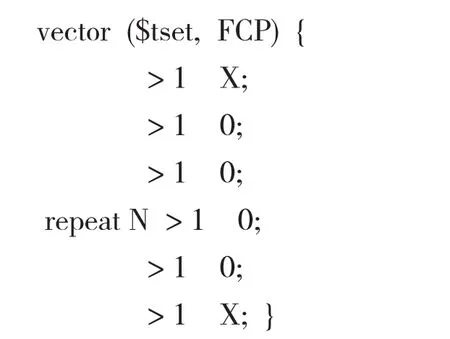

频率计数器模式设置只适用于扩展模式,编程时要声明此引脚使用频率计数器模式。在此模式下的管脚在时间集合中需要选择频率计数器模式。Pattern中只能使用0和X两种数据字符,0和X不再是其通常的意义,在这里它们能控制频率计数器窗口的开启和关闭,多于2个周期的一对数据码才能打开或关闭窗口,因为频率计数器的数据码作用在R0或R1时钟沿[6]。

频率计数器数据码的填写样例如下:

3.4.4 调试异常情况

在程序调试时发现输出信号的杂波较多,为避免输出的毛刺导致测试误判,寻找解决办法试图使毛刺减少。首先排查原因,查看探头是否接对,经检查探针接测试点,鳄鱼夹接地,没有反接。然后尝试给输出管脚加1nF的滤波电容。滤波电容多用于直流电路中,引入滤波电容的原因是要获得平滑稳定的电压,因为电容两端的电压不能突变,所以它能抑制电压的波动,使其变得平稳光滑。图3为加输出滤波电容前后的对比图,上图为加滤波电容前的输出信号波形,下图为加滤波电容后的输出信号波形。可见给输出管脚加电容可以有效帮助抑制杂波。

图3 加输出滤波电容前后的对比图

3.4.5 测试整枚晶圆

另外,这里还进行了电气参数测试,如连接性测试、功耗测试及输出电压测试等,不赘述。将直流参数测试项和功能项组成的一个流程进行单个测试位测试,测试通过。然后进行多点测试。多数ATE的操作系统允许一个程序对应一个芯片的测试,并用复制方式自动扩展这个程序进行多个芯片的同时测试[7]。本项目开发时在同一时间里测试16个管芯,16个测试位间测试结果稳定通过。

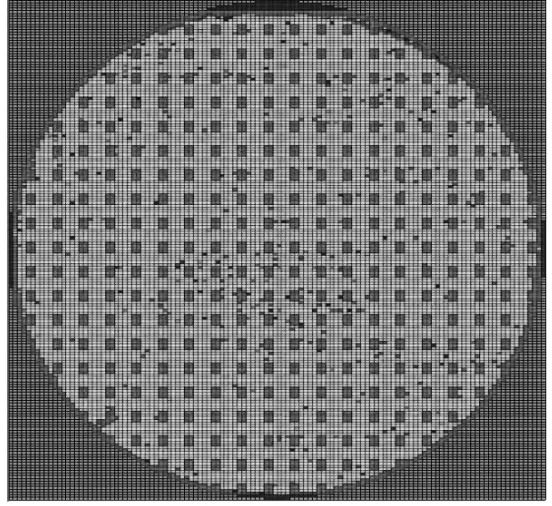

一个制造过程的过程良率可定义为可接受的部分与所有加工的部分之比,过程良率简称为良率[8]。测试整枚样片后,探针台将生成Map文件,Map文件是记录一片圆片的批号、片号、测试坐标及对应IC的Bin值(测试结果表征值)的文本文件[9]。图4为测试整枚晶圆后的map图,圆片共有17583个管芯,其中3303个管芯不需测试,见map图中规律性的红色区域。剩余14280个管芯为本次实际要测试的,其中好品有13935个,好品标记为绿色,良率为97.58%,可见此片圆片的好芯片较多。

图4 测试整枚晶圆后的结果

4 结束语

该MCU芯片可被广泛应用在电子测量仪器、环境监控、手持式测量工具、家庭应用、电子控制工具、马达控制等场合。Teradyne J750测试系统功能强大、测试精度高,应充分利用,不光针对数字电路,还可测试存储器、模/数和数/模转换器及功能复杂的SOC。这里仅以MCU芯片为例简要介绍晶圆级测试的一般开发过程。

[1]Bushnell,M.L.超大规模集成电路测试-数字、存储器和混合信号系统[M].北京:电子工业出版社,2005.Bushnell,M.L.Essentials of Electronic Testing for Digital,Memory,and Mixed-Signal VLSI Circuits[M].Beijing:Electronic Industry Press,2005.

[2]张磊,张振华,杨纯辉,等.Teradyne UltraFLEX的测试程序调试[J].微处理机,2012,33(6):6-8.Zhang Lei,Zhang Zhenhua,Yang Chunhui.etc.Testing Program Debugging of Teradyne Ultra FLEX[J].Microprocessors,2012,33(6):6-8.

[3]魏志刚,徐居明,吴丽.基于J750测试系统的HS3282发送功能测试[J].现代测量与实验室管理,2010,18(4):14-16.Wei Zhigang,Xu Juming,Wu Li.etc.Test of HS3282 Transmission Function Based on J750 Test System[J].Advanced Measurement and Laboratory Management,2010,18(4):14-16.

[4]龙永佳.基于J750的SRAM测试程序开发和调试[J].现代测量与实验室管理,2012,20(2):12-13.Long Yongjia.Development and Debugging of SRAM Test Program Based on J750[J].Advanced Measurement Laboratory,2012,20(2):12-13.

[5]陈国强,吴国华,刘敬猛.中规模集成电路功能测试仪的设计[J].电子技术应用,2009,35(7):139-141.Chen Guoqiang,Wu Guohua,Liu Jingmeng.Design of Function Testing Instrument for Medium Scale Integrated Circuit[J].Application of Electronic Technique,2009,35(7):139-141.

[6]匙雅琳.Teradyne J750数字信号测试机上实现混合信号测试[D].天津:南开大学,2006.Shi Yalin.Implementation of Mixed Signal Test on J750 Teradyne Digital Signal Test Machine[D].TianJin:NanKai University,2006.

[7]杨婷.基于片段间转移低功耗测试结构研究与实现[D].湖南:湖南大学,2007.Yang Ting.Research and Implementation of Low Power Test Structure Based on Inter Segment Transfer[D].HuNan:HuNan University,2007.

[8]孙曦东,马云松,耿爽等.在Teradyne J750上的测试程序调试.微处理机,2008,29(2):36-37.Sun Xidong,Ma Yunsong,Geng Shuang.etc.To Debug the Testing Program on Teradyne J750[J].MicroProcessors,2008,29(2):36-37.

[9]胡兆华,王厚军.圆片级IC测试中脱机打点的一种实现方法[J].仪器仪表学报.2005,26(Z2):482-483.Hu Zhaohua,Wang Houjun.An Implementation Method of Wafer Level in IC Testing In Offline Management[J].Chinese Journal of Scientific Instrument.2005,26(Z2):482-483.

Developing and Debugging of MCU Chip Test Program Based on J750

Tan Xue,Jin Lan

(Chip advanced Co.,Ltd.,Beijing 100094,China)

Teradyne J750 test system is a automatic test equipment with world's largest installed capacity because of its powerful function and high test precision.Here takes a wafer test of MCU chip as an example,mainly expounds the develop and implement of a test method used on a LSI testing system from Teradyne company.The main features of J750 test system is recommended,and the general steps of developing and debugging of test program in wafer test is descripted,including evaluating test equipment,processing test adapter,off-line programming and debugging online testing procedures,etc..The program part mainly focus on the function test and frequency counter and research on debugging abnormalitis.After testing the whole wafer by carrying out 16site,it can show the wafer piece number,batch number,coordinate and bin value,according to the Map file generated by the prober.

MCU chip;J750 tester;Wafer;TDS software;Function test;Frequency counter

10.3969/j.issn.1002-2279.2017.04.007

TN47

B

1002-2279-(2017)04-0023-04

谭雪(1985—),女(回族),北京通州人,硕士研究生,主研方向:IC测试。

2016-11-23