C8051F系列微控制器UART电路设计

2017-09-11孙静

孙 静

(中国电子科技集团公司第四十七研究所,沈阳110032)

C8051F系列微控制器UART电路设计

孙 静

(中国电子科技集团公司第四十七研究所,沈阳110032)

介绍C8051F系列UART的功能结构和传输数据帧的格式,通过其操作模式和两种典型的通信方式,详细分析UART内部特殊功能寄存器的功能和使用方法,阐述发送部分和接收部分电路设计过程,通过特定程序对内部特殊功能寄存器的标志位,发送、接收端口时序以及多机通信过程进行仿真,并给出仿真波形图。

C8051F系列;异步串行接口;特殊功能寄存器;多机通信;仿真波形;仿真程序

1 引言

UART由于操作简单,信号线少,抗干扰强,传输距离较远等优点被广泛地应用在工业、通信和家电控制等嵌入式领域。目前人们对UART的认识仅仅是各种手册的文字描述,通过在线调试和示波器监测等手段亦不能显示传输过程中每个时刻内部寄存器的变化情况。如果在数据传输的同时能观察到内部寄存器的变化就能解决上述问题,这样有利于编程人员更深入的了解UART的工作原理,因此从集成电路设计出发,重点从UART的内部介绍其电路工作原理及时序的产生。

2 寄存器功能描述

UART包括六个特殊功能寄存器。串行口波特率控制寄存器SBCON0、波特率分频系数寄存器SBRLH0、SBRLL0,三个寄存器用于设定系统通讯波特率。串行口控制寄存器SCON0和串行口模式选择寄存器SMOD0用于设置通讯数据位数,如校验位、停止位等。SBUF0是用一个地址访问两个不同的寄存器,一个用于只读,另外一个用于只写。如C程序中,x=SBUF0,则读取接收缓冲寄存器;SBUF0=0x55,则是写发送寄存器[1-3]。

串行口控制寄存器(SCON0)的每一位定义如下:

SCON0.7接收FIFO溢出标志,符号为OVR0。0:没有溢出,1:有溢出。

SCON0.6奇偶错误标志,符号为PERR0。0:没有错误,1:有错误。

SCON0.5发送保持寄存器空标志,符号为THRE0。0:标志非空,1:标志空。

SCON0.4接收使能,符号为REN0。0:禁止接收,1:允许接收。

SCON0.3发送附加位,符号为TBX0。

SCON0.2接收附加位,符号为RBX0。

SCON0.1发送中断标志,符号为TI0。0:没有发送中断,1:有发送中断。

SCON0.0接收中断标志,符号为RI0。0:没有接收中断,1:有接收中断。

串行口模式寄存器(SMOD0)的每一位定义如下:

SMOD0.7多机通信使能,符号为MEC0。0:stop位为1时接收,1:stop和extra位都为1时接收。

SMOD0.6,SMOD0.5校验类型选择,符号为S0PT[1:0]。00:奇校验,01:偶校验,10:标记校验,11:空格校验。

SMOD0.4校验使能,符号为PE0。0:不使能,1:使能。

SMOD0.3,SMOD0.2数据长度选择,符号为S0DL[1:0]。00:5 位,01:6 位,10:7 位,11:8 位。

SMOD0.1附加位使能,符号为XBE0。0:不使能,1:使能。

SMOD0.0停止位长度选择,符号为SBL0。0:1位停止位,1:2位停止位(数据长度 6,7,8),1.5 位停止位(数据长度5)。

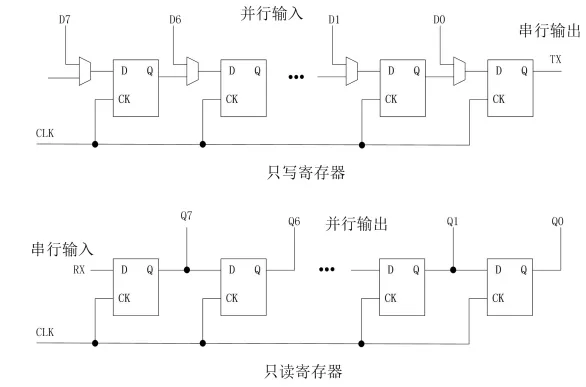

接收、发送缓冲寄存器(SBUF0)

SBUF0寄存器是一个地址访问两个寄存器,一个为只写寄存器(发送移位寄存器)和一个只读寄存器(接收锁存寄存器),其结构图如图1所示。

波特率控制寄存器(SBCON0)的每一位定义如下:

图1 SBUF0结构图

SBCON0.6波特率发生使能,符号为SB0RUN。0:不使能,1:使能。

SBCON0.1,SBCON0.0波特率预分频选择,符号为 SB0PS[1:0]。00:12 分频,01:4 分频,10:48 分频,11:1 分频。

其它位是预留位,必须写0。

波特率高字节重装载寄存器(SBRLH0)

当波特率计数器溢出时,重新装载计数器的高字节。

波特率低字节重装载寄存器(SBRLL0)

当波特率计数器溢出时,重新装载计数器的低字节。

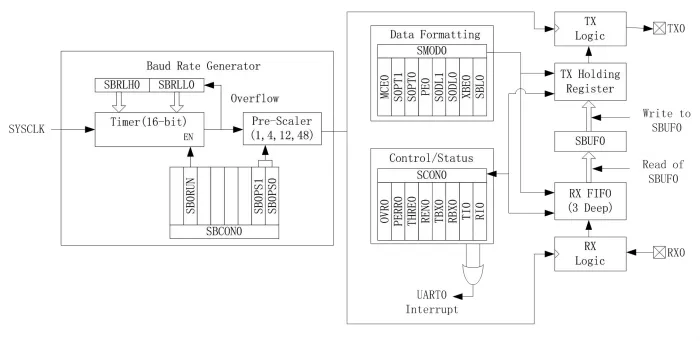

3 基本结构和功能描述

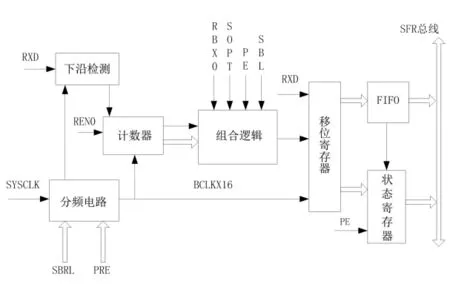

UART是异步全双工串行接口,结构框图如图2所示:

图2 UART结构框图

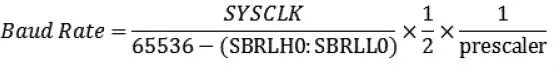

设备通讯过程中,设定同一波特率才可以进行正确的数据传输,C8051F系列单片机UART工作的波特率按照以下公式计算:

SYSCLK为系统时钟工作频率;(SBRLH0:SBRLL0)为分频系数寄存器0000-FFFF的设定范围;prescaler为预分频系数,有以下四个固定分频系数:1,4,12 和 48。

每一帧数据包括起始位、数据位 (低位D0在前)、校验或附加位(可选)、1或2位停止位,数据长度可以在5位到8位之间调节。校验位在数据位之后,按照S0PT[1:0]位选择由硬件自动生成,停止位长度由SBL0位选择。要注意的是当校验位使能时附加位失效[4]。其时序图如图3所示。

图3 串行口时序图

CPU内核写SBUF0寄存器立即启动数据发送操作,数据通过发送移位寄存器从TX0端口串行输出,发送完毕后TI0置1。REN0置1后,UART模块允许接收,数据从RX0端口串行输入,如果接收到停止位是1的数据存入接收FIFO中,FIFO的深度是3,FIFO满后下一个接收数据丢失。接收完成后RI0置1,如果MCE0为1,RI0只有在附加位等于1时置1。SBUF0寄存器中存储的是最先接收的数据,读SBUF0存储在FIFO中的下一个字节被装载到SBUF0中,FIFO中释放的空间用于接收新的字节。只有在FIFO空时,RI0才可被软件清零。

UART通信模式可分为点对点和多机通信两种模式。点对点通信只需要串行总线上有两个设备,MCE0位需要清0。设备A的TX0与设备B的RX0连接,设备A的RX0与设备B的TX0连接。UART支持一个主机和多个从机之间的通信。多机通信时主机的TX0与从机的RX0连接,从机的TX0与主机的RX0连接。

4 电路设计

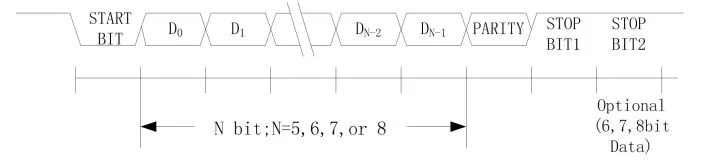

4.1 接收部分电路设计

当REN0使能后,接收电路开始采样,电路主时钟采样到RXD管脚出现下降沿后,即按照所设定的波特率在数据位的中间位置进行采样,并保存到移位寄存器。数据移位过程中,根据寄存器设置判断数据是否接受完毕,正确接收到停止位后,数据被转移到接收FIFO,如RI0寄存器位被置成1,表示数据接收完毕,如果FIFO满则OVR0被置位。如果软件设定接收校验位,则硬件电路自动检查校验位是否正确,校验有误后PERR0会被置位[5-6]。接收电路示意图如图4所示。

图4 接收电路示意图

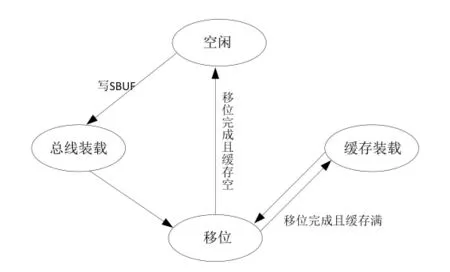

4.2 发送部分电路设计

发送数据有一级缓存,如果当前的数据没有发送完成又写入下一个数据,这个数据先存放在缓存中,等当前数据发送完毕再进入SBUF0,然后串行输出。发送部分电路通过四个状态的相互转换实现发送功能,这四个状态分别是:空闲状态、缓存装载状态、总线装载状态和移位状态。发送状态机如图5所示:

图5 发送状态机

状态机在空闲状态时给出缓存空标志,THRE0位置1,TI0清0。当数据写入SBUF后,状态机进入总线装载状态,THRE0位清0。总线装载状态如果有数据写SBUF信号并且缓存为空,数据写入缓存中,同时给出缓存满标志,数据装载完毕后自动进入移位状态。在移位状态,移位完成后如果缓存空,状态机进入空闲状态,THRE0位置1;如果缓存满,状态机进入缓存装载状态。移位完成标志由逻辑根据SMOD0寄存器设置计算生成,移位完成后TI0置1。移位过程中如果有写SBUF信号并且缓存为空,数据写入缓存中,同时给出缓存满标志。在缓存装载状态,缓存中的数据装载进移位寄存器后自动进入移位状态,同时给出缓存空标志。移位完成后TI0置1,标志发送完成。

5 仿真

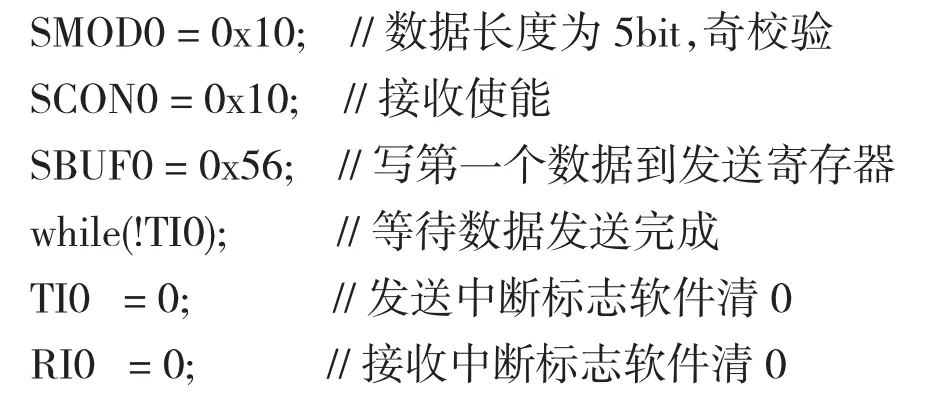

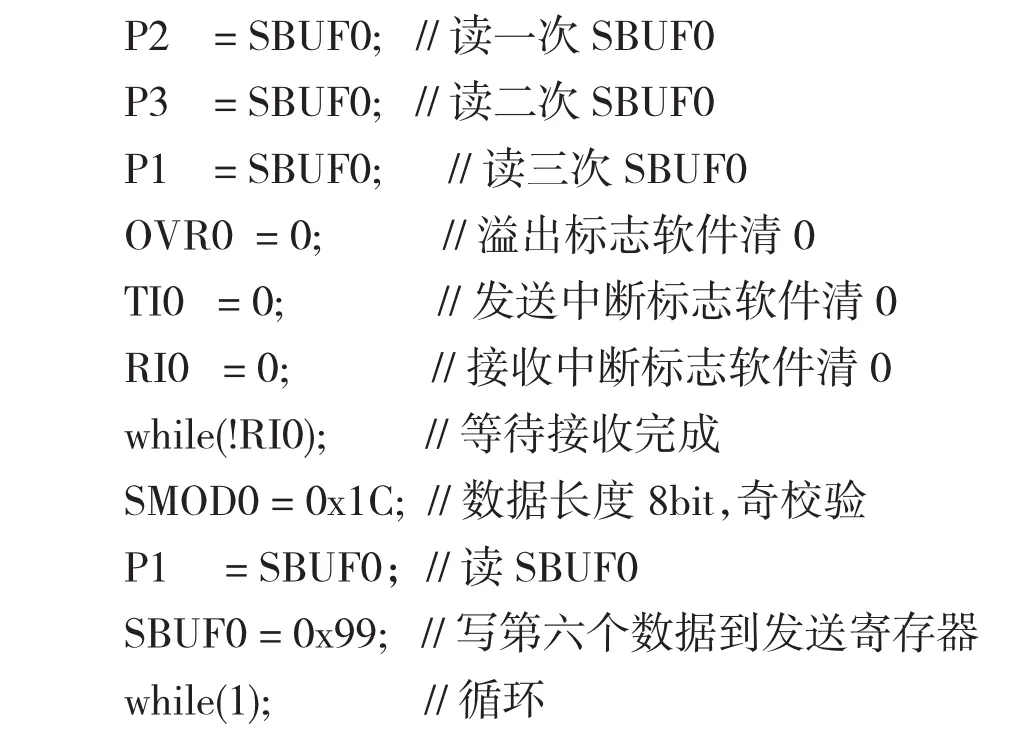

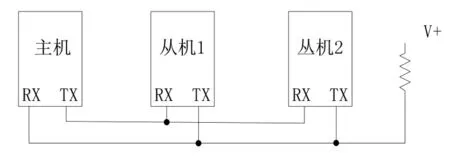

5.1 发送和接收时序仿真

根据UART的功能特点,选取5位带奇校验、6位带偶校验、7位带附加位、8位不带校验和8位带有错误校验的发送和接收模式进行仿真。将UART的TX0端口通过一个2选1的选择器与自身的RX0端口连接。用testbench制造一个错误的校验码,通过2选1的选择器的另一端与RX0端口连接。从TX0发送出的错误数据再被RX0接收,错误的校验码通过选择器接到RX0端口[7-8]。仿真程序如下:

UART发送和接收的时序以及内部寄存器状态的仿真波形图如图6所示。

图6 UART发送和接收仿真波形图

发送数据写入SBUF0后THER0清0(发送保持寄存器非空),发送完成后THER0置1(发送保持寄存器空),TI0置1,TI0是用软件清0的。第一、第二和第三个数据都是前一个数据发送完成后一个数据再写入。由于这三个数据分别是5位、6位和7位数据,因此TX0端口依次发送其低5位(0x16)、6位(0x26)和7位(0x66)数据。第四个数据没有发送完成第五个数据即写入,这时第五个数据(0x69)存入发送缓存TBUF中,待第四个数据发送完成后,第五个数据再被发送。接收端接收到的数据即发送端发送出的数据,第一、二、三个数据存入FIFO中。接收第四个数据引起接收FIFO溢出,OVER置1,第四个数据(0x68)丢失。每接收一个数据RI0置1,接收第二个数据后RI0不可软件清0。OVER置1后,连续读SBUF0三次,接收FIFO清空。因此第五个数据接收到FIFO中,将这个数据读出清空FIFO,这时再接收到的数据如果有校验错误PERRR0置1。第六个数据(0x99)的正确校验码是1,用testbench将接收端的这一位置成0,接收端即接收了一个带有错误校验码的数据,PERRR0置1。

图7 多机通信连接示意图

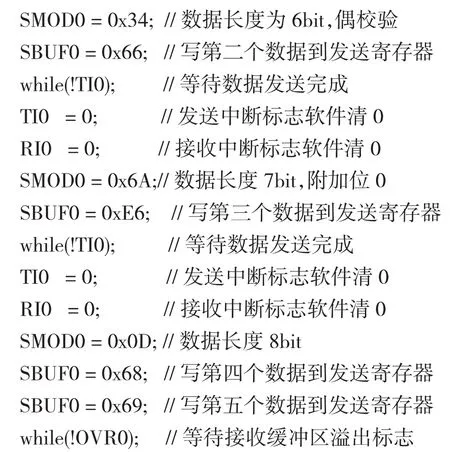

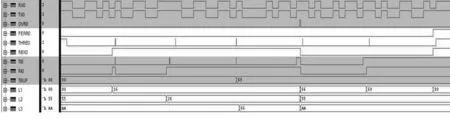

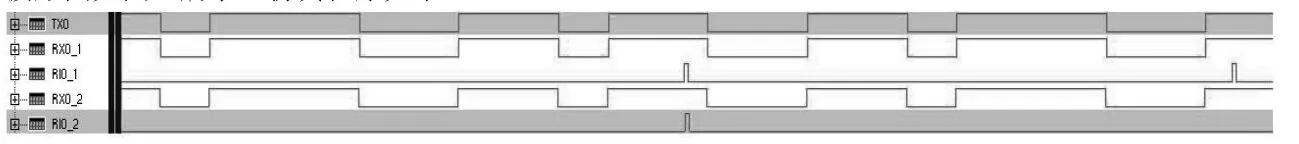

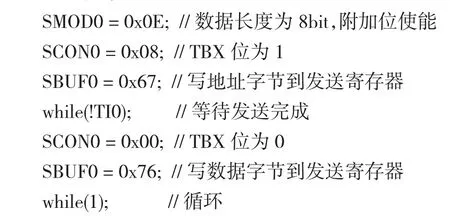

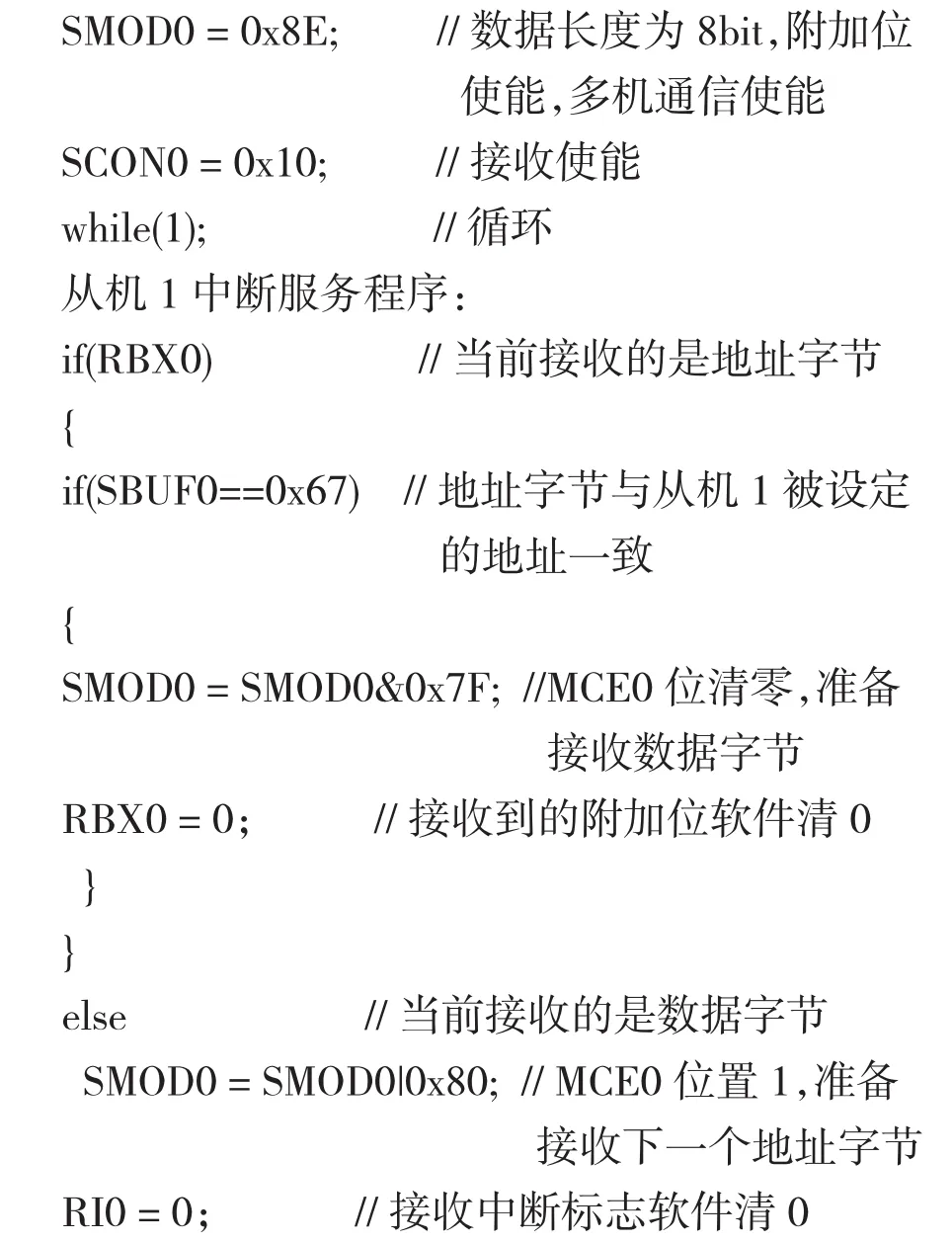

5.2多机通信仿真

多机通信连接示意图如图7所示,主机发送,从机接收。每次传输由两个字节组成,主机先发送地址字节0x67且TBX=1,从机1和从机2的MCE0位都置1,因此从机1和从机2都接收,RI0_1与RI0_2都置1。从机1被分配的地址0x67与接收到的地址一致,从机2被分配的地址0x68与接收到的地址不匹配,因此从机1的MCE0位被软件清0,准备接收第二个字节。从机2的MCE0位不变。主机再发送数据字节 0x76且 TBX=0,从机1(MCE0=0)接收,从机 2(MCE0=1)不接收,RI0_1 置 1,RI0_2 不置1,仿真波形图如图8所示。仿真程序如下:

图8 主机与2个从机通信仿真波形图

主机程序:

从机程序包括主程序和中断服务程序两部分,从机判断地址是否一致和MCE0位清零是通过中断服务程序完成的。从机1和从机2的主程序是一致的。

从机程序:

从机2的中断服务程序与从机1的中断服务程序与只有判断地址处不同即SBUF0==0x68。

6 结束语

展示了UART的内部结构,总结归纳了其使用方法,给出了接收和发送电路的设计过程,并提供了发送、接收端口以及内部寄存器标志状态位的仿真波形图,直观地展现了UART工作时内部寄存器的状态变化,为接口编程提供帮助。

[1]张培仁,孙力.C8051F系列单片机原理与应用[M].北京:清华大学出版社,2013.Zhang Peiren,Sun Li.Beijing:Principle and Application of C8051F MCU Family[M].Tsinghua University Press,2013.

[2]赵亮,侯国锐.单片机C语言编程与实例[M].北京:人民邮电出版社,2003.Zhao Liang,Hou Guorui.MCU Programming and Instantiation of C Language[M].Beijing:Post&Telecom Press,2003.

[3]周立功,夏宇闻.单片机与CPLD综合应用技术[M].北京:北京航空航天大学出版社,2003.Zhou Ligong,Xia Yuwen.Integrated Application Technology of MCU and CPLD[M].Beijing:Beihang University Press,2003.

[4]张迎新,雷文,姚静波.C8051F系列SOC单片机原理及应用[M].北京:国防工业出版社,2005.Zhang Yingxin,Lei Wen,Yao Jingbo.Principle and Application of C8051F SOC MCU Family[M].Beijing:National Defence Industry Press,2005.

[5]阎石.数字电子技术基础 [M]北京:高等教育出版社,1997.Yan Shi.Fundamentals of Digital Electronics[M].Beijing:Higher Education Press,1997.

[6]袁俊泉,孙敏琪,曹瑞.Verilog HDL数字系统设计及其应用[M]西安:西安电子科技大学出版社,2002.Yuan Junquan,Sun Minqi,Cao Rui.Verilog HDL Design and Applications of Digital System[M].Xi’an:Xidian University Press,2002.

[7][美]Janick Bergeron.编写测试平台--HDL模型的功能验证(第二版)[M].北京:电子工业出版社,2006.Janick Bergeron.Writing Testbenches Functional Verification of HDL Models Second Edition[M].Beijing:Publishing House of Electronics Industry,2006.

[8]William K.Lam.Hardware Design Verification[M]USA:Pearson Education,2006.

Design of an UART in C8051F MCU Family

Sun Jing

The function of UART and the Data Format in C8051F MCU family are presented.The operation and the two typical communications are analyzed.The function and use of SFRs are analyzed detailedly.The design process of Transmit and Receive circuit are provided.The state of SFRs is simulated.The timing of TX0 and RX0 are simulated.Multiprocessor communications process is simulated.Simulation waveforms are provided.

C8051FMCU family;UART;SFR;Multiprocessor communications;Simulation waveforms;Simulation program

10.3969/j.issn.1002-2279.2017.04.004

TN4

A

1002-2279-(2017)04-0011-05

孙静(1982—),女,辽宁省开原市人,硕士研究生,工程师,主研方向:集成电路设计。

2016-08-02