一种超低功耗模数转换器的设计与仿真

2017-09-11胡云峰易子川周国富

胡云峰, 易子川,*, 李 琛, 周国富,3

(1. 电子科技大学中山学院,中山 528402; 2. 深圳市国华光电科技有限公司,深圳 518110;3. 深圳市国华光电研究院,深圳 518110)

一种超低功耗模数转换器的设计与仿真

胡云峰1, 易子川1,2*, 李 琛2, 周国富2,3

(1. 电子科技大学中山学院,中山 528402; 2. 深圳市国华光电科技有限公司,深圳 518110;3. 深圳市国华光电研究院,深圳 518110)

为了降低电子终端设备的功耗,提出了一种超低功耗模数转换器(ADC). 首先,通过使用组合电容和三电平转换方案,电容阵列数模转换器(DAC)转换能耗相比传统结构降低99.4%,面积减少87.2%. 采用基于动态逻辑的逐次逼近寄存器(SAR)和两级全动态比较降低SAR ADC整体功耗. 最后,SAR ADC在180 nm CMOS工艺下进行设计与仿真. 仿真结果表明:在1 V电源电压和100 kHz的采样频率下,ADC的信噪失真比(SNDR)为61.59 dB,有效位(ENOB)为9.93 bit,总功耗为0.188 μW,功耗优值(FOM)每步为1.9 fJ. 设计的超低功耗SAR ADC适用于低功耗电子终端设备.

模数转换器; 逐次逼近寄存器; 电容阵列DAC; 超低功耗; 组合电容

近年来,逐次逼近型模数转换器(SAR ADC)由于其低功耗的特点被广泛应用于低功耗电子终端设备[1-5]. SAR ADC主要由电容阵列数模转换器(DAC)、逐次逼近寄存器(SAR)和比较器组成. 电容阵列DAC的转换能耗对SAR ADC功耗影响非常显著[2, 6-7]. 为降低电容阵列DAC的转换能耗,已有不少文献提出了高能效电容阵列DAC结构: 与传统的电容阵列DAC结构相比,单调结构[8]、共模电压结构[9]、三电平结构[10]、共模电压单调(VMS)结构[11]、高精度结构[12]和混合电容(HCS)结构[13]实现了10位电容阵列DAC的转换能耗分别降低81.26%、87.52%、96.89%、97.66%、93.7%和98.83%. 为进一步降低电容阵列DAC能耗,本文提出一种基于组合电容的电容阵列DAC结构及配套的三电平转换方案,并分析了该结构的转换能耗,设计了低功耗SAR和比较器电路,最后基于180 nm CMOS工艺对整体电路进行了仿真和分析.

1 SAR ADC电路设计

1.1 电容阵列DAC

1.1.1 结构 利用电容并联原理,2个相同容量的电容器并联后总电容加倍;利用电容串联原理,2个相同容量的电容器串联总电容减半. 依据电容的并联串联原理,单位电容C可以扩展为组合电容. 本文提出10 bit差分SAR ADC结构(图1B),电容阵列DAC包含2个相同的电容阵列,它们的输出端分别连接比较器的差分输入端,最低位单位电容C用组合电容代替,使电容阵列DAC增加了1 bit精度,因此,在设计同样位数的电容阵列DAC时,最高位电容的单位电容数量可以减少50%.

图1 SAR ADC结构图

1.1.2 三电平转换方案 电容阵列DAC包含3种参考电平:参考电压(Vref)、共模电压(Vcm)和地(gnd). SAR ADC工作时通过电容阵列DAC的参考电平转换来完成比较,以4 bit SAR ADC为例说明本文提出的三电平转换方案. 电容阵列DAC工作分为4个阶段:第1、2、3、4到第N次比较(图2~5).

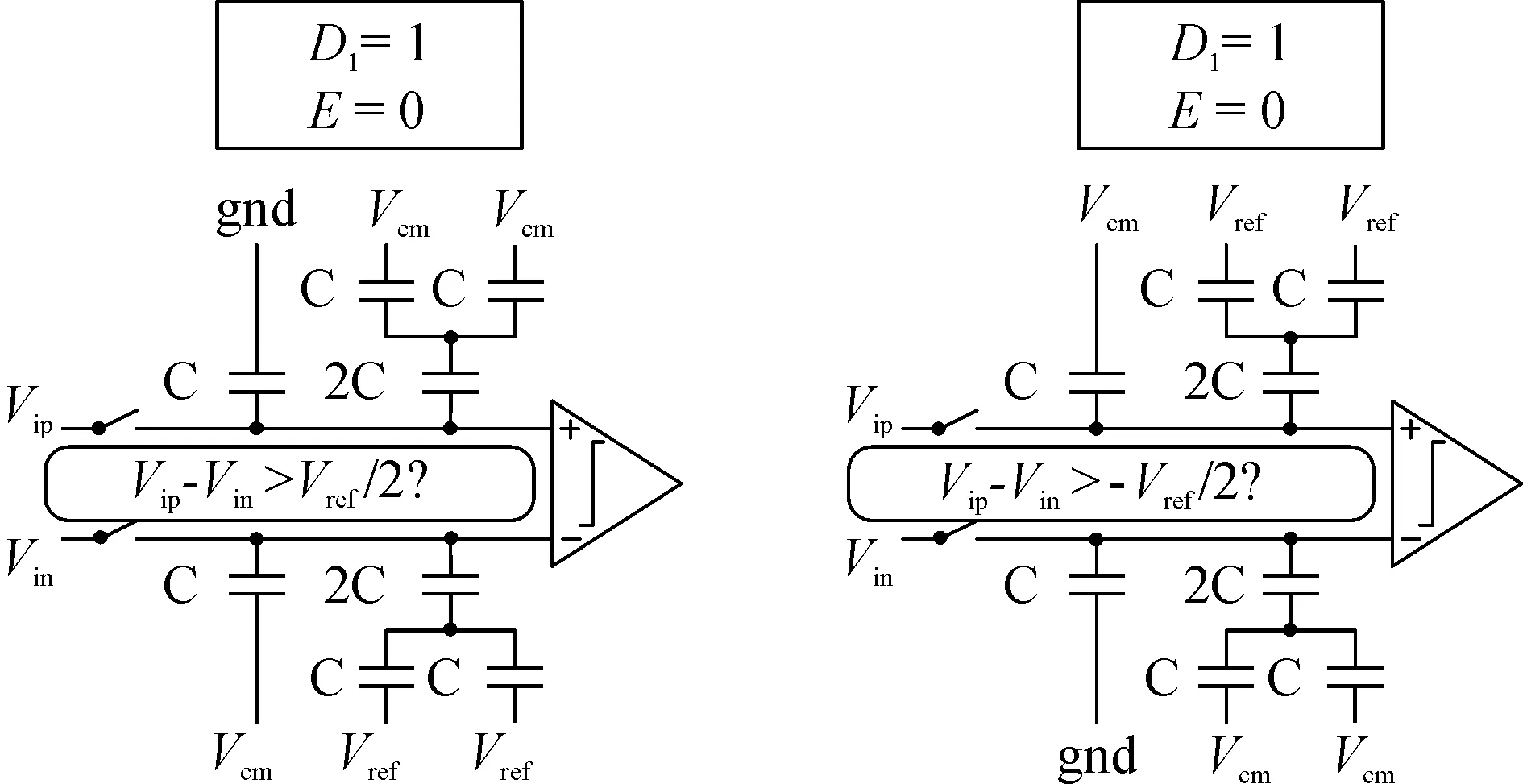

图2 第1次比较

第1次比较:初始时,2个电容阵列中最高位到最低位电容的参考电平依次设置为(gnd,Vcm, …,Vcm),差分输入信号通过采样开关连接到2个电容阵列. 采样结束后,断开采样开关,比较器直接执行第1次比较,并输出比较结果D1.

第2次比较:根据第1次比较的结果D1,输出电压较低的电容阵列中各电容的参考电平依次变为(Vcm,Vref, …,Vref),因此,输出电压较低的电容阵列输出电压升高Vref/2. 输出电压较高的电容阵列中各电容的参考电平保持不变. 然后比较器执行第2次比较.

图3 第2次比较

第3次比较:根据第2次比较的结果D2,输出电压较低的电容阵列中的最高位电容的参考电平由gnd变为Vcm或者由Vcm变为Vref,电容阵列输出电压升高Vref/4,然后比较器执行第3次比较.

图4 第3次比较

第4次比较:从第4次比较开始,根据前一次比较的结果,输出电压较高的电容阵列中的对应电容的参考电平由Vcm变为gnd或者由Vref变为Vcm. 举例来说,在第4次比较时,输出电压较高的电容阵列中的次高位电容的参考电压由Vcm变为gnd或者由Vref变为Vcm,然后比较器执行第4次比较. 重复该步骤直到执行完第N次比较.

图5 第4次比较

1.1.3 转换能耗建模 第1次比较时,由于采样结束后没有进行参考电平的转换,电容阵列DAC没有产生转换能耗,E1=0. 第2次比较时,由于输出电压较低的电容阵列中各电容的参考电平同时升高Vref/2,因此,第2次比较未产生转换能耗,E2=0. 第3次比较时,由于输出电压较低时电容阵列中的各电容参考电平变为相同,各电容之间发生电荷闭环流动,因此,第3次比较未产生转换能耗,E3=0. 第4次到第N次比较时,每次比较仅有1个电容的参考电平发生变化,参考文献[14]提出的DAC转换能耗计算方法,可以得到第4次到第N次比较的转换能耗,当i=4时,

当5≤i≤N-1时,

当i=N时,

Ei=

其中,D1、D2、…、DN为第1、2、…、N次比较的结果. 因此,每次比较的结果都会影响转换能耗的大小.

N位电容阵列DAC比较周期的转换能耗为第1次到第N次比较转换能耗之和:

N位SARADC的输出数字码有2N种情况,将所有输出数字码对应比较周期的转换能耗求和并除以2N,即得到电容阵列DAC平均转换能耗模型:

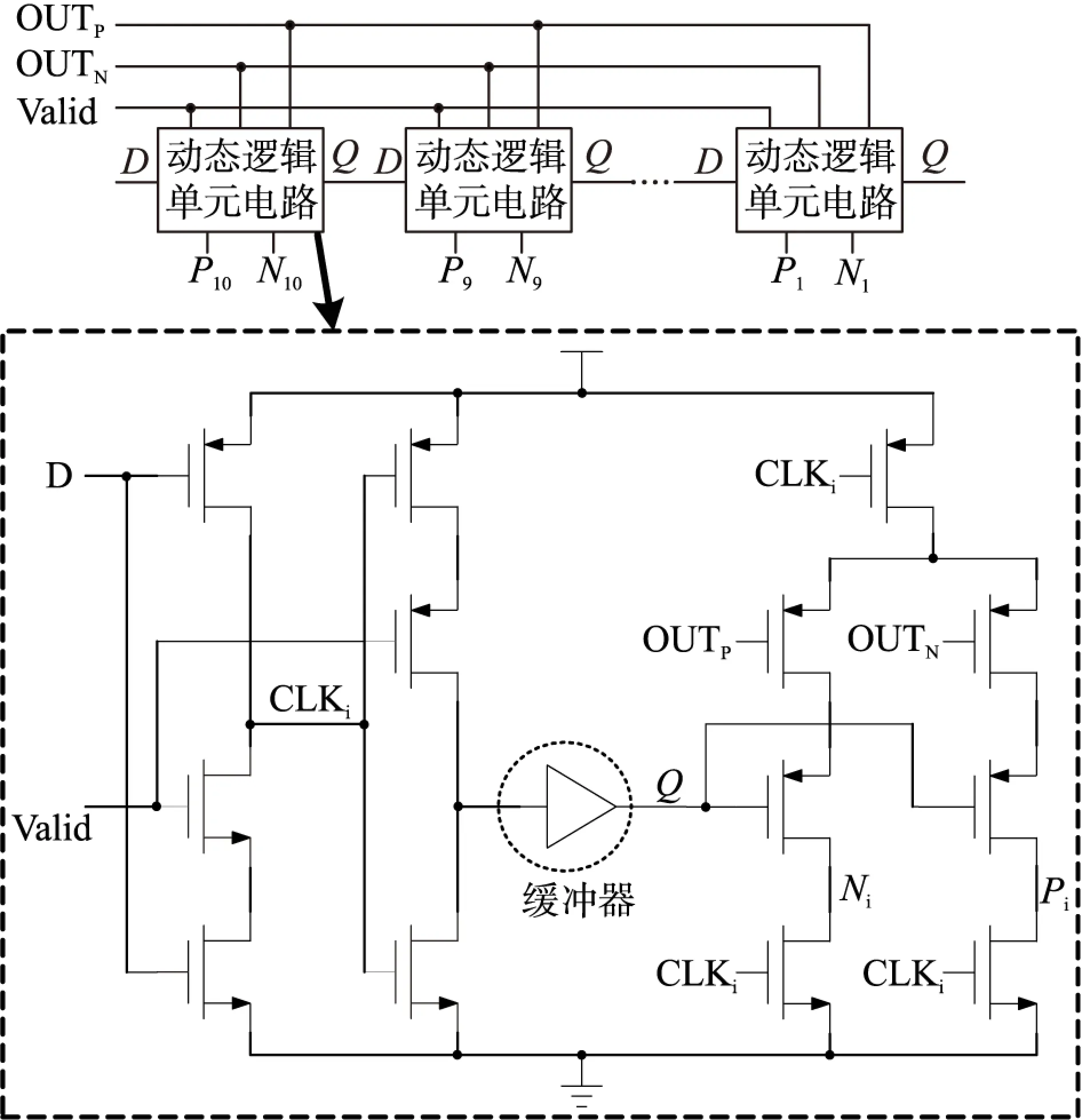

1.2 移位寄存器

为了进一步降低SAR ADC功耗,采用基于动态逻辑的SAR电路[15](图6). 本文在文献[15]比较器结构的基础上,通过在动态逻辑单元电路中添加缓冲器,延长锁存控制信号Q的低电平时间,从而延长给Ni或Pi充电的MOS管导通时间,提高Ni或Pi的电压.Ni或Pi的电压提高后可以避免下一级电路中被驱动MOS管出现亚阈值导通状态. 图7为锁存控制信号Q时间延长示意图,当Valid变为低电平时,文献[15]中的Q马上变为高电平,本文的Q经过一段缓冲器延长时间才变为高电平.

图6 基于动态逻辑的SAR

图7 锁存控制信号Q时间延长示意图

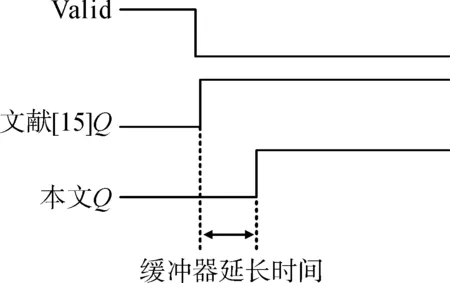

1.3 比较器

本文比较器采用两级全动态比较器(图8),第一级为动态预放大级,VP和VN为电容阵列DAC输出信号,连接比较器差分输入端,AN和AP为差分输出. 第二级为动态锁存级,负责二级放大和结果锁存,OUTP和OUTN为比较结果. 比较器通过PMOS管接电源(图8),通过NMOS管接地,这些接电源和接地的MOS管同时受时钟信号CLK控制,因此不会同时导通,即比较器不会形成从电源到地线的通路,也不会产生静态功耗.

图8 两级全动态比较器

2 结果与讨论

2.1 DAC转换能耗模型仿真

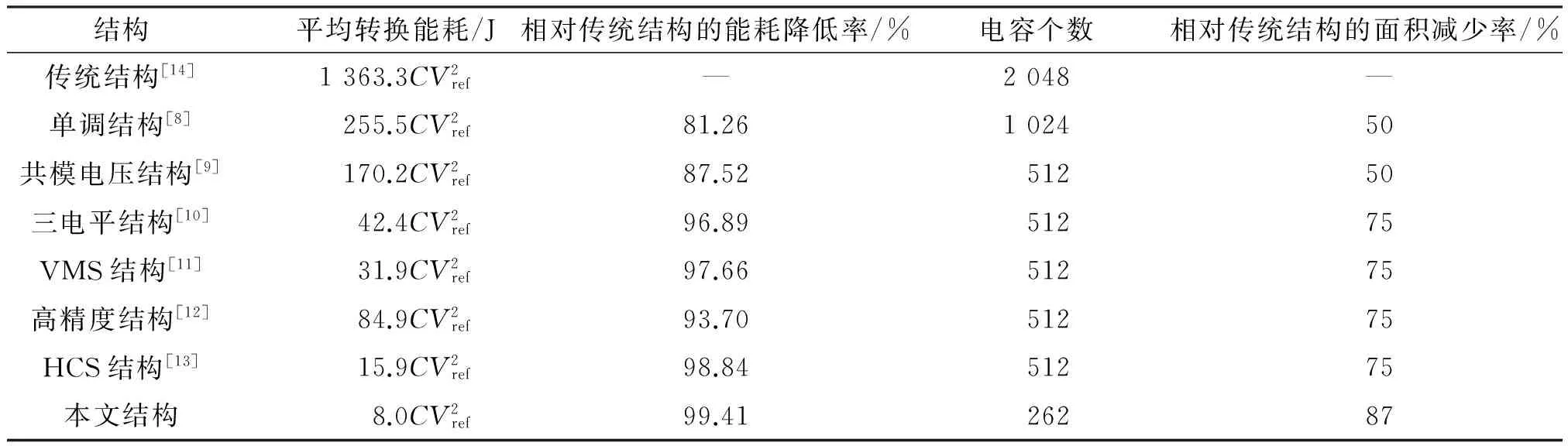

利用MATLAB进行DAC转换能耗模型仿真,几种10 bit电容阵列DAC比较周期的转换能耗随输出数字码而变化(图9),平均转换能耗如表1所示. 由于本文的DAC第1到第3次比较未产生转换能耗,而且从第4次比较开始,每次比较仅有1个电容的参考电平变化,因此平均转换能耗较低. 模型仿真表明,电容阵列DAC结构相比传统结构平均转换能耗降低99.4%,单位电容数量减少87.2%.

表1 几种10 bit电容阵列DAC的转换能耗和面积减少率比较Table 1 Comparison of energy consumption and areareduction for several 10-bit capacitive array DAC

图9 几种10位电容阵列DAC的转换能耗随输出码的变化

Figure 9 Switching energy of several 10-bit capacitive array DACs with output codes

2.2 SAR ADC电路仿真

采用180 nm CMOS工艺设计和仿真超低功耗SAR ADC. 电容阵列的单位电容C尺寸设置为4 μm×4 μm,单位电容C容值为17.2 fF. 设置电路的仿真条件如下:电源电压和参考电压Vref均为1 V,共模电压Vcm为0.5 V,采样频率为100 kHz,输入信号频率为46.243 kHz.

对电路仿真输出采集1 024个点并进行快速傅里叶变换(FFT)分析(图10),SAR ADC的无杂散动态范围(SFDR)为71.32 dB,信噪失真比(SNDR)为61.59 dB,有效位(ENOB)为9.93 bit.

图10 1 024采样数据的FFT结果

对电路仿真输出采集32 768个点并进行微分非线性(DNL)和积分非线性(INL)分析(图11),DNL和INL的范围分别为0.15~-0.16和0.24~-0.21.

SAR ADC电路仿真的总功耗为0.188 μW,功耗优值(FOM)每步为1.9 fJ. 表2为SAR ADC与文献的性能比较. 本文提出的SAR ADC在FOM远低于其他文献,实现了较好的功耗性能.

图11 32 768采样数据的DNL和INL结果

性能参数数据来源文献[16]文献[17]文献[18]本文工艺技术特征尺寸/nm180180180180分辨率/bit1291010电源电压/V1.00.91.01.0采样频率/kHz100100100100功耗/μW251.331.720.19ENOB/bit10.558.029.489.93FOM/fJ16551.324.11.9

3 结论

本文提出了一种超低功耗SAR ADC,通过采用组合电容和三电平转换方案使电容阵列DAC转换能耗降低99.4%,电容阵列DAC面积减少87.2%. 同时通过采用动态逻辑SAR和两级全动态比较器来降低SAR ADC整体功耗. SAR ADC采用180 nm CMOS工艺进行设计与仿真,在1 V电源电压<100 kHz的采样频率下,其SNDR为61.59 dB,总功耗为0.188 μW,有效位(ENOB)为9.93 bit,功耗优值(FOM)每步为1.9 fJ. 文中设计的SAR ADC适合应用于低功耗电子设备.

[1] HARPE P,GAO H,VAN DOMMELE R,et al. A 0.20,3 nW signal acquisition IC for miniature sensor nodes in 65 nm CMOS[J]. IEEE Journal of Solid-State Circuits,2016,51(1):240-248.

[2] LIN J Y,HSIEH C C. A 0.3 V 10-bit 1.17 f SAR ADC with merge and split switching in 90 nm CMOS[J]. IEEE Transactions on Circuits & Systems I,2015,62(1):70-79.

[3] LEE H,PARK S,LIM C,et al. A 100-nW 9.1-ENOB 20-kS/s SAR ADC for portable pulse oximeter[J]. IEEE Transactions on Circuits & Systems II Express Briefs,2015,62(4):357-361.

[4] CHUNG Y H,WU M H,LI H S. A 12-bit 8.47-fJ/conversion-step capacitor-swapping SAR ADC in 110-nm CMOS[J]. IEEE Transactions on Circuits & Systems I,2015,62(1):10-18.

[5] TAO Y,LIAN Y. A 0.8-V,1-MS/s,10-bit SAR ADC for multi-channel neural recording[J]. IEEE Transactions on Circuits & Systems I,2015,62(2):366-375.

[6] LEE B G. Power and bandwidth scalable 10-b 30-MS/s SAR ADC[J]. IEEE Transactions on Very Large Scale Integration Systems,2014,23(6):1103-1110.

[7] ZHU Z,LIANG Y. A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-μm,CMOS for medical implant devices[J]. IEEE Transactions on Circuits & Systems I,2015,62(9):2167-2176.

[8] LIU C C,CHANG S J,HUANG G Y,et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure[J]. IEEE Journal of Solid-State Circuits,2010,45(4):731-740.

[9] ZHU Y,CHAN C H,CHIO U F,et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS[J]. IEEE Journal of Solid-State Circuits,2010,45(6):1111-1121.

[10]YUAN C,LAM Y. Low-energy and area-efficient tri-level switching scheme for SAR ADC[J]. Electronics Letters,2012,48(9):482-483.

[11]ZHU Z,XIAO Y,SONG X. VCM-based monotonic capa-citor switching scheme for SAR ADC[J]. Electronics Letters,2013,49(5):327-329.

[12]RAHIMI E,YAVARI M. Energy-efficient high-accuracy switching method for SAR ADCs[J]. Electronics Letters,2014,50(7):499-501.

[13]XIE L,WEN G,LIU J,et al. Energy-efficient hybrid capacitor switching scheme for SAR ADC[J]. Electronics Letters,2014,50(1):22-23.

[14]GINSBURG B P,CHANDRAKASAN A P. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC[C]∥IEEE International Symposium on Circuits and Systems. Kobe: IEEE,2005:184-187.

[15]ZHU Z,XIAO Y,WANG W,et al. A 0.6 V 100 KS/s 8-10 b resolution configurable SAR ADC in 0.18 μm CMOS[J]. Analog Integrated Circuits and Signal Processing,2013,75(2):335-342.

[16]VERMA N,CHANDRAKASAN A P. An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes[J]. IEEE Journal of Solid-State Circuits,2007,42(6):1196-1205.

[17]TANG H,SUN Z C,CHEW K W R,et al. A 1.33 μW,8.02-ENOB 100 kS/s successive approximation ADC with supply reduction technique for implantable retinal prosthesis[J]. IEEE Transactions on Biomedical Circuits & Systems,2014,8(6):844-856.

[18]YUAN C,NG K A,XU Y P,et al. A 1-V 9.8-ENOB 100-kS/s single-ended SAR ADC with symmetrical DAC switching technique for neural signal acquisition[C]∥IEEE Asian Solid-State Circuits Conference. Xiamen:IEEE,2016:1-4.

【中文责编:谭春林 英文审校:肖菁】

Design and Simulation of an Ultra-Low Power ADC

HU Yunfeng1, YI Zichuan1,2*, LI Chen2, ZHOU Guofu2,3

(1. Zhongshan Institute,University of Electronic Science and Technology of China,Zhongshan 528402, China; 2. Shenzhen Guohua Optoelectronic Technology Co., Ltd., Shenzhen 518110, China; 3. Academy of Shenzhen Guohua Optoelectronics, Shenzhen 518110, China)

In order to reduce the power consumption of electronic terminal equipment, an ultra-low power ADC is presented. Firstly, by using combinational capacitor and tri-level switching scheme, the proposed capacitor array DAC achieves 99.4% switching energy saving and 87.2% capacitor area reduction, compared to conventional switching scheme. Next, dynamic logic SAR and two-stage fully dynamic comparator are used to decrease the power consumption of SAR ADC. Finally, the proposed SAR ADC is designed and simulated in 180 nm CMOS technology. The simulation results show that, when supply voltage is 1 V and sampling rate is 100 kHz, the ADC achieves an SNDR of 61.59 dB and ENOB of 9.93 bit, consumes 0.188 μW, resulting in a Figure-of-Merit(FOM) of 1.9 fJ per conversion-step. In conclusion, the ultra-low power SAR ADC proposed in this paper is suitable for application in low power electronic devices.

ADC; SAR; capacitor array DAC; ultra-low power; combinational capacitor

2017-02-23 《华南师范大学学报(自然科学版)》网址:http://journal.scnu.edu.cn/n

国家自然科学基金项目(61571196);广东省科技计划项目(00760211330304099,2014B090914004,2016B090918083);广东省引进创新科研团队计划资助(2013C102);深圳市科技计划项目(GQYCZZ20150721150406);中山市科技计划项目(2016B2146)

TN453

A

1000-5463(2017)04-0005-06

*通讯作者:易子川,高级工程师,Email:yizichuan@163.com.