基于全流程并行加速的改进数字下变频器设计*

2017-09-06吉炜寰邹玉炜黄磊

吉炜寰,邹玉炜,黄磊

(1.河南职业技术学院电气工程系,郑州450046;2.安阳师范学院物理与电气工程学院,河南安阳455000; 3.东南大学电气工程学院,南京210096)

基于全流程并行加速的改进数字下变频器设计*

吉炜寰1*,邹玉炜2,黄磊3

(1.河南职业技术学院电气工程系,郑州450046;2.安阳师范学院物理与电气工程学院,河南安阳455000; 3.东南大学电气工程学院,南京210096)

针对宽带通信雷达探测系统中高速率数据处理难度较大的问题,设计了一种全流程并行化处理的高速率数字下变频器,混频模块采用并行化的流水线坐标旋转数字计算机(CORDIC)对来自A/D的高速采样数据进行分组处理,以降低单个通道的数据率;抽取滤波模块采用多相滤波器进一步将高阶卷积网络进行并行化分解,减少不必要的乘累加运算。实验结果表明:最大处理速率由原先的131MHz提高到了255MHz,改进设计利用现有硬件条件大幅度提高了处理速度,减少了通带内信号的衰减。

数字下变频器;坐标旋转数字式计算机;多相分解;抽取滤波

在现代宽带通信雷达探测系统中,尽管高速过采样技术有利于提高信噪比和镜频抑制比,也能有效减少信号失真[1-3],但由于器件性能的限制,系统需要通过数字下变频器件在不过度恶化信号质量的同时降低处理速度,当前通用数字下变频器大多采用典型的基于多级抽取滤波的结构,中频数字信号首先与数控振荡器NCO(Numerically Controlled Oscillator)产生的本振信号混频,然后通过CIC高倍率信号抽取,HB半带滤波器以及FIR高阶抗混叠滤波后解调出I/Q两路正交信号,用于后续处理估计。而NCO和FIR滤波器往往成为影响系统采样频率提升的关键节点,这是因为目前实现NCO多采用直接数字式频率合成方法,本质上是将存储在ROM中的波形在相位域进行采样,最高输出频率将是1/2倍的fclk,ROM器件的访问速度受限,所以不能一味提高采样频率;同时,高阶抗混叠滤波器大量采用基于乘累加的卷积结构,增加了硬件布线难度及延迟,随着阶数和时钟频率的增加,各路径延迟的不同步将导致数据建立时间过长,无法输出稳定结果。为了降低FIR滤波器的处理负担,CIC滤波器的抽取倍率不得不进一步提高,导致通带衰减过快,人为恶化了信号质量,在后续处理中必须进行补偿处理[4-6]。为此,本文利用多相并行计算的思想重新设计了下变频器,将包括混频和滤波运算在内的整个处理流程进行全并行化处理,在降低单个通道数据率的同时有效提升了系统的处理效率。

1 基于多相并行的改进NCO设计

多相分解思想本质上是将单条数据处理路径通过多路并行处理,降低单个路径的数据吞吐速率[7-8]。采用经典DDS结构的NCO,其相幅变换模块成为制约DDC整体速度的瓶颈,虽可采用流水线技术进行优化,亦不能对速度有质的提高。由式(1)知,这最终将影响可调频率范围。

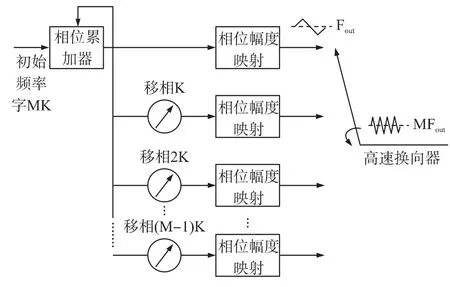

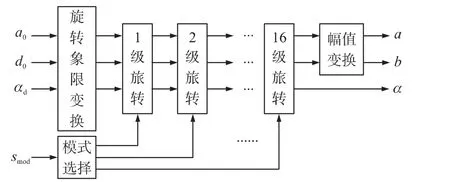

图1 多相分解NCO原理

将相位序列每M个分为一组,初始相位字设为MK,则NCO开始工作后,相位累加器将进行0,MK,2MK…NMK的线性累加,在累加器输出NMK的每一个间隔周期内,单路移相器将同时并行产生NMK+K,NMK+2K…NMK+(M-1)K共M路偏移相位值,这些值同时被读入M个幅相转换模块,每一个相位字将产生一个幅值,最后通过M倍采样率的换向器进行并串转换,将并行的数据合成高速串行数据流。如果单路NCO的最高工作频率为Fmax,则理论上最终输出的数据速率为MFmax,可调频率范围变为0~0.5MFmax,提高了M倍。

1.1 基于多相并行加速的CORDIC设计

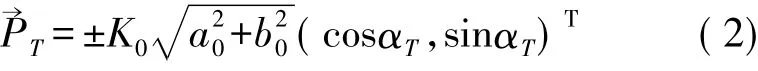

图1本身存在一些不足,以最简单的二相分解DDC为例,如果采用查找表法,这将消耗4个LUT,同原始DDC结构相比,将消耗成倍的存储器资源,增加器件的功耗,对于信道化接收机而言不便采用。此外,采用此结构后I/Q两路的数据吞吐量过大,大大增加了后续同步处理压力。CORDIC算法则很好适应这种结构,该算法的全称为坐标旋转数字式计算[9-12],目前在数字信号处理领域获得了广泛应用,它仅利用移位相加运算同时实现了正交信号的合成与混频,不需要查找表和乘法器,适合高速数据运算。假设有一个二维矢量其初始位置为→P0=(a0,b0)T,当它以逆时针逐级旋转θ角后至α,新的坐标值变为:

式中,αT为目标向量的角度。如果将初始坐标向量设为(a0,b)T=(0,x[n])T,x[n]为射频采样信号,则上式变为:

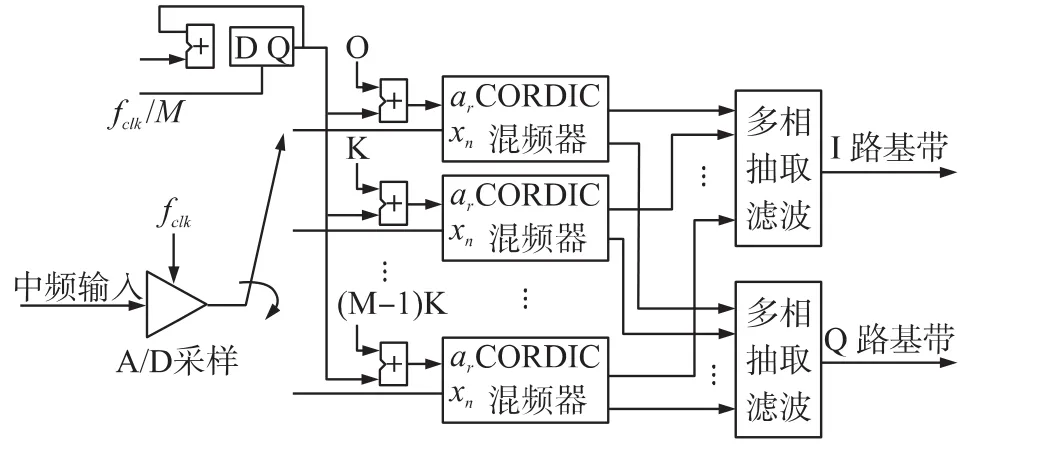

从上式可见,在旋转模式下,CORDIC算法可以实现正交混频的功能。利用CORDIC算法实现的多相分解DDC结构如图2所示。

图2 CORDIC算法实现多相分解混频

由于CORDIC核同时实现了NCO和混频功能,因此需前置换向器,预先对x[n]作相位分解。该结构的优势是显而易见的,它虽然总的采样率变为原来的M倍,但单路DDC速率并不高,此外该结构省去了混频乘法器和查找表。

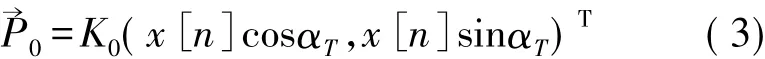

1.2 流水线CORDIC实现

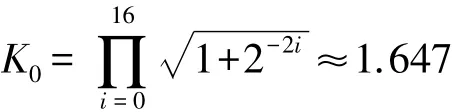

图3展示了16级流水线CORDIC电路结构,该电路由4个模块组成:旋转象限变换单元、多级流水线旋转单元、幅值变换单元、模式选择单元。

公元前359年,秦孝公命商鞅颁布《垦田令》,拉开了全面变法的序幕。在商鞅前后两次变法中,重农抑商、奖励耕织的政策从未改变。《史记·商君列传》载:“僇力本业,耕织致粟帛多者复其身。事末利及怠而贫者,举以为收孥。”“为田开阡陌封疆,而赋税平。”[6]商鞅承认土地私有,允许自由买卖,适应了当时以铁器、牛耕为代表的新的先进的生产力,奖励“耕织致粟帛多者”,惩罚“事末利及怠而贫者”在今天看来是落后的,然而在自给自足的自然经济下无疑是正确的,通过发展农业,封建国家可以征收稳定的土地税,可以更好地控制金字塔底端的农民群体,提高农民的生产积极性,促进国家经济迅速发展。

图3 流水线CORDIC原理

若输入向量仅经过简单迭代旋转,CORDIC最大可调节范围为-99.88°~99.88°[11-12],为了实现圆周范围内旋转,需要借助三角函数的对称性对输入的旋转角度进行象限变换,同时对输出的坐标幅值变换,具体方法可参考文献[11]中的说明。在旋转模式下,CORDIC计算机对向量模值有一定缩放,在16级迭代情况下,缩放值趋于常数:

为了防止结果溢出,需要将初始输入信号幅值统一右移一位,即缩小0.5倍。

2 基于多相并行的抽取滤波器设计

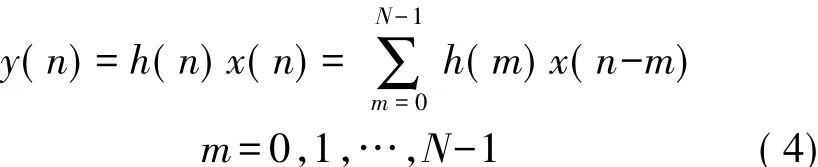

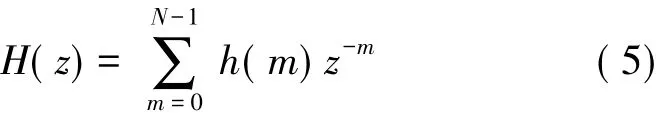

为了降低后续抽取滤波器的处理压力,亦采用多相并行处理的思想重新设计滤波器组[13]。对于一个N阶常规FIR滤波器,其时域卷积表达式为:

式中,h(m)表示N阶单位脉冲响应函,是一个有限长的序列;x(n-m)表示输入信号经过m个抽头延时线后的结果。整个滤波器通过有限次乘累加算法实现。

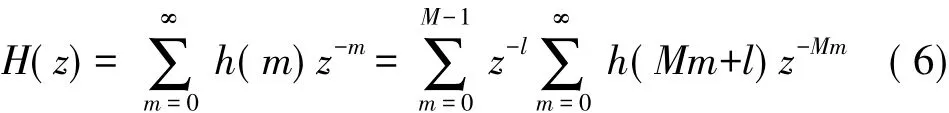

利用z变换可以将上式写作:Y(z)=X(z)H(z),其中:

由于对NCO进行了M相分解,等效于在每一个通路上对信号进行了M倍抽取,S假定滤波器的阶数为M的整数倍,则式(1)可以重写为:

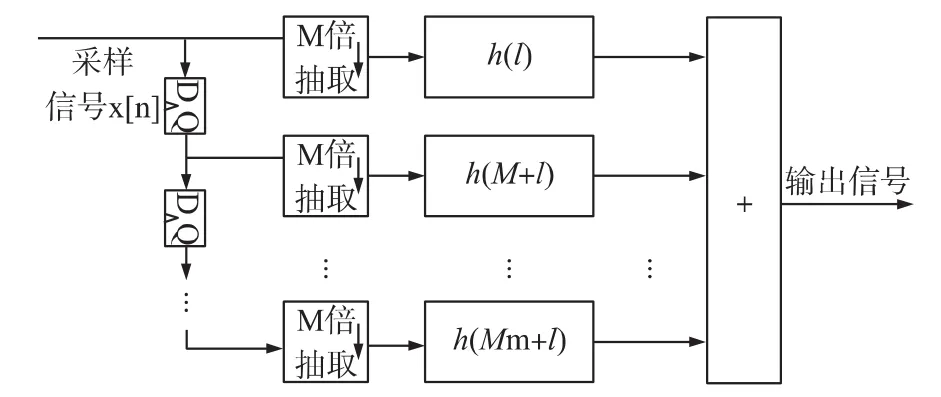

式中,h(Mm+l)称为FIR滤波器的多相分量,基本原理图如图4所示。

图4 多相分解滤波器原理

从图4可以看出,原来需要N阶乘累加运算的滤波器被分解为N/M阶,虽然消耗的乘法器总数没有减少,但通过并行处理和数据提前抽取,在减少了不必要运算的同时提高了乘法器的使用效率。实际设计中M倍的抽取处理被图2中的前端高速换向器所代替。

3 系统设计与实验分析

3.1 参数设计与逻辑综合

就单频信号而言,多相分解DDC本质上只是将原来单通道NCO的工作频率降低了M倍,由fclk变为fclk/M,故式(1)仍然适用。而对于雷达系统中广泛使用的线性调频连续波(LFMCW)而言,初始频率字K将步进增加,随着K值的线性增加,相移量也将分组步进,原来一个时钟周期内步进的频率值Δf,将花M个时钟周期完成,根据文献[14]可以推导得到新的波形参数公式:

式中,ΔK为频率步进字,B为F LMCW的带宽,T为FMCW的持续时间,fclk和f'clk分别代表CORDIC工作时钟以及频率步进字寄存器的工作时钟。因此,在达到同样带宽和持续时间下,频率步进字也必须提高M倍。

采用FPGA设计实现了8相分解DDC,选用Altera公司的StratixⅡ系列的EP2S130芯片进行逻辑综合。FIR滤波器原型采用16 bit、64阶等波纹结构,对于单个通道仅需8次乘累加运算。通过逻辑综合可得,系统共消耗44 528个逻辑单元,115个9 bit嵌入式硬件乘法器,0 bit嵌入式M4K存储单元,系统最大采样速率为255 MHz。对比之下,除去其他组件,单个64阶常规FIR滤波器经过综合后最大工作频率仅能达到79 MHz,无法直接处理高速数据流,单个查找表法NCO也只能达到131 MHz的最大采样速率,同时将多消耗256 kbit嵌入式M4K存储单元,因此改进设计显著提升了DDC的处理速率。

3.2 闭环实验与结果分析

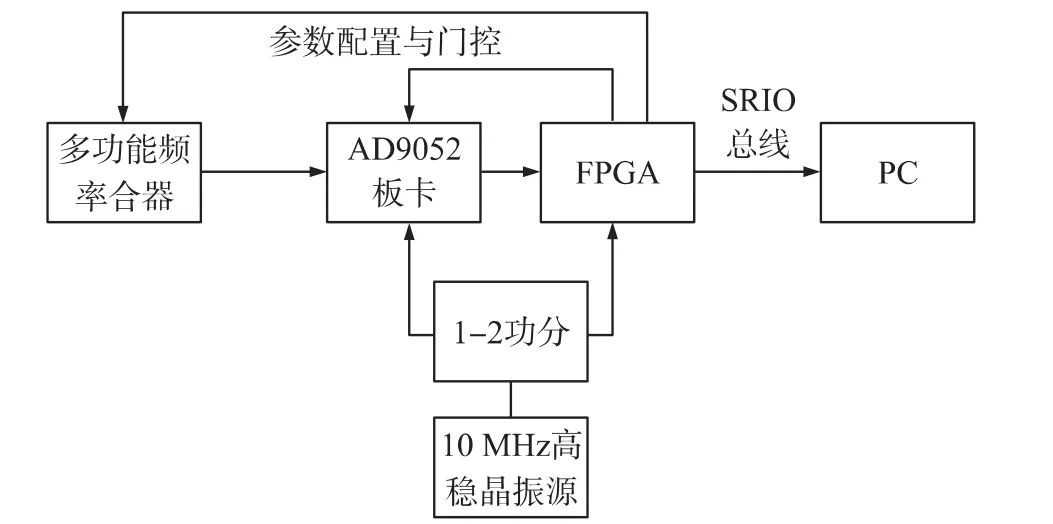

图5 闭环实验

实验搭建如图5所示的闭环系统[15-16],AD9954作为多功能频率合成器的核心器件,可编程产生频率为70 MHz,扫频宽度5 MHz的LFMCW信号,扫频周期10ms,AD9652高速ADC板卡将采集到的模拟中频信号转换为200 MHz采样率16 bit数字信号,数字信号送入FPGA内部的多相数字下变频器处理得到基带正交信号,数字信号通过SRIO总线送入计算机进行时频域分析。AD9652板卡和FPGA内部均有锁相环PLL模块,可将外部10 MHz晶振信号倍频至所需的系统时钟。实验结果如图5所示。

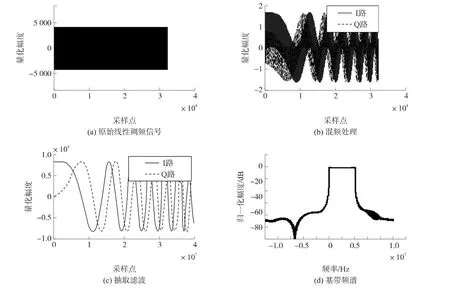

图6 闭环实验结果

由于10 ms共产生5×105个样值,为方便观察仅在时域中显示前3.2×103个样值的处理结果。

图6中200 MHz的LFM信号通过8倍率多相抽取滤波后变为25 MHz基带,从基带频谱图看出,5 MHz的原始扫频信号被完整恢复出来。

为了进一步证明改进设计对信号失真度有改善,图7和图8对比了两种抽取滤波器的频响特性。

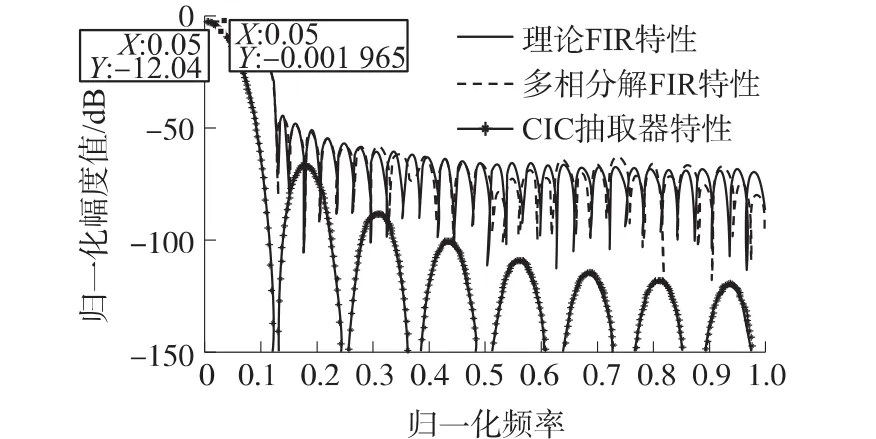

图7 滤波器幅频特性比较

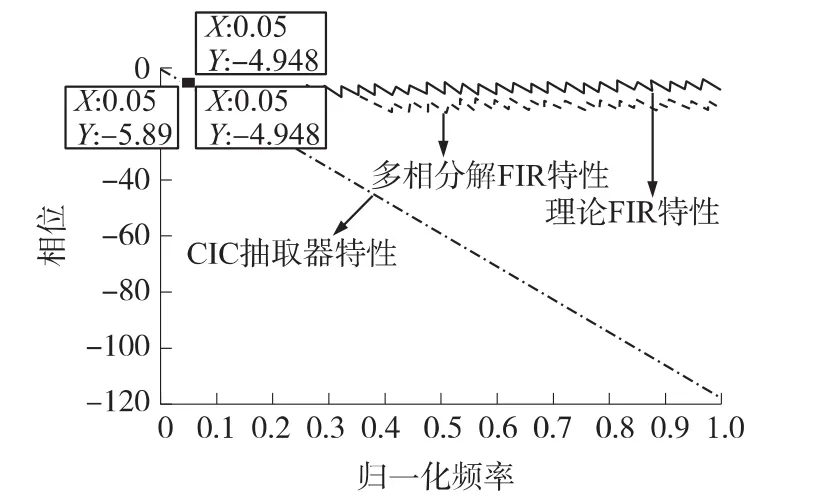

图8 滤波器相频特性比较

根据设计的波形参数可知,滤波器的通带边缘位于:5 MHz/100 MHz=0.05。CIC滤波器采用典型的5级级联结构,从图7看出,由于其带内衰减过快,在0.05附近幅度衰减值达到-12 dB,而FIR抽取滤波器仅为0.002 dB,具有平坦的通带特性。因此,改进设计能够在实现抗混叠滤波功能的同时,将基带信号的失真保持在极小的范围内。

图8对比了滤波器的相频特性,从图8可以看出,在0~0.05的通带内,各个滤波器均具有十分近似的线性相位曲线。因此在相位域,改进设计能够满足指标要求。该实验证实了改进的全流程并行数字下变频器的可行性和有效性。和传统方法比,该方案在现有硬件条件下大幅度提高了下变频器的处理速度的同时还有效减少了基带信号的失真。

4 结束语

本文提出了一种改进的高速数字下变频器,采用并行化处理,将高速采样数据进行多相分解,降低单个通道中混频器和滤波器的处理速度,其中混频模块采用CORDIC算法,降低了多相分解NCO的资源需求,多相FIR滤波器和普通CIC抽取器相比,对信号的失真影响更小。该方法总的采样率虽然很高,但通过增加相位通道数及多相滤波器的级联,大大提升了雷达探测系统对后续数据的处理能力。采用闭环实验的方法将200 MHz过采样中频LFMCW数字信号输入设计电路中进行功能验证,跟常规电路相比,系统在实现高速信号下变频的同时,有利于减小信号的幅相失真。

[1]刘劲,戴奉周,刘宏伟.基于过采样抽取子带处理的宽带雷达杂波抑制[J].电波科学学报,2011,26(1):95-101.

[2]邱贺,段永红.用于感应式磁传感器低噪声前置放大器的研制[J].仪表技术与传感器,2015(1):22-24.

[3]李刚,张丽君,林凌,等.结合过采样技术和锯齿成形函数的微弱信号检测[J].电子学报,2008,36(4):756-759.

[4]Aggarwal S,Meher PK,Khare K.Multirate Filter Design and Implementation for Mixed-Signal ICs[J].Elektrotechnik und Informationstechnik,2015,132(6):262-268.

[5]Gordana JD,Fred H.Design ofWideband CICCompensator Filter for a Digital IF Receiver[J].Digital Signal Processing,2009, 19(5):827-837.

[6]翟琼华,欧毅,薛晨阳,等.SIW交指带通滤波器的设计与仿真[J].传感技术学报,2015,28(9):1379-1383.

[7]张飞,伍小宝.广义多相滤波及其应用[J].雷达科学与技术,2014,12(3):262-266.

[8]郭连平,田书林,王志刚,等.并行数字下变频中的NCO实现研究[J].仪器仪表学报,2012,33(5):998-1004.

[9]Aggarwal S,Meher P K,Khare K.Scale-Free Hyperbolic CORDIC Processor and Its Application to Waveform Generation[J].IEEE Transactions on Circuits and Systems,2013,60(2):314-326.

[10]祁艳杰,刘章发.基于Parallel-CORDIC的高精度高速度直接数字频率合成器的FPGA实现[J].电子学报,2014,42(7): 1392-1397.

[11]徐成,秦云川,李肯立,等.免缩放因子双步旋转CORDIC算法[J].电子学报,2014,42(7):1441-1445.

[12]胡煜.基于FPGA实现改进CORDIC算法研究[J].电子器件,2014,37(2):358-360.

[13]宋广怡.FIR滤波器的8路多相27子滤波器实现结构[J].无线电工程,2015,45(2):22-25,63.

[14]王炜珽,李淑华,张文旭.基于FPGA实现直接数字频率合成脉冲线性调频信号[J].现代电子技术,2015,38(10):10-15.

[15]刘恒,熊丰,孟瑞丽,等.微机械振动电场传感器闭环自激驱动建模及系统仿真[J].传感技术学报,2015,28(6):825-830.

[16]冯丹,任宏滨,李伟伟,等.反激式开关电源控制系统小信号模型[J].探测与控制学报,2015,37(5):89-93.

吉炜寰(1974-),男,河南郑州人,讲师,硕士,主要研究方向为自动控制与电子技术,weih74@126.com;

邹玉炜(1974-),男,河南安阳人,讲师,博士,主要研究方向为新能源发电与无线电能传输;

黄磊(1980-),男,河南商丘人,讲师,博士,主要研究方向为电机设计优化及控制系统。

Design of Improved High-Speed Digital Downconverter Based on Full Poly-phase Parallel Acceleration*

JIWeihuan1*,ZOU Yuwei2,HUANG Lei3

(1.Department of Electrical Engineering,Henan Polytechnic,Zhengzhou 450046,China;

2.College of Physics and Electrical Engineering,Anyang Normal University,Anyang He’nan 455000,China;

3.College of Electrical Engineering,Southeast University,Nanjing 210096,China)

Aiming to overcome challenge of high-speed data processing in broadband communication radar detection system,a full parallel accelerating computation based digital downconverter is proposed.Mixing module adopts pipelined coordinate rotation digital computer(CORDIC)to realize parallel processing of A/D dataflow,which can reduce data rate in single channel.Extraction module adopts poly-phase filter to decompose high-order convolution network,which can reduce unnecessary accumulative operation.The experiment result shows that the maximum working frequency increases from 131MHz to 255 MHz,and the improved design can effectively improve processing speed and reduce channel attenuation under existing hardware conditions.

digital downconverter;CORDIC;polyphase decomposition;decimation filter

C:1270

10.3969/j.issn.1005-9490.2017.01.027

TN45

:A

:1005-9490(2017)01-0142-05

项目来源:国家青年基金项目(51407027);河南省科技厅科技计划项目(142102210517)

2016-02-14修改日期:2016-03-09