高速PCM图像数据存储器

2017-09-06张耀峰李大全严帅张会新辛海华赵鹏飞张跃林史磊

张耀峰,李大全,严帅,张会新*,辛海华,赵鹏飞,张跃林,史磊

(1.中北大学电子测试技术国家重点试验室,太原030051; 2.仪器科学与动态测试教育部重点试验室,山西太原030051;3.北京宇航系统研究所,北京100076; 4.中国运载火箭技术研究院,北京100076;5.首都航天机械公司,北京100076)

高速PCM图像数据存储器

张耀峰1,2,李大全3,严帅3,张会新1,2*,辛海华3,赵鹏飞4,张跃林3,史磊5

(1.中北大学电子测试技术国家重点试验室,太原030051; 2.仪器科学与动态测试教育部重点试验室,山西太原030051;3.北京宇航系统研究所,北京100076; 4.中国运载火箭技术研究院,北京100076;5.首都航天机械公司,北京100076)

为了准确接收和存储某遥测系统的PCM、图像数据,设计了基于FPGA的高速PCM、图像数据采集存储器。存储器以FPGA为控制核心,并利用三星FLASH芯片K9WBG08U1M的交叉双平面页编程技术提高数据写入速度;为了实现存储器的多次上电存储并保证上一次上电存储的数据不被覆盖,我们在FPGA控制FLASH实现边擦边写的基础上开发了断电续存技术。设计的存储器具有数据写入速度快、可多次上电存储和抗干扰能力强等特点。

PCM;图像;FPGA;FLASH;断电续存

随着航空航天技术的发展,数据采集精度要求越来越高,数据传输速率越来越快,使得高速数据采集存储技术的需求越来越大。在卫星通讯、雷达通讯、信号测量等领域,信息的采集、存储和分析一直是我们面临的重要课题[1]。因此,具有采集存储速度快、容量大、体积小、抗干扰能力强、可靠性高等特点的存储器成为我们的研究方向。

1 存储器性能指标要求

1.1 PCM数字量指标要求

利用RS422接收一路PCM数据,存储器记录时间不超过1 h,码速率为5 Mbit/s,帧格式为96(列)×64(行),主帧同步码为EB90,副帧同步码为146F,上游设备在码同步信号的上升沿发送数据,存储器在码同步信号的下降沿接收数据,先接收到的是数据高位,后接收到的是数据低位。

1.2 图像数字量指标要求

利用LVDS接收一路图像信息数据,帧速率为8 ms/frame,一帧图像数据包含320 byte×512 byte的图像信息,接收的图像数据不大于6 000 frame。LVDS的负载串行传输速率为360 Mbit/s,LVDS的并行传输数据位数为10 bit,其中低8 bit为图像数据信号,高2 bit为指示信号,指示接收的图像数据是否为有效的图像数据。

1.3 其他指标要求

存储器在一次记录完成后,断电以后再上电,存储器还可以接着上次的断点位置再次启动记录。

2 设计方案

存储器采用模块化的设计的思路,各个模块既相互独立又相互配合[2]。存储器主要由电源转化模块、图像接收模块、PCM接收模块、逻辑控制模块、图像存储模块、PCM存储模块、读Flash缓存模块和网口接口模块组成。图像接收模块通过LVDS接收图像数据,PCM接收模块通过RS422接收PCM数据。逻辑控制模块选用Xilinx公司生产的Spartan-3AN系列的FPGA芯片XC3S1400AN作为主控芯片;为了匹配数据接收模块的数据接收码率与数据存储模块的数据存储码率,在FPGA内部构建了两个FIFO,分别为缓存1,缓存2;存储数据时为了判断两个FIFO何时满足可读取条件,并将满足可读取条件的FIFO中的数据写入对应的存储模块中,并且在回读数据时为了判断读取哪一个存储模块中的数据,在FPGA内部构建了数据调度模块。图像存储模块和PCM存储模块都选用Flash作为存储芯片。当需要读取图像数据或PCM数据至PC机进行数据处理时,FPGA读取对应的Flash中的数据至缓存3,当缓存3满足可读取条件时,将数据传送至网口控制器W5300的内部缓存中[3],最终数据通过网口传送至PC机。PC机可通过网口控制器W5300给FPGA发送“擦除”或“回读”指令,FPGA接收到指令后对两个Flash做出“擦除”或“读取数据”的操作。FPGA控制单元还需要配置PROM和晶振来发挥其主控作用。结构框图如图1所示。

图1 系统结构框图

3 硬件电路设计

3.1 电源模块电路

为了消除系统电源和外界信号对高速LVDS信号的串扰,图像数据接收需要信号隔离[4],隔离器的两端由不同的5 V电源供电,整个存储器控制电路的供电分为两个部分:隔离前端部分和隔离后端部分。存储器外接电压是28 V,为了分别提供两个隔离的5 V电压,在28 V电源输入后首先经过EMI滤波模块,输出的电压在两个DC/DC转换模块的作用下产生两个不同的5 V电压负责隔离前后的供电,如图2所示。

图2 EM I和DC/DC电路设计

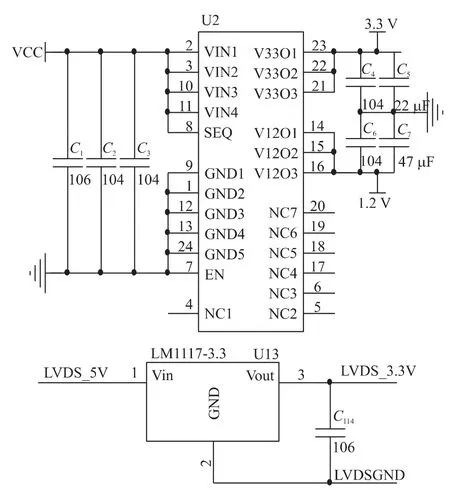

由于隔离前图像数据LVDS接收接口的供电电压为3.3 V,隔离后的FPGA供电电压为3.3 V和1.2 V,因此,在隔离前端和隔离后端分别使用了电压转换芯片LM1117-3.3 V和TPS70345,负责将5 V电压转换为各自需要的供电电压,如图3所示。

EMI滤波模块对系统输入的28 V电压进行滤波处理,这不但能够抑制系统自身产生的EMI噪声,同时可以为FPGA以及其他芯片提供无衰减的直流输入电压,滤除由电网加进来的各种干扰信号,使设备不受EMI噪声干扰[5]。

图3 电源模块电路设计

3.2 图像接收电路

LVDS技术的低压差分传输特性使其具有高速传输和抗干扰能力强等特点,故图像数据采用LVDS传输。为了接收由上游设备的10 bit低压差分信号串化器DS92LV1023发送来的图像数据,存储器接收接口芯片采用10 bit低压差分信号解串器DS92LV1224。由上游设备发送来的图像信号经过均衡器CLC014传输到解串器DS92LV1224,解串器DS92LV1224接收图像信号时FPGA为其提供同步时钟REFCLK,在这个时钟同步下将低压差分信号LVDSRX+/-解串为带有数据同步并行时钟RCLK的10 bit并行数据D[9:0][6],解串后的数据通过ADu1400C进行隔离,隔离后送给FPGA写入图像缓存。图像数据接收电路如图4所示。

3.3 PCM接收电路

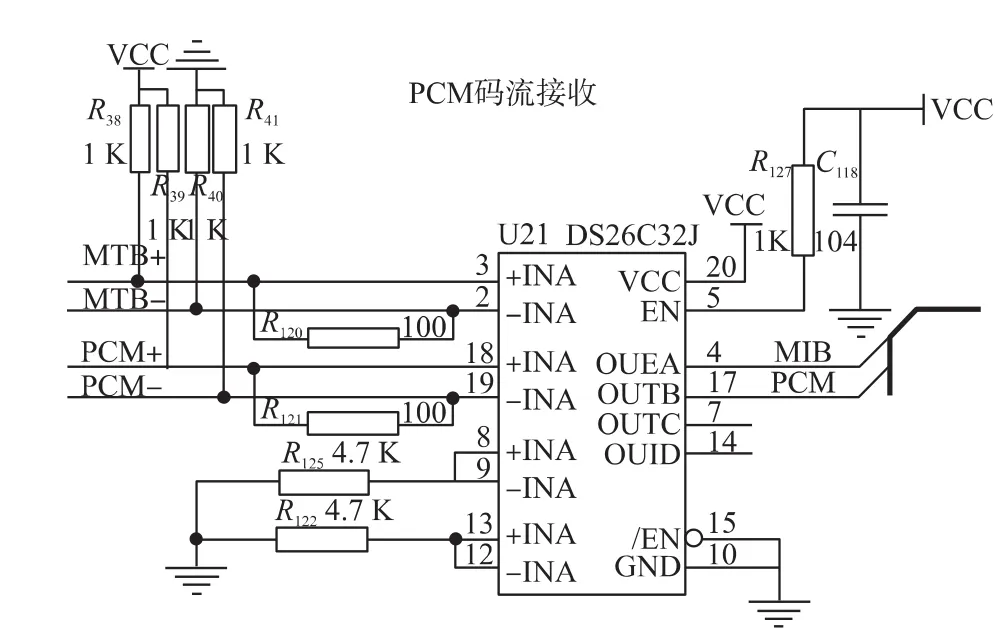

RS422接口采用差分方式传输数据,在通讯距离、抗共模干扰能力等方面性能都比较好,故PCM数据采用RS422接口接收。为了与上游设备的RS422发送接口芯片DS26C32J相匹配,存储器的RS422接收接口芯片采用DS26C32J。DS26C32J把由DS26C31J发送来的差分信号MTB+/-、PCM+/-还原成原来的MTB(码同步)、PCM信号[3],FPGA接收后将其写入FPGA内部构建的PCM缓存,接收电路如图5所示。

图4 图像接收电路

图5 PCM接收电路设计

3.4 数据接收框图

图6 数据接收示意图

图6所示为存储器接收图像数据和PCM数据时的数据传输过程,具体传输过程已在3.2节、3.3节中介绍。

4 时序设计

4.1 图像接收时序设计

接收的单幅图像数据帧格式为320×512,帧速率8ms/frame,LVDS的负载串行传输速率为360 Mbit/s。DS92LV1224采用的同步时钟频率为36 MHz,并行10位输出,36 Mbit×10=360 Mbit/s,满足串行数据传输速率要求。设计的图像数据接收时序如图7。上游设备8ms传送一帧320×512的图像数据,一帧的数据量大小为320×512=160 kbyte,LVDS接收接口DS92LV1224接收160 kbyte的图像数据需要的时间为160×1024/36 MHz=5.46 ms<8 ms,这说明图像数据在整个传输过程中LVDS不能一直保持满负荷传输状态。然而利用LVDS技术传输数据时,需要实时进行数据同步,因此上游设备的数据发送端在图像数据传输的间隙(即8 ms~5.46 ms=2.54 ms时间段内)填充了无效数据,以实现数据传输时的数据同步。8 ms传输一帧的时间内,5.46 ms是有效图像数据传输时间,2.54ms是无效图像数据传输时间,满足了8 ms接收一帧图像数据的要求。在传输过程中,帧同步信号和行同步信号作为图像数据转换成10 bit LVDS数据的高两位,当高两位为11、10、01时,指示接收到的图像数据为有效图像数据,FPGA在同步时钟的作用下接收这10 bit并行数据并将其写入内部构建的图像缓存即缓存2,当高两位为00时,指示传输的图像数据为无效图像数据[3],FPGA不对其进行接收。

图7 图像数据接收时序

4.2 PCM接收时序设计

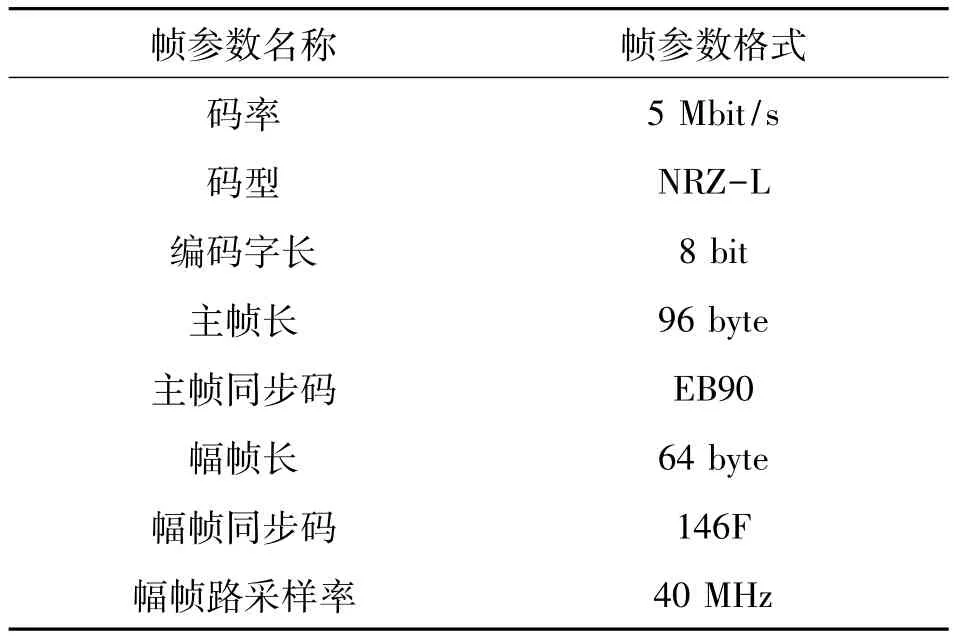

存储器接收1路码率为5 Mbit/s的PCM数据,PCM数据帧格式如表1。

表1 PCM数据帧格式表

图8是PCM数据传输时序。存储器在码同步信号的作用下接收PCM数据,一个同步信号周期对应一位数据,8个同步信号周期对应数据的一个字节,一个字节中先接收高位后接收低位,字节之间没有空闲位。上游设备在码同步信号的上升沿发送数据,存储器在码同步信号的下降沿接收数据。

图8 PCM数据传输时序

存储器由RS422接收接口接收PCM数据时,由于没有字同步信号,在数据接收时不能判断哪一位是数据的起始位,而FPGA需要将8 bit串行数据转换成8 bit并行数据并写入PCM缓存即缓存1,这转换时有可能将不同字节的数据拼接在一起,导致接收混乱。解决这一问题的关键在于帧同步码EB90、146F,FPGA接收数据时内部构建一个16 bit的移位寄存器,先移位接收15 bit数据,然后左移1 bit,补接收1 bit,判断这16 bit数据构成的两个字节是否为EB90或146F,如果不是,左移1 bit补接收1 bit,继续判断是否为EB90或146F,如此往复,当判到EB90或146F后,再移位接收96×8=768 bit,若还是EB90或146F,说明串并转换成功,FPGA可将数据写入PCM缓存中,若不是EB90或146F,重新开始移位接收判断。

4.3 FLASH存储时序设计

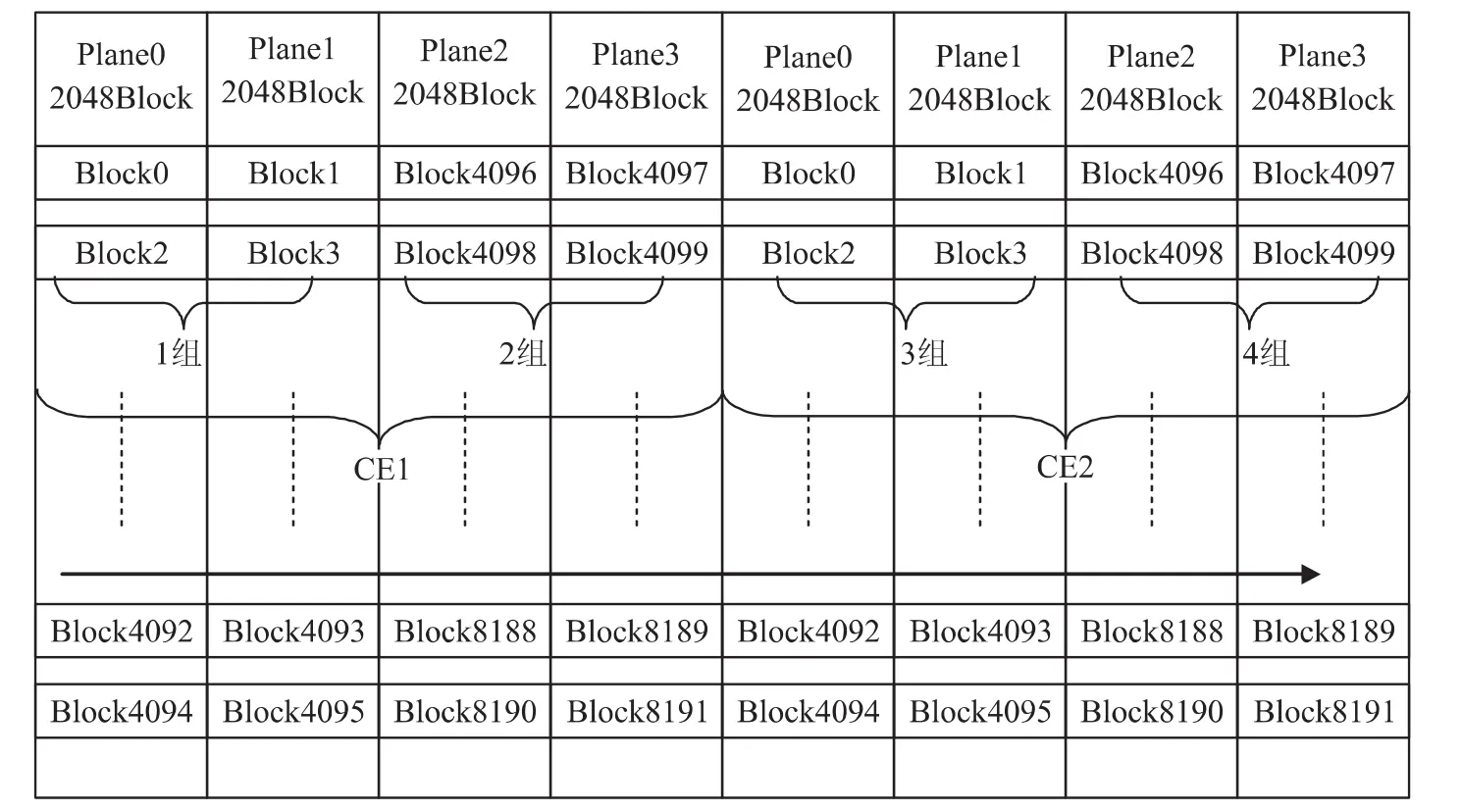

依照给出的性能指标要求,存储PCM数据的最大数据量为(1×60×60×5 M)÷8÷10243=2.1 Gbyte,存储图像数据的最大数据量为320×512×6 000÷1 0243=

0.92 Gbyte,图像存储Flash和PCM存储Flash都采用单片双片选4G芯片K9WBG08U1M,满足指标要求,块组成平面结构图如图9所示[7]。

图9 块组成平面结构图

存储器工作时,FPGA内部构建的数据调度模块实时判断缓存1、缓存2中的数据量是否达到4 kbyte,如果其中有一个缓存中的数据量达到4 kbyte,FPGA便将缓存中的数据写入对应的存储模块中。由于Flash的单平面顺序页编程、单平面交叉页编程和双平面页编程操作模式已满足不了高速数据存储的要求,而交叉双平面页编程模式可将数据写入速度提高到30 Mbyte/s[8],故FPGA向Flash写PCM或图像数据时,采用Flash的交叉双平面页编程模式。交叉双平面页编程是在一个双平面进行页编程时候,切换片选信号执行另一个双平面页编程[9]。操作过程如图10所示。

图10 交叉页编程操作流程图

从图10可以看出在第1组双平面的写寄存器时间结束后,通过片选信号CE切换至第3组双平面并进入写寄存器时间,第3组写寄存器时间结束之后,通过片选信号CE切换至第2组双平面并进入写寄存器时间,第2组写寄存器时间结束之后,通过片选信号CE切换至第4组双平面并进入写寄存器时间,第4组写寄存器时间结束之后,通过片选CE信号切换至第1组,如此往复,整个操作过程中所有的页编程等待时间都被充分利用,每时每刻数据都在写入寄存器,没有等待时间,因此在交叉双平面页编程模式下Flash存储数据的速度即为数据写入寄存器的速度,

此时Flash存储数据的速度达到最大,设计的存储器

便具备了数据写入速度快的特点。

4.4 断电续存技术

按照设计指标要求,存储器在本次数据采集后,下电以后再上电,存储器还可以接着上次断电时存储的断点位置进行数据存储,为此,我们开发了断电续存技术。存储操作采用边擦边写的方式进行,操作流程图如图11所示。

图11 边擦边写流程

由于Flash的坏块检测、擦除、编程操作都在交叉双平面模式下进行,存储器工作时按照以上流程图操作后,每次下电之后都会有一组被擦除的FF块,再次上电时只需要检测到这一组FF块便找到了存储器下电时的数据存储断点位置,然后在断点位置处再次进行数据存储就可以实现断电续存的功能了。

5 数据测试结果

存储器通过接收由上游设备发送来的PCM数据来验证数据接收的正确性。上游设备发送PCM递增数,存储器接收并存储后将数据传送给上位机,并由上位机软件分析。图12为回读至上位机并由上位机软件显示的部分PCM数据,从图中可以看出PCM数据的主帧同步码为EB 90,副帧同步码为146F,在上位机软件中显示的完整PCM数据为:主帧长96路、副帧长64路、帧有效数据为00~5C的递增数。接收到的PCM数据满足设计指标要求。

图12 PCM数据片段

存储器通过接收由上游设备发送来的图像数据来验证数据接收的正确性。存储器将接收并存储的图像数据传送给上位机,上位机利用图像还原软件对图像数据逐帧播放分析。图13是回读的图像数据片段,使用图像还原软件对图像数据进行处理,得到图像如图14所示。图像数据分析无误,满足设计指标要求。

图13 图像数据片段

图14 还原后的图像

6 结论

设计的存储器可按照PCM数据、图像数据指标要求接收一路PCM数据和一路图像数据,并具有断电续存的功能。数据传输时,存储器采用RS422、 LVDS接口接收数据,这两种接口芯片都采用差分方式传输数据,抗干扰能力强;数据存储时,采用flash的交叉双平面页编程模式,大大提高了数据写入速度,具有高速存储的特点。

[1]刘蕴才.无线电遥测遥控[M].北京:国防工业出版社,2001: 7-8.

[2]魏敏,刘文怡,王金陵,等.基于交叉双平面技术的图像采集存储系统[J].电视技术,2013,37(15):63-66,81.DOI:10.3969/ j.issn.1002-8692.2013.15.018.

[3]邸丽霞.双通道遥测数据存储测试系统的设计[D].中北大学,2014.

[4]菅少坤.一种具有断电续存功能固态存储系统的设计[D].中北大学,2014.

[5]韦斯顿.电磁兼容原理及应用[M].第2版.杨自佑,王守三,译.北京:机械工业出版社,2006:601-660.

[6]张健,吴晓冰.LVDS技术原理和设计简介[J].电子技术应用,2000(5):59_61.

[7]Samsung Electronics.K9WBG08U1 M Advanced Flash Memory DataSheet[Z].2007.

[8]马志刚,刘文怡,凌伟,等.基于PCI和LVDS的高速数据存储系统的设计[J].电子技术应用,2014,40(4):80-83.DOI:10.3969/j.issn.0258-7998.2014.04.004.

[9]吴鹏.高速实时FLASH阵列数据采集系统研究与实现[D].南京:南京理工大学,2007.

张耀峰(1990-),男,汉族,山西忻州人,学生,现为中北大学在读硕士,研究方向为动态测试技术与仪器,1511688590 @qq.com;

张会新(1980-),男,汉族,黑龙江牡丹江人,讲师,现为北京航空航天大学在读博士,研究方向为抗过载存储技术及动态测试技术与仪器,zhanghx@nuc.edu.cn。

High Speed PCM Image Data Acquisition M emory

ZHANG Yaofeng1,2,LIDaquan3,YAN Shuai3,ZHANG Huixin1,2*,XIN Haihua3,ZHAO Pengfei4,ZHANG Yuelin3,SHILei5

(1.National Key Laboratory for Electronic Measurement Technology,Shanxi Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science and Dynamic Measurement of Ministry of Education,Taiyuan 030051,China;3.Beijing Institute of Aerospace Systems Engineering,Beijing 100076,China;4.China Academy of Launch Vehicle Technology,Beijing 100076,China; 5.Capital Aerospace Machinery Corporation,Beijing 100076,China)

In order to receive PCM data and image information from a remotemetering system exactly,we designed a memory tomeet the requirement.The memory uses FPGA as the control center and makes use of the interleave two-plane page program technique of Samsung flashmemory K9WBG08U1M to raise the datawriting speed.Also on the foundation of using the operation of erasing and writing meanwhile of memory,the technology of continuous memorymethod,we developed tomake sure that the previous stored data can not be covered when thememory is powered on several times.Thememory we designed has the characteristics of high data writing speed,capability of storing data when powered on several times and ability of high resistance to interference.

PCM;image;FPGA;FLASH;continuousmemory

C:6140

10.3969/j.issn.1005-9490.2017.01.010

TN79

:A

:1005-9490(2017)01-0049-06

2016-01-14修改日期:2016-02-24