基于FPGA的多通道多量程数据采集系统设计

2017-09-03冯传均戴文峰

冯传均,何 泱,戴文峰

(中国工程物理研究院流体物理研究所 脉冲功率科学与技术重点实验室,四川 绵阳 621900)

基于FPGA的多通道多量程数据采集系统设计

冯传均,何 泱,戴文峰

(中国工程物理研究院流体物理研究所 脉冲功率科学与技术重点实验室,四川 绵阳 621900)

为了实现多路模拟信号的准确采集、记录和显示,设计了一种基于FPGA的多通道、多量程数据采集系统。该系统采用FPGA作为主控芯片,通过FPGA内部的控制模块控制A/D数据转换和UART接口数据传输,并在FPGA内部完成数据处理。FPGA与上位机之间采用RS-232串口实现数据通信,上位机采用Viusal Basic编写监控界面,实现远程控制和显示。该系统具有性能稳定、实时性强、操作界面友好、可扩展性强等特点。

数据采集;FPGA;串口通信;上位机

0 引言

数据采集技术是信息科学的重要分支,被广泛应用于现代工业生产、国防及科学研究等方面。数据采集、传输及监控系统是过程控制、状态监测、故障诊断、质量检测等系统的重要组成部分。怎样快速完成多路模拟信号的同步采集,并对采集到的信号进行快速处理和显示,以满足工艺现场的控制要求,是数据采集技术研究的一个重要问题[1-2]。本文以Altera公司的FPGA作为主控芯片,结合Maxim公司的高速ADC以及TI公司兼容RS-232标准的芯片,实现对8路模拟电压信号(±10 V、±5 V、0~10 V、0~5 V)的实时采集和传输[3],上位机软件采用Viusal Basic编写监控界面,实现远程控制和数据显示。

1 系统总体结构设计

数据采集系统主要由A/D转换电路、FPGA单元电路、数据通信和上位机监控界面4部分组成,如图1所示。

图1 系统结构框图

A/D转换电路采用Maxim公司的MAX197。由FPGA内部的A/D控制模块向MAX197发送采样控制指令,控制A/D转换芯片将模拟信号转换为数字信号,转换精度为12 bit。

FPGA采用Altera公司Cyclone IV系列的EP4CE15F17 C8N,FPGA芯片作为系统的主控芯片,控制A/D转换芯片实现数据转换并对转换结果进行处理,同时通过UART接口控制[4],实现FPGA与上位机串口通信。

FPGA与上位机之间采用RS-232串口实现数据通信,上位机通常具备标准的串行接口,FPGA与RS-232串口间采用电平转换芯片MAX232实现TTL/COMS电平转换,FPGA内部模块实现UART接口控制。

上位机监控软件采用Visual Basic进行界面设计,实现数据采集系统的采样通道、电压范围、电压极性等参数的远程控制,并对采集的数据结果进行记录、显示及绘制曲线。

2 系统硬件设计

2.1 A/D转换电路

2.1.1 MAX197芯片介绍

MAX197是Maxim公司推出的具有12位测量精度和多量程(±10 V、±5 V、0~10 V、0~5 V)的高速A/D转换芯片,转换时间为6 μs,采用+5 V单电源供电,具有8路输入通道,提供并行接口-8位三态数据I/O口。

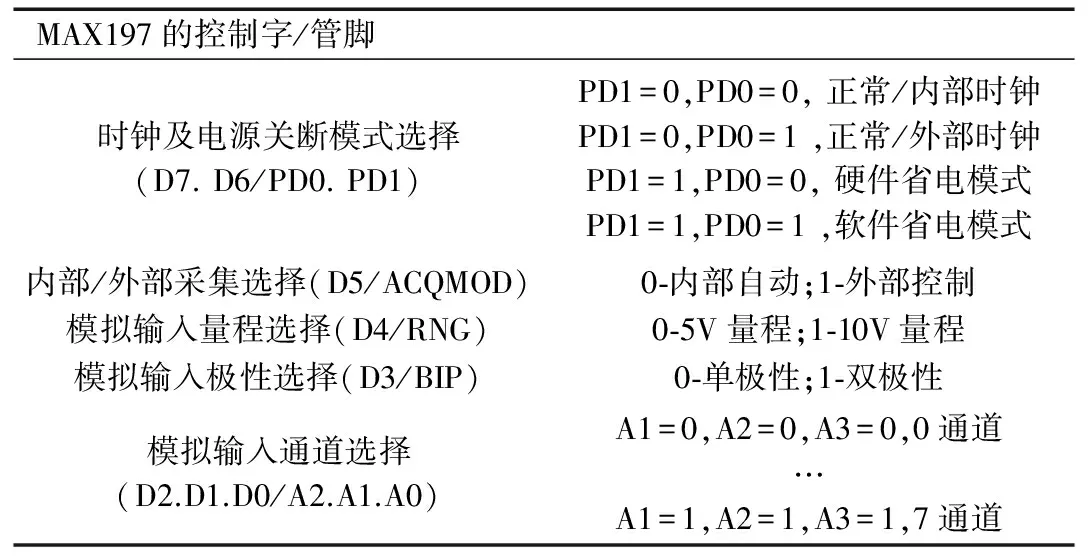

2.1.2 MAX197的控制字

MAX197芯片的控制字节的写入和数据的读出都是由8位并行接口实现[5]。FPGA可以将MAX197芯片作为一个I/O来寻址,使用方便。MAX197芯片进行数据采集转换前需要先对其进行初始化,通过设置控制寄存器,确定其采样转换的通道、量程和极性等。控制寄存器格式如表1所示。

表1 MAX197控制寄存器格式

2.1.3 MAX197控制接口电路

MAX197是一种通用A/D芯片,可以与多种微机接口配合。对于本文选用的FPGA芯片,FPGA的D1~D8与MAX197的D0~D7相连,既用于输入MAX197的控制字,也用于读取转换结果数据。FPGA的E1~E5分别连接MAX197的INT、HBEN、RD、WR、CS引脚。INT为转换识别信号,当数据转换完毕时INT脚产生中断信号;HBEN为12位数据,高4位或低8位有效控制位,高电平时高4位数据有效,低电平时低8位数据有效;RD为读信号控制;WR为写信号控制;CS为片选控制。选择MAX197为低功耗工作方式,故置MAX197的SHDN脚为高电平;采用内部时钟模式,CLK脚接100 pF电容,时钟频率为2 MHz;芯片采用内部基准电压,故REF、REFAD通过电容器接地,设计接口电路如图2所示。

图2 FPGA和MAX197接口电路

2.2 数据通信电路

FPGA与上位机之间采用RS-232串口通信,由于FPGA的I/O脚信号电平和RS-232的标准不一样,FPGA与RS-232之间采用电平转换芯片MAX232,实现TTL/COMS电平之间的转换。

MAX232芯片是由TI公司推出的一款兼容RS-232标准的芯片。该芯片采用5 V单电源供电,支持3.3 V/5 V电平,采用Lin BiCMOSTM工艺技术,一片MAX232芯片包含两个驱动器及两个接收器。MAX232电平转换电路图如图3所示。

图3 MAX232电平转换电路图

3 FPGA软件设计

FPGA是系统的核心控制部分,控制A/D转换芯片完成模/数转换,通过内部UART接口控制,实现与上位机之间串口通信。FPGA软件采用Verilog HDL编程语言在Quartus II软件下完成[6]。软件采用自顶向下的设计方法,分别完成各个模块的代码编写。FPGA内部控制模块包括:波特率产生模块、UART接收控制模块、MAX197控制模块和UART发送控制模块。波特率产生模块将系统提供的外部时钟转换为UART收发模块需要的频率。UART接收控制模块按照设定的数据接收协议,从串口接收上位机发送的控制命令,并对接收的数据进行缓存、解析处理后将控制命令写入A/D转换控制模块。A/D转换控制模块根据控制命令向MAX197发送采样控制指令,控制A/D转换芯片完成数据转换,转换结果经过缓存、数据处理后写入UART发送控制模块。UART发送控制模块按照设定的数据发送协议将数据结果通过串口发送给上位机。FPGA控制原理图如图4所示。

3.1 波特率产生模块

在电子通信领域,波特率即调制速度,它是对符号传输速率的一种度量,1 b/s表示每秒传输1个符号。波特率产生模块的功能是产生与RS-232串口通信波特率同步的时钟,其基本思路是对系统输入时钟进行分频得到需要的波特率。本设计FPGA输入时钟为50 MHz,波特率选择的是9 600 b/s,分频计数值为5 207。

图4 FPGA控制原理图

3.2 UART接收控制模块

UART接收控制模块主要实现对串行数据的串并转换,转换的串行数据按照既定的数据帧格式进行输出。UART数据接收协议采用1位起始位、8位数据位、1位停止位、无奇偶校验位的格式,在9 600 b/s波特率下,UART数据采集步骤如下:

(1)空闲状态,等待数据起始位0;

(2)根据起始位的标志,判断UART时序起始;

(3)由低位到高位串行接收8位数据;

(4)判断结束位1,一帧数据接收完毕。

3.3 UART发送控制模块

UART发送控制模块主要实现对并行数据的并串转换,转换的串行数据按照既定的数据帧格式进行输出。UART数据协议采用1位起始位、8位数据位、1位停止位、无奇偶校验位的格式,在9 600 b/s波特率下,UART数据采集步骤如下:

(1)初始化状态,等待UART数据发送使能标志位;

(2)串行数据发送格式为:先发送数据起始位,8位数据由低到高依次发送,最后发送停止位;

(3)发送完成回到初始状态,等待下一次发送使能。

3.4 MAX197控制模块

MAX197控制模块用于产生MAX197芯片正常工作所需要的时序,MAX197芯片工作过程包括:等待(IDLE)、控制寄存器初始化(SEND_CTRLDATA)、等待转换结束(WAIT_INT)、读转换完成数据的低8位(READ_LOW)、读转换完成数据的高4位(READ_HIGH)、判断下一次操作(STATE_JUDGE)共6个状态,MAX197芯片的控制状态机如图5所示。

图5 MAX197芯片控制状态机

4 上位机监控界面设计

上位机监控界面采用Visual Basic软件开发工具实现[7]。该软件具有良好的界面设计能力,串口通信相关控件功能强大、完善且易用。上位机控制界面如图6所示,主要控件包括:串口管理模块、数据采集设置模块、多通道数据显示模块、波形绘制窗口。串口管理模块用于设置串口号、波特率、数据位、停止位和奇/偶校验位等参数;数据采集模块设置A/D转换芯片的工作方式、时钟模式、采样电压范围、采样电压极性、采样通道;多通道数据显示模块对A/D转换完成的数据进行显示;波形绘制窗口对采集的数据进行波形曲线绘制,横坐标为时间,纵坐标为数据结果。

图6 上位机控制界面

5 结论

本文设计的基于VB和FPGA的数据采集系统,能够实现多通道、多量程数据的在线监测。该系统利用FPGA内部控制模块,实现A/D芯片A/D转换控制和UART接口控制,简化了硬件电路设计;上位机软件通过图形界面实现采样通道、采样参数设置,A/D转换结果的存储、处理和十进制显示等功能。系统采用模块化设计,通过修改参数设置,可运用到其他数据采集系统中。

[1] 周学礼,叶飞,吕忠斌.基于VB的多路数据采集系统设计[J].电气工程,2010(5):9-12.

[2] 刘军,岳兴莲,何国国,等.基于FPGA的数据采集系统的设计[J].微型机与应用,2009,28(19):13-15.

[3] 李华,刘宝盈,刘萌,等.基于FPGA的多路数据采集与传输系统设计[J].电子测试,2014(18):29-31.

[4] 赵乐森,王旭柱.基于FPGA与USB2.0的实时数据采集与处理系统[J].微型机与应用,2011,30(17):25-27.

[5] 颜延秦.12位MAX197和51单片机实现数据采集设计[J].能源技术与管理,2006(3):75-77.

[6] 韩彬,于潇宇,张雷鸣.FPGA设计技巧与案例开发详解[M].北京:电子工业出版社,2014.

[7] 辛本柱.新手学Visual Basic[M].北京:北京希望电子出版社,2010.

The design of a multi-channel variable-range data acquisition system based on FPGA

Feng Chuanjun, He Yang, Dai Wenfeng

(Key Laboratory of Pulsed Power, Institute of Fluid Physics, CAEP, Mianyang 621900, China)

To satisfy the need of acquiring, recording and displaying multiple analog signals, this paper presents a multi-channel variable-range data acquisition system based on FPGA. This system introduces an FPGA chip as the main controller, which implements the A/D transition, the UART port communication, and data processing. The controller communicates with the upper machine through an RS-232 series port. The upper machines runs a graphic user interface that programmed in Visual Basic to manipulate and supervise the system remotely. This system has the characteristics of stable and real-time performance, friendly user interface, and easy to extend.

data acquisition; FPGA; serial communication; upper machine

TP274+.2

A

10.19358/j.issn.1674- 7720.2017.15.011

冯传均,何泱,戴文峰.基于FPGA的多通道多量程数据采集系统设计[J].微型机与应用,2017,36(15):38-40,44.

2017-03-05)

冯传均(1989-),男,本科,主要研究方向:脉冲功率技术及测控技术。