24 GHz CMOS功率放大器芯片设计

2017-08-11谢蓉芳吴风松

彭 娜,谢蓉芳,陈 珂,吴风松,叶 松

(成都信息工程大学 通信工程学院,四川 成都 610225)

24 GHz CMOS功率放大器芯片设计

彭 娜,谢蓉芳,陈 珂,吴风松,叶 松

(成都信息工程大学 通信工程学院,四川 成都 610225)

24 GHz频段在车载雷达和无人机方面应用广泛,但面临着提高集成度、降低成本的挑战,而CMOS毫米波芯片因其成本低和易于系统集成的优点,在毫米波通信系统的应用中占据着越来越重要的地位。因此提出一种基于CMOS工艺的24 GHz功率放大器芯片的设计方法,包括24 GHz 功放芯片的应用,以及有源器件的版图对其特征的影响及设计,给出了CMOS毫米波无源器件的特征及建模设计,最后对无源与有源器件进行了联合仿真,得到一个PAE为17%、Pout为10.7 dBm的单级24 GHz功率放大器芯片。

毫米波集成电路;功率放大器;CMOS;雷达

0 引言

24 GHz频段是车载雷达和无人机应用的主流频段。当前,毫米波雷达系统以其抗物理环境依赖性的优势在主流汽车产业应用广泛,但多采用国外毫米波雷达传感器,雷达产业被国外厂商控制着。国内来看,国内还没纳入整个全球雷达统计的范畴,但这两年起步较快,各雷达厂商数量不会低于20家,对自主可控的研究迫在眉睫[1]。

功放是毫米波雷达系统射频部分的重要器件,其性能对整个雷达系统起着关键作用,现阶段的毫米波雷达系统的射频部分大多使用化合物工艺如GaAs、SiGe来达到较好的性能,但是集成度不高,而CMOS工艺是提高系统集成度的最佳选择。随着深亚微米和纳米CMOS工艺的成熟,设计和实现低成本的毫米波CMOS集成电路已成为可能[2],CMOS工艺线长度不断减少,从0.25 μm、0.18 μm,到40 nm、28 nm以及到被极为看好的16 nm。使得工艺的截止频率Ft能达到数百GHz,为毫米波电路设计提供极为良好的设计基础。本芯片设计采用某工艺厂商40 nm Low Power CMOS 工艺实现, CMOS 工艺除了相较于SiGe等工艺的低成本及整系统集成(full system integration)等优势外还有相对稳定的技术支持,从而受到业界的欢迎,在CMOS毫米波芯片技术领域,国内的研究相比国外处于相对落后的阶段[3]。因为CMOS工艺有着衬底损耗大,输出功率低的缺点,对毫米波电路设计提出了巨大的挑战,主要体现在需要采用全电路三维电磁场仿真,对电感及信号连线进行电磁场仿真,根据电路的特点优化版图的结构,从而减少损耗提高电路效率,结合Cadence进行联合仿真[4]。

1 功率放大器的基本结构

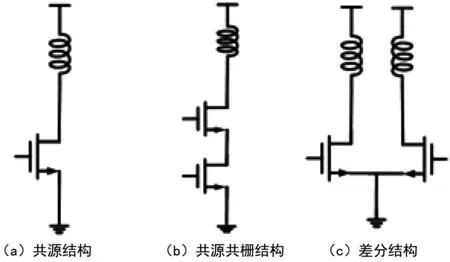

功率放大器基本的结构有共源结构、共源共栅和差分结构3种,如图1所示。

图1 功率放大器的基本结构

共源结构的噪声性能较优,并且在功放电路中有较低的电压供电、较高的效率和较好的线性度。相对于共源结构,共源共栅结构可以很好地隔离输入与输出信号,能够提高电路的增益,提高稳定性,对匹配的设计也有一定的帮助[5-6]。 差分工作的电路有更强的环境噪声抗干扰能力,提高可得到的最大输出电压摆幅,拥有更高的线性度,差分电路的众多优点使其广泛用于放大器特别是功率放大器的设计,电路设计使用共源结构来得到更高的效率和线性度。

2 24 GHz CMOS有源器件版图设计

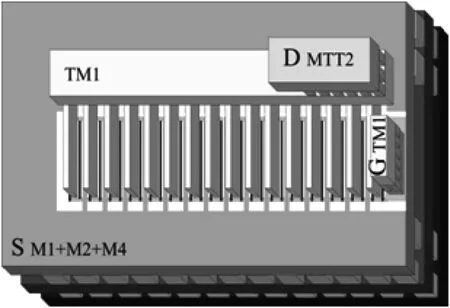

因为CMOS 工艺晶体管较低的截止频率Ft限制了其所能达到的最大增益,比如在24 GHz 频率处,40 nm CMOS工艺中晶体管的最大增益(Gmax)仅仅只有 15 dB 左右,如何改进电路结构以提高晶体管在毫米波频段的增益是 CMOS 功率放大器设计的又一挑战[5]。毫米波电路由于高工作频率,有源器件的Ft和Fmax对电路性能的影响很大,有源器件的版图结构,包括有源器件本身的版图,即栅指数目、栅指宽度的选择及引出连接线的结构,有源与无源之间的互连线必须当作传输线来考虑[5]。确定好栅指数目和宽度,对于固定的偏置电流,Ft是固定的,Fmax会随着栅指宽度变化,采用多栅指数,小栅指宽度能提高Fmax。栅漏电容和栅极电阻对Fmax的影响最大,在优化连接线时应最大限度地减少这两个值,源极电阻和栅漏寄生电容的优化,提升MSG(最大稳定增益)[7-8]。本设计有源器件的版图如图2所示,有源器件栅极与M3连接,从M3打孔到TM1引出,采用过孔的结构目的是减少寄生电阻。源极需要通过较大电流,则需要足够的金属宽度来承载电流,可根据具体电路来确定金属厚度,源极用M4、M2和M1连接到地,绕有源器件一周,这样做既有足够的金属宽度及厚度通过电流又能减少非对称。漏极从M2往上层金属打孔到M8引出,用TM1连接然后打孔到顶层金属MTT2,增加金属厚度能减少寄生电阻,通过较大电流,且有利于无源器件的连接。

为了能得到更好的性能,在高级设计系统(Advanced Design System,ADS)仿真工具中通过Loadpull仿真和MAXGAIN仿真,考虑AM-AM和AM-PM的值,以及MOS管的FT和FMAX,多次仿真、修正MOS 管参数,有源器件模型参数选择20*8为最佳,其偏置为Vd1.1 V、Vg0.75 V,单路功放在功率级输入为 0 dBm功率时,最大输出功率为12.5 dBm。

图2 有源器件的版图

3 CMOS毫米波无源器件及匹配网络设计

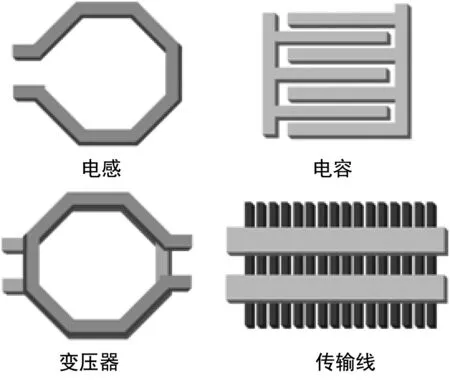

CMOS工艺厂家工艺库中的无源器件电感、电容适用于一定的频率范围,工作频率在毫米波段的无源器件需要建模设计[9],图3为CMOS毫米波电路设计常用到的无源器件电感、电容、变压器以及带屏蔽层的差分传输线的结构。电路中的电感、电容的选择考虑到电容的Q值在高频段变低的现象,一般以20 GHz为界,20 GHz 以上采用电感耦合。

图3 CMOS毫米波无源器件

在毫米波频段,连接线必须看成是分布系统即传输线。传输线能实现高精度小电感值的电感,并且其品质因数能达到20左右,可以满足阻抗匹配、扼流及谐振回路等要求[10]。毫米波电路常常大量使用传输线用于阻抗匹配及信号传输。通常,传输线的面积较大,相比于其他器件占用芯片更大的比重,会进行弯曲处理,以减小芯片面积[11]。作为阻抗匹配和信号传输的传输线要尽可能短,寄生耦合效应随着工作频率的提高而愈加显著,合理布局显得尤为重要,每一部分的无源器件都要经过大量时间的电磁仿真优化。

无源器件建模使用3D电磁仿真工具HFSS和Momentum仿真工具对比验证,其设计的方法是在这2种工具中,建立工艺的衬底及介质等模型,用顶层金属来设计源器件的结构,通过改变这些无源器件的结构,优化得到所需要的指标。本设计的扼流电感用顶层金属来实现,结构为八边形,通过改变线宽和半径来优化其性能。LC匹配网络,电感用螺旋结构。

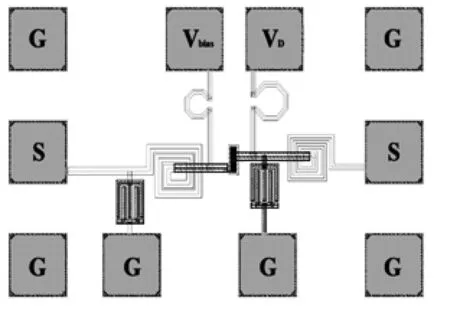

4 版图设计及仿真

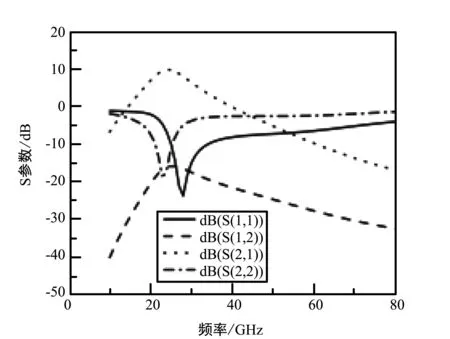

电路性能有源器件经过优化,同时无源器件在电磁仿真工具中经过建模优化,需要将有源和无源部分整合起来,才能得到整个电路的性能。无源部分经过电磁仿真之后生成S参数,这个结果包含了整个无源部分的Z、Y参数[12],将之导入到schematic中结合有源器件仿真,如图4所示,有源与无源之间的互连线,在无源器件建模时考虑进去,处理不好会导致频率的偏移,偏置线用λ/4走线可以防止微波信号泄露。无源部分仿真优化之后,将电磁仿真工具中优化后的无源部分在Cadence Virtuoso layout中画出来,PAD部分包括GSG PAD和供电PAD,由顶两层金属和AL构成,测试时信号用探针从GSG PAD引入。图4为24 GHz单级功放芯片的版图,单级功放芯片的饱和输出功率为10.7 dBm,功率附加效率PAE为17%,增益为9 dB,如图5所示。

图4 24 GHz功功率放大器芯片版

(a)小信号

(b)大信号图5 电路的大小信号性能

5 结束语

详细介绍了CMOS毫米波芯片设计的流程及版图考虑,包括设计工艺的选择依据,有源器件的版图需要考虑的问题,无源器件的建模仿真和版图考虑,最后介绍了无源器件和有源器件的整合仿真,以及基于整个流程设计的24 GHz单级功放芯片的设计以及其性能。毫米波电路设计的过程是不断地优化与权衡的过程,整个过程繁琐复杂,需要反复调整多次,无源器件需要经过不断的电磁仿真优化,直到电路达到最好的性能。

[1] 赵青晖. 毫米波雷达技术及应用大解析(2016-12-12)[DB/OL]. http://www.leiphone.com/news/201612/owHDk93xVS9g1gUC.html.

[2] 夏立诚,王文骐,祝远渊.毫米波CMOS集成电路的现状与趋势[J].半导体技术,2007,32(3):23-24.

[3] 陈波.基于CMOS工艺的毫米波发射机芯片设计[D].上海:华东师范大学,2016.

[4] 曹佳.基于CMOS工艺的微波毫米波集成电路关键技术研究[D].南京:东南大学,2014.

[5] 黄鹏.基于CMOS工艺的变压器耦合毫米波功率放大器芯片设计[D].成都:电子科技大学,2014.

[6] 李智群.射频集成电路与系统[M].北京:科学出版社,2008.

[7] Di Xianzhao,Patrick R.CMOS 60-GHz and E-band Power Amplifiers and Transm-itters [M].Switzerland: Springer,2015.

[8] Ali M N,Hossein H. mm-Wav-e Silicon Technology 60 GHz and Beyond[M].NEW YORK:Spinger Science + Business Me-dia,2008.

[9] 陈林辉.60 GHz CMOS发射机的设计与实现[D].南京:东南大学,2015.

[10]郭开喆.60 GHz CMOS 功率放大器设计[D].成都:电子科技大学,2013.

[11]黄映乾.基于CMOS技术的60 GHz毫米波功率源研究[D].杭州:浙江大学,2012.

[12]William R E. S-Parameter-Based IC Interconnect Transmission Line Characterizati-on[C]∥IEEE J. Transactions on Components,Hy-brids and Manufacturing Technology,1992:483-485.

Design of 24 GHz CMOS Power Amplifier Chip

PENG Na,XIE Rong-fang,CHEN Ke,WU Feng-song,YE Song

(College of Communication Engineering,Chengdu University of Information Technology,Chengdu Sichuan 610225,China)

24 GHz frequency band is widely used in vehicular radar and unmanned aerial vehicle(UAV),but it’s use at present faces the challenges of improving integration and lowering cost. The CMOS millimeter wave integrated circuit(IC) is becoming more and more important in the application of millimeter wave communication systems because of its merit of lower costs and high system integration. This paper presents a CMOS IC design of 24 GHz power amplifier,including the impact of layout design on the active device performance. The approach of the whole circuit simulation with dynamic link including passive and active devices is illustrated with an example design of 24 GHz power amplifier which achieves PAE of 17% and Pout of 10.7 dBm. This is the best performance in similar works.

millimeter wave integrated circuit; power amplifier; CMOS; radar

2017-05-09

彭 娜(1990—),女,硕士研究生,主要研究方向:微波集成电路设计。叶 松 (1967—), 男, 教授,主要研究方向:射频微波集成电路设计。

10. 3969/j.issn. 1003-3114. 2017.05.18

彭娜,谢蓉芳,陈珂,等.24 GHz CMOS功率放大器芯片设计[J].无线电通信技术,2017,43(5):82-85.

[PENG Na,XIE Rongfang,CHEN Ke,et al. Design of 24 GHz CMOS Power Amplifier Chip [J]. Radio Communications Technology,2017,43(5):82-85.]

TN454

A

1003-3114(2017)-05-82-4