MEMS片上绝缘性能测试高阻标准件研制

2017-08-08乔玉娥翟玉卫梁法国郑世棋

乔玉娥,刘 岩,丁 晨,翟玉卫,梁法国,郑世棋

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

MEMS片上绝缘性能测试高阻标准件研制

乔玉娥,刘 岩,丁 晨,翟玉卫,梁法国,郑世棋

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

针对MEMS圆片测试系统中绝缘性能测试的准确测量问题,利用GaAs半导体材料硼离子注入后的高绝缘特性,研究制作片上高值电阻标准件的方案,研制出一种基于GaAs衬底的由2个金属电极构成的1GΩ片上高阻标准件。组建能有效溯源至国家最高标准的定标装置,使用与标准件探针压点坐标匹配的探针卡作为测试夹具,考核出年稳定性优于0.1%的在片标准件。经试验表明:该标准件携带方便、性能稳定,对开展MEMS片上绝缘性能测试提供有效的现场校准方案,有效解决其溯源问题。

MEMS片上测试系统;绝缘性能;片上高阻标准件;标定

0 引 言

MEMS圆片测试环节位于MEMS生产线的设计和封装测试之间,能够有效剔除不合格芯片[1],避免其进入后期的封装和测试环节,可降低MEMS量产成本,提高器件可靠性。

MEMS片上绝缘性能测试主要针对电学中的绝缘电阻参数,是分析晶圆级封装的芯片内部管脚之间的隔离状态的重要手段,对正确判断产品工艺缺陷有着重要意义。目前,行业公认的绝缘电阻的典型判据为相对误差±10%。如果此参数测量不准,则会对前期工艺设计造成误判导致资金的浪费,甚至会造成器件过热出现短路烧毁器件的现象。

国内目前对MEMS片上绝缘性能测试是否准确问题,主要采取单台仪器校准的方法,这种溯源方式存在一定的弊端。主要原因是单台仪器的技术指标仅仅是整个系统的准确度的很小一部分,其他影响量如探针台系统、矩阵开关、线缆泄漏电流、光照、外界电磁干扰等才是影响晶圆级准确测量的重要因素,也就是说溯源工作并未至客户所使用的探针端面。此外,国内各计量机构尚无满足校准要求的在片标准件。国际上,采用美国国家标准技术研究院[2-3]提出的标准物质(RM8096和RM8097)完成MEMS圆片测试系统的验证。但是,这种标准物质并未针对单个参数,而是针对MEMS产品的终测环节,因此也无法将标准物质应用于此类系统的校准。

在分析国内外研究现状的基础之上[4],本文提出一种通过研制片上高值电阻标准件的方案解决目前行业内此类仪器的校准问题。这种标准件有2个优势:1)可在 4in 或 6in(1in=0.025m)圆片上制作,从形式上属于在片范畴,可以满足MEMS圆片测试系统的测试形式,能够校准到探针端面;2)采用不同于半导体行业常用的方块电阻制作工艺,本文采用了“制作基于GaAs高绝缘衬底的金属电极”的方案研制阻值高达1GΩ的标准电阻,以覆盖行业内对片上绝缘性能测试相对误差±10%的量值需求。

1 方案设计

目前,半导体行业内多采用方块电阻(典型值50~100 Ω/块)的制备工艺来制作在片电阻,其阻值范围一般覆盖1 Ω~10 MΩ。若采用此种技术,在4~6in晶圆片的有限区域内,根本无法研制吉欧姆量级的在片电阻,亦无法满足MEMS晶圆片绝缘特性的测试要求。

1.1 总体方案

本文选用“制作基于GaAs高绝缘衬底的金属电极”的方案,利用GaAs衬底的高绝缘特性,将两金属电极间的电阻(体电阻和表面电阻合成)定义为目标电阻值,从而实现片上高阻标准件的研制。

在方案设计中,衬底材料的选择是关键所在,必须选择具有高绝缘特性的衬底材料。陶瓷和GaAs是半导体行业中常用的绝缘衬底材料,具有较高的电阻率,其中陶瓷材料可以达到1010~1014Ω·cm,GaAs材料可以达到107~108Ω·cm。但是,陶瓷衬底相比GaAs而言,表面粗糙度较大,且加工工艺不如GaAs成熟,因此选用半导体工艺[5]中的离子注入工艺,对单晶GaAs材料表面全部区域进行掺杂。离子注入的过程首先是产生杂质离子(如硼),将这些离子加速到5 keV~1 MeV的高能状态,接着把离子注入到GaAs内,最后进行退火以消除晶格损伤并激活掺杂杂质。因此选用GaAs作为标准件的衬底材料[6],采用离子注入工艺,注入一定浓度的硼离子,破坏原有晶格结构,增强绝缘强度,减少泄漏电流,提高稳定性。

在电极尺寸制作方面,不同的金属电极尺寸对应着不同的电阻值,本文选用的方案是:固定衬底的电阻率和金属电极的间距,通过改变金属电极尺寸的方式来控制阻值,从而得到1GΩ电阻对应的电极尺寸,完成标准件的制作。

1.2 版图设计

根据1.1中的方案,利用L-Edit工具设计了如图1所示版图。其中,灰色部分为探针压点(pad),粉红色部分设计为一系列等高变宽的金属电极,深蓝色部分为划片道,白色部分为注入硼离子后的GaAs高绝缘衬底。

图1 高值电阻标准件版图设计

以电极宽度10μm为例将其放大,如图2所示。Pad 尺寸为 100 μm×100 μm(超过 100 μm 后,与宽度d一致);高度h为200 μm保持不变;间距Δ为4 μm保持不变;宽度d在10~400μm分布。这样制作的目的一方面是为了保持垂直方向上尺寸的一致性,便于探卡对其进行筛选;另一方面只有电极尺寸在微米量级做一系列的变化,才能获得最贴近阻值1GΩ对应的电极尺寸范围。总之,按照上述版图设计理念,当衬底材料绝缘性能足够高且足够稳定时,两个金属电极之间的电阻即为标准样片的电阻值[7]。

2 工艺制作

2.1 工艺流程

半导体工艺加工的流程如图3所示。

图2 等高电极版图放大(电极宽度=10μm)

图3 工艺流程图

首先对4in单晶GaAs衬底进行清洗和烘干;离子注入是一个物理过程,掺杂的硼原子被离化、分离、加速形成离子束流,扫过晶圆,该环节根据所需要达到的绝缘强度要求对GaAs衬底大面积注入硼离子[8];在离子注入后的衬底表面淀积一层氮化硅,因为Si3N4比较硬,具有较高的绝缘强度和抗氧化能力,可以较好地保护硼离子注入层避免划伤,同时也是一种较好的湿气和钠的阻挡层,以提高整体的稳定性;通过光刻工艺将所需图形(金属电极)显现出来;通过蒸发工艺将金属Ag刻在所需的图形上面;通过剥离的手段将晶圆片上不需要的结构(如光刻胶)去除;最后在整个结构表面进行一层Si3N4的钝化,以保证整个器件免受外界环境(如温度、湿度、强氧化等)的影响。

2.2 标准件实物

按照图3的工艺流程和图1的设计理念,进行了制版(负胶),然后在4in GaAs衬底上进行了1GΩ标准样片流片。通过PCM自动测试系统对其进行了初步实验:1V电压下,加电2h,泄漏电流为1.016nA,稳定性优于0.1%。

因为标准件在圆片上是以cell单元的形式进行分布的,一个cell对应图1的一个版。那么在考核的过程中,不同的cell单元上都存在1只ISOTM-10芯片,如何区分不同cell单元中相同的芯片为后期的考核带来困扰。在制版阶段是无法解决此问题的,因为一旦cell单元进行了分布便无从辨认,为了对每个cell单元进行区分,本文通过对标准样片制作1∶1的接触版,以列号/行号的方式标记每一个cell单元。如图4所示,某一cell单元的标记为C10R31,表示此单元位于圆片的第10列/第31行的位置。

图4 标准件的唯一性标记

3 考核标定

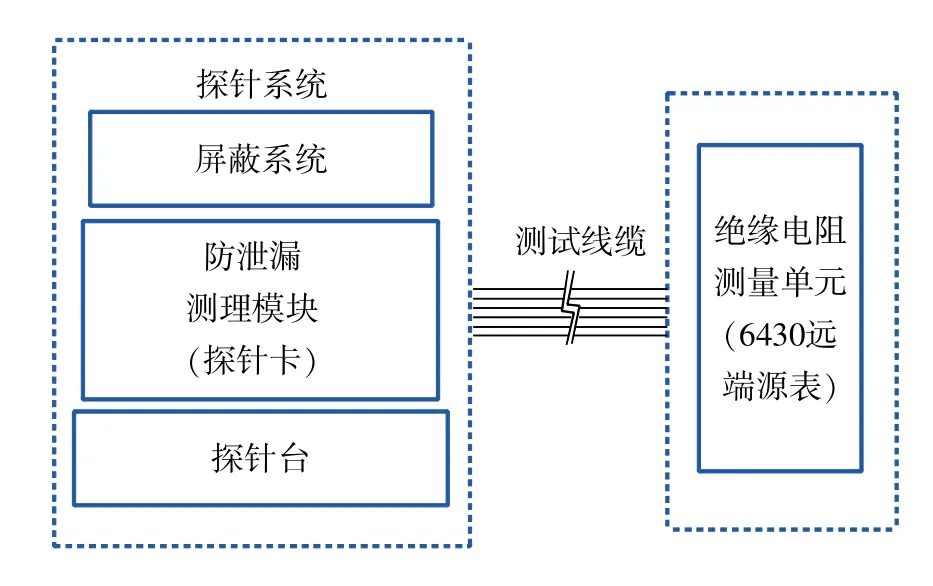

为了对所研制的片上高值电阻标准件标定,需要建立定标装置,其组成如图5所示。

图5 定标装置

本文采用的标准仪器为Keithley6430远端源表,工作模式为FVMI(加压测流)[9],即在被测件两端施加1V电压,通过测量流经两点间的泄漏电流从而计算得到电阻值[10]。探针台为直流探针台,屏蔽系统是最外围的屏蔽箱,防泄漏模块为高阻抗具有防泄漏功能的探针卡,探针卡的Pad结构是根据标准件的电极尺寸制作的。组建的定标装置可溯源至中国计量院高值电阻标准,定标装置的测量不确定度优于0.1%[11-12]。

对整个4in圆片进行了数据考核,以±20%作为判据,初步考核的数据如表1所示,从数据可见,当电极宽度在24~45μm之间时,合格的几率最大。

表1 1GΩ标准样片考核数据

表2 标准样片C08R18考核数据

对标准样片中编号为C08R18(电极宽度26μm)的样片进行了重复性和年稳定性筛选考核,测试数据如表2所示。

按照MEMS晶圆片测试系统对产品相对误差±10%的要求,标准件需要满足1%的技术指标。从表中考核结果可见,标准样片的短期测量重复性优于0.02%,年稳定性优于0.1%,均优于技术指标1%的1/10,因此满足作为标准件的要求。

4 结束语

通过研制出的1GΩ标准件使用情况表明,本文所设计的片上高阻标准件的研究方案可行,所组建的定标装置能够满足标准件的考核要求,可以作为便携式标准件对MEMS片上绝缘性能开展校准工作,从而解决系统的隔离特性的校准难题。

此外,应用本文提及的研制方案同样可扩展至0.1GΩ和10GΩ标准样片的制作,未来可将标准样片划片后选择3个阻值制作在一个载体上,作为一套标准件使用。亦满足其他0.1~10 GΩ高值电阻在片形式的测量系统(如:半导体PCM测试系统、AW-SEP310、RI-EG PCM自动测试系统等)的绝缘特性校准需求。

[1]ESCHENBURG A,HABIB T.通过晶圆片检测MEMS器件[J].电子工业专用设备,2010(2):14-16.

[2]MARSHALL J C,VERNIER P T.Electro-physical technique for post-fabrication measurements of CMOS process layer thicknesses[J].Journal of Research of the National Institute of Standards and Technology,2007,112(5):223-256.

[3]MARSHALL J C.New optomechanical technique for measuring layer thickness in MEMS processes[J].Journal of Microelectromechanical Systems March,2001,10(1):153-157.

[4]乔玉娥,刘岩,程晓辉,等.MEMS晶圆级测试系统现状及未来展望[J].传感器与微系统,2016,35(10):1-3,7.

[5]皮埃罗.半导体器件基础-国外电子与通信教材系列[M].黄如,王漪,王金延,等译.北京:电子工业出版社,2004:11-17.

[6]于信明,崔玉兴.GaAs工艺监测研究[J].半导体技术,2011,36(7):520-523.

[7]俸永格,刘文进.绝缘材料高阻测量方法初探[J].海南大学学报(自然科学版),2003,21(3):234-237.

[8]ZANT P V.芯片制作[M].韩郑生,译.6版.北京:电子工业出版社,2005:23-33.

[9]赵振业,段光安.微弱电流及V/I法高阻测量[J].测量与测试,2001(3):6-7.

[10]张秀勇,龚向曙,王海燕,等.高阻测量技术方法研究[C]∥2012国防计量与测试学术交流会,2012:523-525.

[11]乔玉娥,范雅洁,杜蕾,等.MEMS晶圆片测试系统绝缘电阻参数校准技术研究[C]∥2015国防计量与测试学术交流会,2015:29-32.

[12]BEILEY M, LEUNG J, WONG S S.A micromachined array probe card-fabrication process[J].IEEE Trans on Components Packaging and Manufacturing Technologypart B,1995,18(1):179-183.

(编辑:李妮)

Development of high resistance standard for the MEMS on-wafer insulation test

QIAO Yu'e, LIU Yan, DING Chen, ZHAI Yuwei, LIANG Faguo, ZHENG Shiqi

(The 13th Research Institute of China Electronics Technology Group Corporation,Shijiazhuang 050051,China)

In order to solve the accurate measurement problem of isolation test about MEMS wafer test system, prepared a plan of manufacturing on-wafer high resistance standard parts and developed a kind of 1GΩ on-wafer high resistance standard parts that were composed of 2 metal poles based on GaAs substrate according to the high insulation properties of GaAs semiconductor materials after boron ions were injected,and also developed a calibrated equipment that can effectively trace back to the highest national standard.By using the probe card matched with pad coordinates of standard parts,assessed the wafer standard parts with annual stability superior to 0.1%.The test indicates that the standard part is portable with stable performance, which provides effective field calibration plan and can effectively solve the source tracing problem.

MEMS on-wafer test system; insulation performance; on-wafer high resistance standard;evaluation

A

:1674-5124(2017)07-0088-04

10.11857/j.issn.1674-5124.2017.07.017

2016-11-29;

:2016-12-12

乔玉娥(1980-),女,河北石家庄市人,高级工程师,硕士,研究方向为电磁仪器计量技术研究。