FPGA功能验证自动化技术研究与实践

2017-08-07朱伟杰费亚男

朱伟杰 阳 徽 费亚男 李 洋 王 昶

北京航天自动控制研究所,北京100854

FPGA功能验证自动化技术研究与实践

朱伟杰 阳 徽 费亚男 李 洋 王 昶

北京航天自动控制研究所,北京100854

深入分析了影响FPGA功能验证效率和质量的各项因素,改进了传统FPGA软件验证平台的搭建方法,阐述了FPGA软件自动化验证平台搭建技术、基于Perl语言的Testbench自动生成技术、受约束的随机激励生成技术、接口时序自动侦错技术、SVA断言以及基于VBA宏的管脚配置自动检查技术等6种改进策略。这些自动化技术将功能验证中程式化和标准化的工作交由工具完成,提高了验证平台搭建和仿真结果检查的效率。 关键词 功能验证;自动侦错;自动化验证平台;受约束的随机激励

以FPGA和CPLD为代表的可编程逻辑器件由于具有并行的计算结构且开发周期短、功能可自行定制的明显优势,已被大量应用于航天型号的产品设计之中。随着航天发射任务的不断增长,型号研制中FPGA设计的数量呈暴发式增长,FPGA软件测试任务量逐年攀升,测试时间不断压缩,为了保证航天型号发射和实验任务的顺利开展,需要具备在短时间内完成对复杂FPGA设计进行充分、全面验证的能力。据统计,商业化IC设计流程中功能验证大约占用整个周期的50%~70%,芯片失效的原因中74%的故障与逻辑功能错误有关。因此,如何利用新的验证技术提升功能验证的效率和质量成为整个业界共同关心的问题。

本文根据多年FPGA软件测试经验,总结了6点提高了FPGA软件测试自动化程度的改进技术,这些自动化技术辅助测试人员快速搭建验证平台,实现了部分测试结果的自动比对,利用高级语言实现程式化和标准化工作的自动执行,最大化提高验证效率和验证质量。

1 FPGA功能验证自动化技术实现方案

1.1 FPGA软件全生命周期验证流程

验证贯穿于整个FPGA设计流程,从需求分析到最终固件的每个阶段都需要验证[1]。如图1所示,FPGA验证类型分为静态验证和动态验证,其中静态验证包括文档审查、代码审查、跨时钟域检查、静态时序分析和逻辑等效性检查;动态验证包括功能仿真、时序仿真和板级验证。这些验证类型实现了FPGA软件的全生命周期覆盖。静态验证一般由测试工具自动完成,人工分析结果,耗时较少;功能仿真、时序仿真需要人工搭建测试平台,编写测试用例,分析仿真结果,耗时占整个验证周期的70%~80%。因此,要提高FPGA软件验证效率,必须对功能验证进行优化和改进。

1.2 功能验证自动化技术总体方案

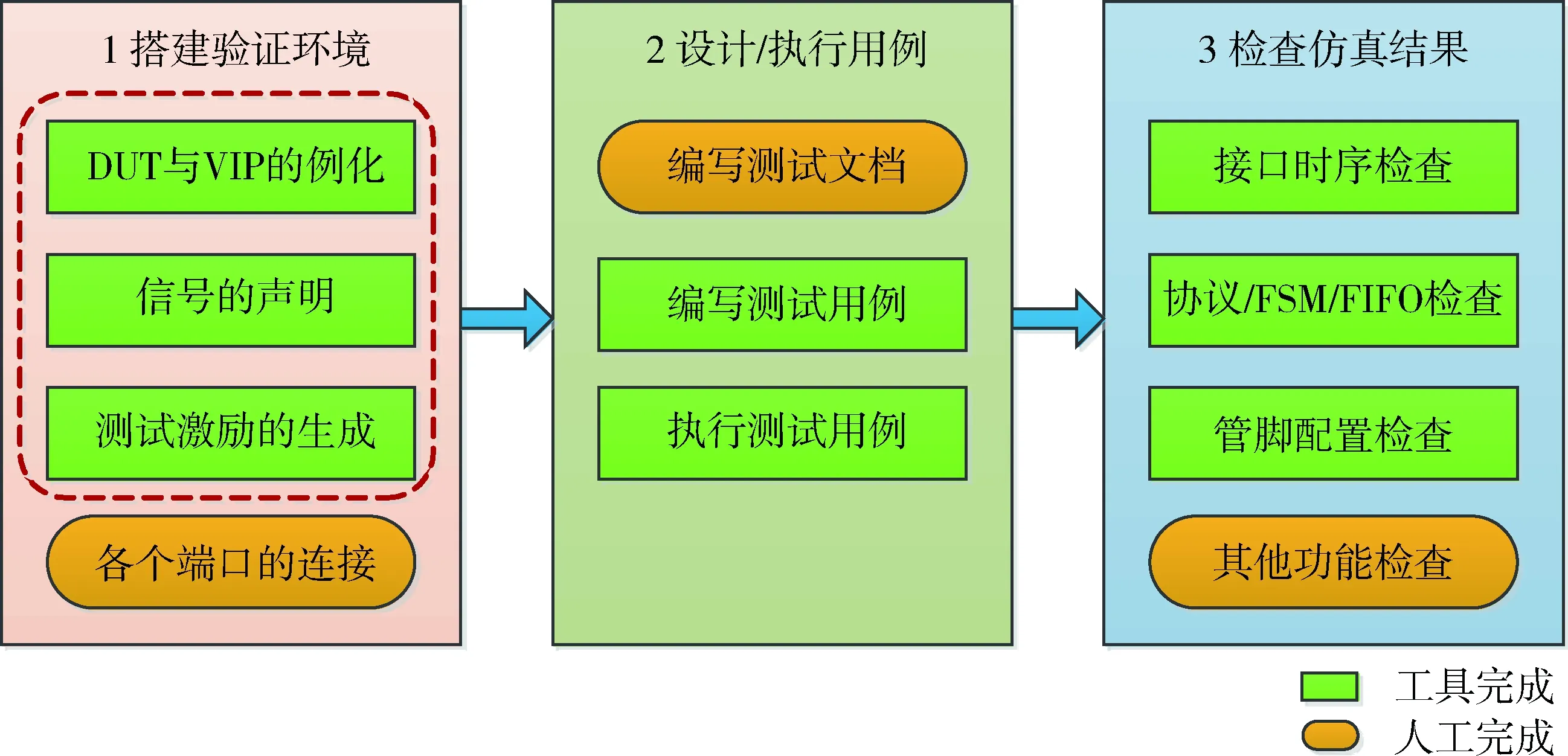

FPGA功能验证主要分为3个步骤,依次为搭建验证环境、设计和执行测试用例、检查仿真结果,如图1所示,其中部分程式化工作,如Testbench搭建、测试用例自动生成及部分仿真结果的检查可由工具或脚本来完成。

图1 功能验证的任务分解

本文开发了基于Makefile的验证平台自动搭建脚本和基于Perl语言的Testbench自动生成脚本,实现了FPGA软件测试环境的自动搭建。受约束的随机激励生成技术用来实现测试激励的自动生成; specify block用来实现接口时序的自动检查;SVA用来实现功能、协议和状态机的自动检查;VBA宏用来实现管脚配置的自动检查,这些技术将验证过程中程式化的工作交由计算机完成,提高了功能验证平台的搭建效率和仿真结果的侦错效率。

2 FPGA软件测试自动化技术

2.1 基于Makefile的自动化验证平台设计

验证环境是指对设计进行验证时为了便于使用、管理和协同工作而设计的一个环境,启动验证所需要的一系列工具,可对设计的仿真结果进行分析和整理,利用系统脚本,实现整个验证流程的自动化,具有灵活、可重用和可配置性的特点[2]。构建自动化验证环境,利用脚本组织与管理验证数据,自动呈现验证结果,能够避免大量人工重复劳动,提高验证效率。

2.1.1 验证数据的组织与管理

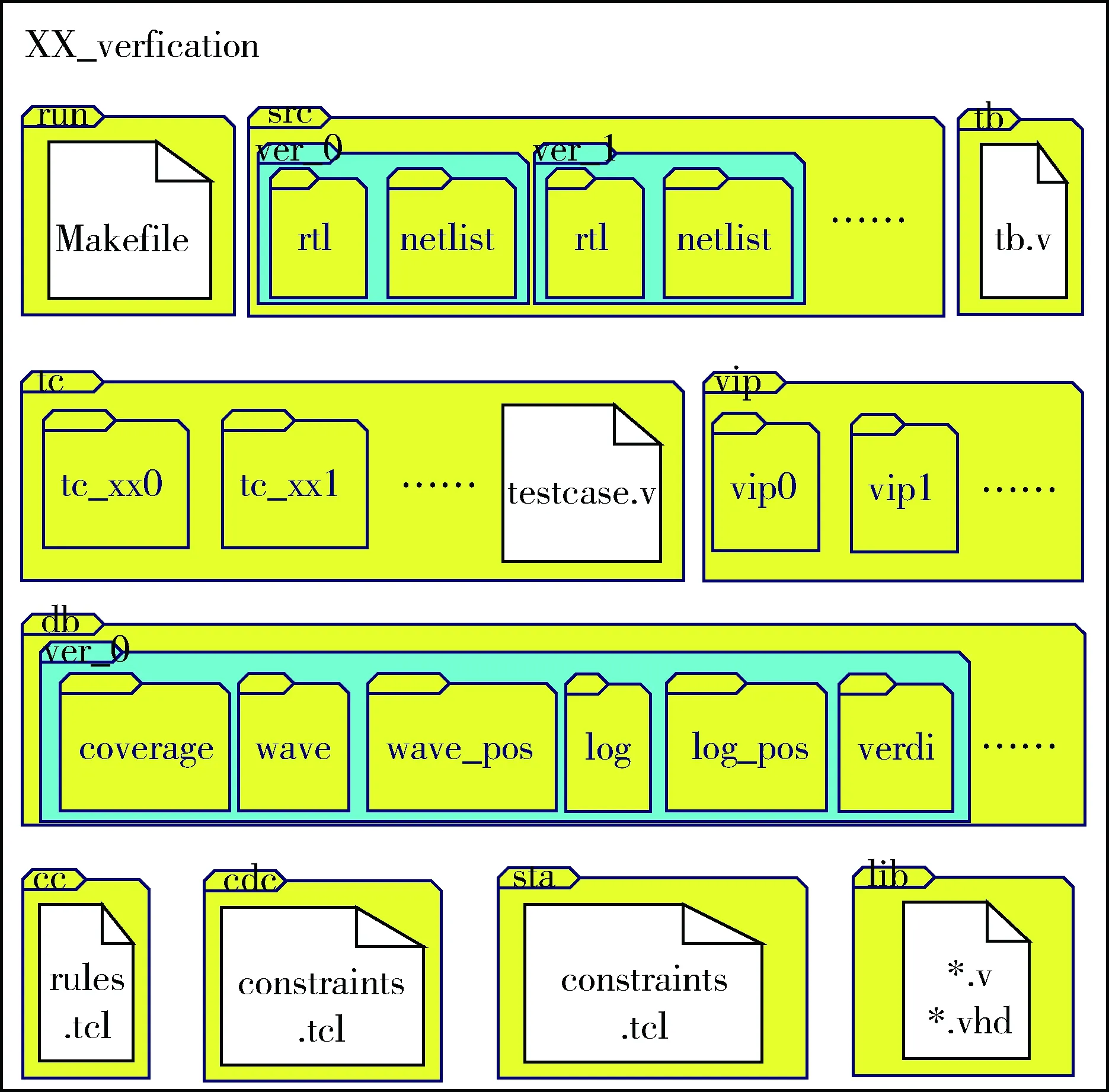

高效的数据组织和管理方法能提高验证平台的自动化程度。自动化验证平台需完成FPGA代码规则检查、功能仿真、时序仿真、跨时钟域分析、覆盖率统计和静态时序分析等6种类型的测试。其架构如图2所示,各个目录的功能介绍如下。

图2 基于Makefile的自动化验证平台架构

1) run:通用测试平台目录,包含Makefile脚本、编译库和仿真运行的临时文件;

2) src:源文件目录按版本编号细分子目录,每个版本编号目录包括rtl源文件(功能仿真),netlist网表文件以及sdf标准时延文件(时序仿真);

3) tb:仿真平台文件目录,包含测试方编写的仿真测试平台tb.sv、配置文件等;

4) tc:测试用例目录,包含功能、时序仿真所有的测试用例集;

5) vip:验证模型库文件目录,包含功能、时序仿真时用到的标准模型;

6) db:数据库目录,包含功能仿真和时序仿真中生成的各种数据:覆盖率数据、仿真波形数据和仿真日志数据等;

7) cc:代码规则检查,包含检查规则文件、运行脚本和运行中间结果;

8) cdc:跨时钟域检查,包含设计TCL约束文件、运行脚本和运行中间结果;

9) sta:静态时序分析,包括静态时序设计约束、运行脚本和运行中间结果;

10) lib:芯片库文件目录,包含器件芯片提供的库文件。

2.1.2 基于Makefile的脚本设计

系统脚本是整个验证环境的关键所在,也是形成自动化验证环境的基础。使用脚本搭建验证环境能提高验证的自动化程度,减少人工重复劳动。Makefile脚本功能描述如下:

1)创建验证目录;按图2的架构生成各级目录,将初始化文件(例如Questasim的*.ini和VCS的*.setup文件)拷贝到相应子目录下;

2)设置仿真参数:指定被测件顶层名称、器件类型及版本号、仿真工具、工况类型和仿真类型等配置信息,仿真时将根据配置信息搜索文件及仿真库;

3)仿真:包括功能仿真和时序仿真,根据仿真参数对FPGA标准库文件LIB、外围器件模型VIP、被测件的源文件或者网表文件DUT、测试平台TB以及测试用例TC进行编译,并将所有程序的编译结果存放在run目录下的编译日志文件中,便于编译不通过时查找错误,仿真结果保存为fsdb文件;

4)调试:本文使用Verdi工具进行调试,Verdi根据配置信息编译源文件、显示RTL代码、原理图和fsdb仿真波形文件;

5)数据库:平台自动保存日志文件、波形文件和覆盖率信息,这些文件按照版本号和数据类型存放在对应子文件夹下;

6)覆盖率统计:合并各个测试用例的覆盖率,统计语句、分支等总覆盖率;

7)静态测试:根据配置信息、自定义规则集、约束文件等自动执行代码规则检查、跨时钟域检查和静态时序分析,由人工进一步分析结果。

基于Makefile脚本,测试人员在Linux终端输入简单命令即可实现验证的自动化执行,例如终端输入命令make vcs tc=tc_reset_001 debug=yes cov=yes即可调用VCS仿真工具执行测试用例tc_reset_001,仿真结束调用Verdi工具调试,统计覆盖率信息。自动化脚本代替复杂图形化界面操作能极大地提高验证效率,统一的目录架构易于理解和继承,便于测试团队协同开展测试。

2.2 基于Perl语言的Testbench自动生成技术

Perl被称为实用报表提取语言,特别适合批处理文本文件。由VHDL或Verilog语言编写的RTL代码有固定的格式和关键字,通过Perl脚本识别关键字来提取有用的信息,再将其打印输出生成符合System Verilog语法规范的Testbench。具体实现方法如下。

1)被测件的自动识别与例化

通过识别关键字entity和module来提取被测件的实际名称,识别关键字input/inout/output和in/inout/out来提取输入输出端口信息,删除无用字符后将端口名称存储至数组中,最后按System Verilog语法打印端口信息,实现被测件例化。

2)输入/输出端口的自动识别与声明

通过关键字input/inout和in/inout识别输入端口,并将其声明成wire/logic型变量;通过关键字output和out识别输出端口,并将其声明成reg/logic型变量。

3)部分激励的自动生成

自动将端口中含有clock/clk字符的端口识别为时钟信号,产生默认频率的时钟激励。同样地,将含有reset/rst字符的端口识别为复位信号并复位激励,再由人工根据软件任务书进行适应性修改。

4)测试平台的版本控制

Perl脚本自动检测计算机本地时间和Linux用户名,并添加到Testbench文件头的注释中,从而实现Testbench版本的自动控制。

图3 测试平台自动生成的过程

基于Perl语言的验证平台生成过程如图3所示,在Linux终端中输入的命令格式为:perl tb_gen.pl dut.v vip1.v vipn.v,其中tb_gen.pl为Perl脚本。Perl脚本会在几秒钟内自动生成测试平台和简单激励等,测试人员只需简单修改时钟周期和复位时间等参数即可使用。而传统的方法需要人工编程,容易引入低级语法错误且格式不统一,对于大规模软件能显著提升Testbench搭建效率。

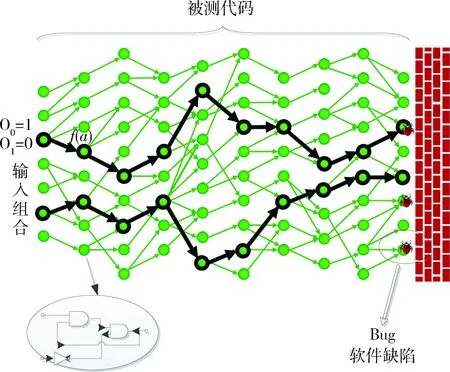

2.3 受约束的随机激励生成技术

传统的验证大多使用定向测试,即针对被测件的具体特性来编写测试向量,然后人工检查仿真结果是否与预期一致。受约束的随机激励将输入激励限定在一定范围,由代码自动产生,然后通过参考模型预测输出结果,实现结果的自动检测。如图4所示,小圆圈代表逻辑电路,只有满足特定的输入,通过特定的路径,才能发现软件缺陷。随着设计规模愈发庞大,验证空间将呈指数级增长,使用定向激励覆盖所有的功能变得越来越困难。

图4 软件缺陷寻找过程

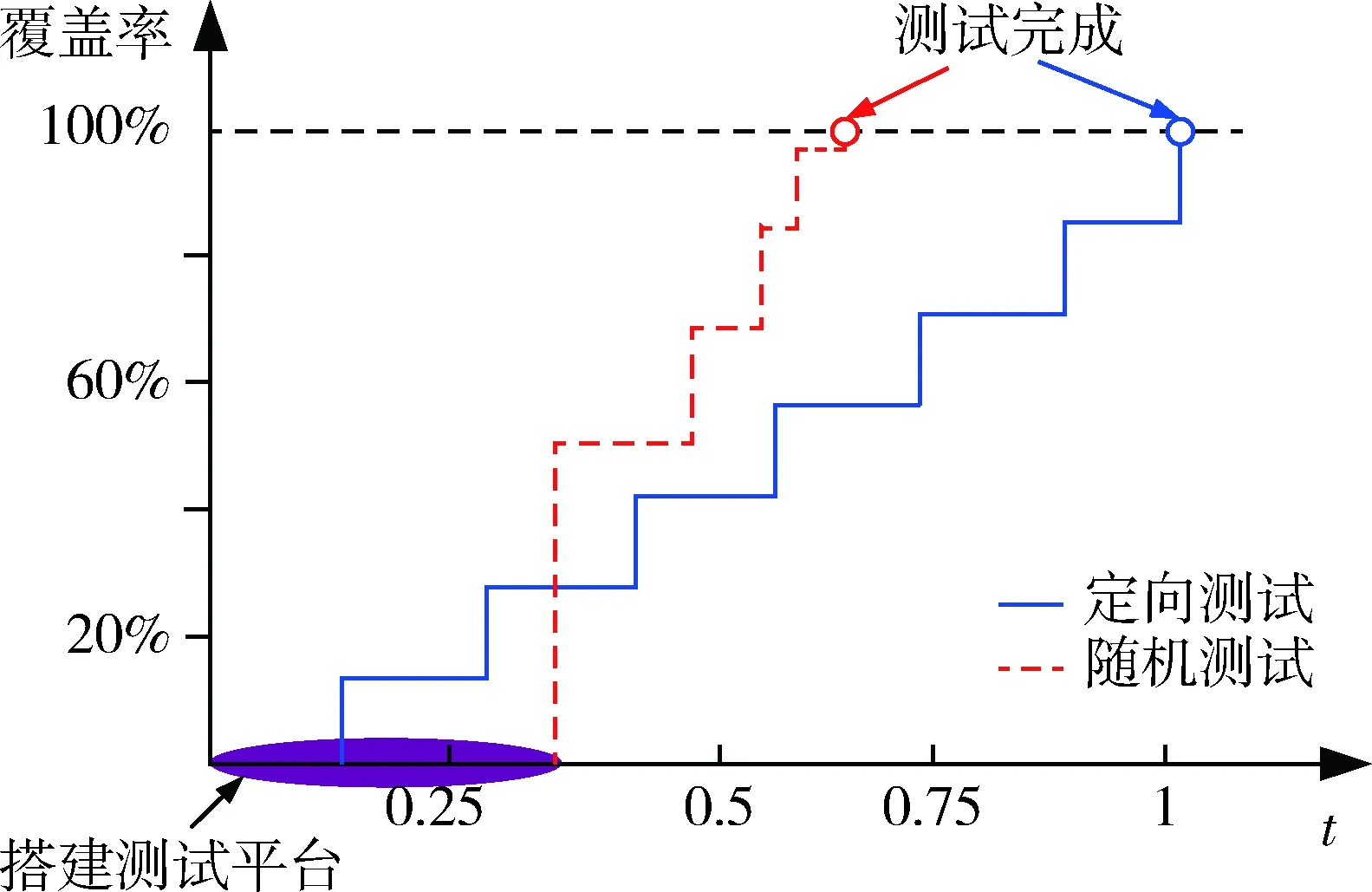

定向测试可以找出设计中预期的漏洞,而随机测试能找出预料不到的漏洞。建立分层随机激励测试平台所需的时间比定向测试平台多,尤其是自动检测部分,但其回报却很高。覆盖率是考核验证进度的重要指标,对于那些受约束的随机测试覆盖不到的地方,再补充定向测试,直至覆盖率达到100%。受约束的随机测试与定向测试的进度比较如图5所示。在验证较大规模设计时,受约束的随机测试效率更高。

图5 受约束的随机测试与定向测试的进度比较

在生成随机激励时,需要考虑随机粒度的划分和随机层次的划分[3]。随机粒度太细会导致随机激励空间爆炸,无法有效完成激励覆盖;随机粒度太粗则会导致构造粗粒度随机单元的人工工作量上升,随机自动化比例下降。采取分层的随机激励架构,每个层次面向某一抽象级别的功能激励,各层间相对独立并相互约束,可以对随机生成流程进行更有效的管理和扩展。因此,验证激励生成流程需要结合验证粒度和验证层次的划分,达到高效随机效果和良好的可控性。

System Verilog提供了丰富的约束方式和随机数函数[4],例如$dist_exponential()实现指数衰落,$dist_normal实现钟形分布等。Verilog语言使用$random函数也可以实现随机化,在模拟芯片接口时序时,使用$random函数让信号在Tmin~Tmax之间变化,例如#(Tmin + {$random}%(Tmax-Tmin));使用线性反馈移位寄存器(LFSR)产生伪随机数,保证数据有足够的跳变,例如data[7:0] = (data[6:0],!{data[3]^data[5] ^data[6]^data[7]})。

2.4 基于specify block的接口时序自动侦错技术

FPGA接口测试是指通过时序仿真验证不同工况下的接口时序性能是否满足协议值的要求。传统验证方法一般是在时序仿真完成后,由人工对照芯片数据手册检查接口信号的仿真波形,该方法对人工判读质量和仔细程度要求较高,当执行多次仿真(如3种工况下的时序仿真)时,人工检查接口时序会耗费较长时间,无法实现结果的自动化检查。Verilog和System Verilog语言提供了specify block指定块,从而实现时序检查,当发现时序违例会自动报错。specify block可以执行以下2类时序检查:

1)检查时序窗口的稳定性,使用$setup,$hold检查建立和保持时间,使用$recovery和$removal检查恢复和移除时间;

2)检查时钟和控制信号在指定事件之间的时间间隔,使用$skew检查限制最大偏斜,使用$width检查最小脉宽,使用$period检查最小周期,使用$nochange限制信号不发生变化等。

图6 根据芯片接口时序编写specify指定块

如图6所示,specify block指定块能在仿真过程中持续监视接口时序,一旦发现时序违例会自动报错,其执行步骤如下:

1)根据芯片接口时序编写specify指定块。以HY27UF081G2A芯片为例,根据地址锁存时序和时间参数编写specify block,示例中写信号WE低电平最小脉宽为15ns,在specify block中表述为$width(negedge iWE, 15);

2)执行功能仿真或时序仿真。如果接口时序满足芯片手册要求,则仿真工具不会提示任何信息;如果发生时序错误,仿真工具会报告错误发生的时刻和具体信息。

该技术使接口时序的自动侦错成为可能。一种常见的情景是测试人员在下班前编写好specify block时序检查语句,然后利用非工作时间在服务器上执行3种工况下的时序仿真,再次上班时查看仿真报告是否发生时序错误。而传统方式是执行完一次仿真,人工在波形窗口用标尺测量各个时间,检查无误后再执行下次仿真。对于大规模设计,传统的人工检查可能存在遗漏且耗时较长,specify block技术能将接口测试效率提升几个数量级。

2.5 基于SVA断言的FPGA软件功能验证自动侦错技术

传统的功能验证结果检查方法是等到仿真结束后,错误传递到输出端口,通过查看日志文件和分析仿真波形来查找缺陷,这消耗了验证人员大量的时间和精力。基于断言的验证是通过在RTL代码中插入断言语句,然后在动态仿真过程中由这些断言语句来判断实现的设计是否跟设计的规范相一致。

SVA (System Verilog Assertion)断言可以执行协议接口检查(如PCI,USB协议接口)、逻辑控制信号检查(如SDRAM控制信号)、有限状态机(FSM)和仲裁器等时序和功能检测,这些断言埋在FPGA设计中,仿真过程中断言不停地监视着设计的预期行为,一旦在某个插入点发现缺陷时就会打印出相关的缺陷报告,直接定位缺陷发生的位置。在FPGA软件RTL代码中可以断言的插入点包括:

1)接口协议检查

使用SVA断言对标准协议接口进行有效监控,例如借助断言检查内部寄存器配置,检查复位后相关信号的波形等。

2)有限状态机检查

使用断言检查状态机各状态间的转换是否正确,且不违背任何时序上的要求。一种可以借鉴的方法是先画出FSM状态转换矩阵,然后分析出各个状态禁止发生的跳转。

propertyp_forbid_l;@(posedgeclk)disableiff(!reset)((current_state[2:0]==`ACTIVE)||(current_state[2:0]==`HALT)||(current_state==`CPU)||(current_state==`READY))|->$past((current_state==`IDLE)==0);endpropertya_forbid_1:assertproperty(p_forbid_1),else$fatal;

属性p_forbid_1表示如果当前状态为ACTIVE,HALT,CPU或READY,那么FSM的前一个周期状态就不能是IDLE。

3)FIFO状态监视

检测FIFO的操作是否符合设计要求,FIFO的上溢和下溢,以及错误时中断申请信号的触发。例如,监视FIFO空信号和读信号,当FIFO已空,再读出就会报下溢错;监视FIFO满信号和写信号,如果FIFO已满,再写入会报上溢错。

4)逻辑输出信号断言

例如要验证属性:“当信号a 在某一个时钟周期为高电平时,那么在接下来的2~4个时钟周期内,信号b 应该为高电平”,其SVA代码为:

propertya2b_p;@(posedgesclk)$rose(a)|->[2:4]$rose(b);endpropertya2b_a:assertproperty(a2b_p);//生效a2b_c:coverproperty(a2b_p);//覆盖语句

5)脉冲宽度断言

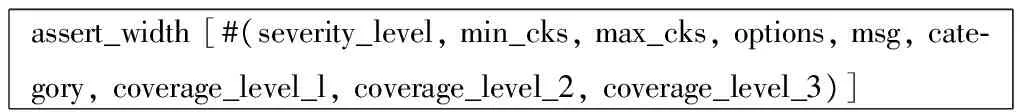

方法1:使用SVA直接对属性进行描述;方法2:使用SVA库中的assert_width模块,通过配置相关参数实现宽度断言:

assert_width[#(severity_level,min_cks,max_cks,options,msg,cate⁃gory,coverage_level_l,coverage_level_2,coverage_level_3)]

SVA可以监视设计模块的内部、模块与模块间连接信号的各种时序关系,与RTL代码综合,用于调试,也可以进行设计的功能覆盖。

2.6 基于VBA宏的FPGA管脚配置自动检查技术

传统的管脚配置检查方法是依据软件需求分析的管脚定义人工逐项核对FPGA工程文件中管脚配置,大规模FPGA设计使用的管脚可能达到几百个

且杂乱无章地排列,通过人工逐个检查的效率低下,且可能存在漏判的情况。Excel具有快捷方便的数据输入和强大的数据处理能力,它提供的VBA(Visual Basic for Application)宏语言可以方便地开发出用户需要的功能。

本文开发的“管脚配置检查宏”能自动比较Excel表格中来自软件需求分析和FPGA工程中的信号名和管脚号,其原理如图7所示,测试人员首先将软件需求分析中的管脚配置信息复制到Excel表格A/B列,然后将FPGA工程中的管脚配置报告复制到C/D列,最后点击“检查FPGA管脚配置”执行检查。宏将依次从A列和C列中寻找匹配的端口名称(如A列4行和C列9行的端口localclk),再比较B列和D列对应行的FPGA管脚(B列4行的管脚名称A9和D列9行的管脚名称C9),如果二者一致,则报告检查通过;如果不一致,则报告错误。该技术可以在几秒内完成上百个管脚配置的检查,显著提升检查效率。

图7 使用Excel执行管脚配置检查

3 应用效果

为统计FPGA软件的验证效率,本文引入式(1)的效率计算公式计算千行代码消耗的人时数。例如,某测试组10人一年测试了12万行代码,按一年工作280天,每天工作10小时,其中70%的时间用于测试,测试效率为163人·小时/千行。

=163人*小时/千行

(1)为验证本文总结的6项改进措施的实际效果,将测试团队分为采用传统验证手段和采用自动化验证技术2个组,计算在一段时间内(3个月)2个组的验证效率。经测算,改进前平均千行代码耗时176人·小时,改进后平均千行代码耗时144人·小时,效率提升了18.2%。实践表明,本文介绍的FPGA软件自动化验证平台、基于Perl语言的Testbench自动生成技术、受约束的随机激励生成技术、接口时序自动侦错技术、SVA断言以及基于VBA宏的管脚配置自动检查技术等6种改进策略,能充分利用各类语言的优势提升FPGA软件验证的自动化程度,从而降低测试成本,保证测试充分性。

4 总结

深入分析了FPGA软件全生命周期验证流程,阐述了提高了FPGA软件测试平台搭建和自动化侦错的6点改进技术,这些自动化技术一方面辅助测试人员快速搭建验证平台,另一方面实现了部分测试结果的自动比对,将功能验证中程式化和标准化的工作交由工具完成,从而实现FPGA软件批量化和自动化测试,减轻了测试人员的工作量,将测试人员的精力更多地放在测试用例设计环节,最大化提高验证效率和质量。

[1] 王石. 基于FPGA芯片的功能仿真平台构建及静态时序分析[D]. 西安:西安电子科技大学,2008. (Wang Shi.Construction of Function Simulation Platform and Static Timing Analysis Based on FPGA Chips [D]. Xian: Xidian University, 2008.)

[2] 费亚男,周辉,朱伟杰. FPGA软件自动验证平台设计与实践[J]. 计算机测量与控制,2016,24(5):139-142.(Fei Yanan, Zhou Hui, Zhu Weijie. Auto Verify Platform Design and Practice for FPGA Software [J]. Computer Measurement and Control, 2016,24(5):139-142.)

[3] 殷燎.面向SoC的IP核及嵌入式处理器功能验证方法研究[D]. 杭州:浙江大学博士论文,2010.(Yin Liao. Research on IP Core and Embedded Processor Function Verification Method Based on SoC [D]. Hangzhou: Zhejiang University, 2010.)

[4] Chris Spear.张春,麦宋平,赵益新,译. System Verilog验证测试平台编写指南[M].北京:科学出版社,2009.

Research and Practice of Automation Technology on FPGA Function Verification

Zhu Weijie, Yang Hui, Fei Yanan, Li Yang, Wang Chang

Beijing Aerospace Automatic Control Institute, Beijing 100854, China

Inthispaper,thefactorsthataffecttheefficiencyandqualityofFPGAfunctionverificationareanalyzeddeeply,thetraditionalmethodofbuildingtheFPGAverificationplatformisimproved,andsiximprovementstrategiessuchastheautomatictechnologyofbuildingverificationplatform,theTestbenchgenerationmethodbasedonthePerllanguage,thegenerationtechnologyoftheconstrainedrandomteststimulus,theerrordetectingtechnologyoftheinterfacetimingsequence,thesystemVerilogassertionandtheautomaticinspectionofpinconfigurationareintroduced.Byusingtheseautomatictechnologies,theprogramandstandardizedworkinthefunctionverificationarecompletedbythecomputer,andtheefficiencyofbuildingtheverificationplatformandcheckingthesimulationresultsisimproved.

Functionverification;Errordetecting;Automaticverificationplatform;Constrainedrandomteststimulus

2016-12-16

朱伟杰 (1987-),男,山东威海人,硕士研究生,工程师,主要研究方向为FPGA软件设计与测试;阳 徽(1985-),男,湖南邵阳人,硕士研究生,高级工程师,主要研究方向为FPGA软件设计与测试;费亚男 (1988-),女,长春人,硕士研究生,工程师,主要研究方向为FPGA软件测试;李 洋(1989-),男,哈尔滨人,硕士研究生,工程师,主要研究方向FPGA软件设计与测试;王 昶(1989-),男,黑龙江双城人,硕士研究生,工程师,主要研究方向为FPGA软件设计与测试。

TP316.2

A

1006-3242(2017)02-0072-06