一种数字T/R组件同步设计

2017-08-02荆州南湖机械股份有限公司

荆州南湖机械股份有限公司 张 弛

一种数字T/R组件同步设计

荆州南湖机械股份有限公司 张 弛

数字T/R组件是数字化雷达的重要组成部分,其性能直接影响到整个雷达系统的探测精度。如果阵列数字T/R组件之间不能够稳定同步,将直接导致数字波束合成的无效,因此,数字T/R组件的同步,是数字化T/R组件首先要解决的问题。本文结合一种数字T/R组件的具体设计,介绍了其同步设计技术。

数字T/R组件;数字波束合成;同步技术

引言

数字T/R组件主要运用在有源相控阵雷达中,每个天线辐射单元都装配有一个收发组件, 每一个组件都能自己产生、接收信号。因此在频带宽度、信号处理和冗余度设计上都比无源相控阵雷达具有更大的优势,且幅度、相位都由数字电路控制。而数字电路的同步并不像模拟电路那样固定和线性,多级数字电路的组合更加增加了信号相位翻转的不确定性。一般的有源相控阵雷达为发挥更大的探测威力,往往采用数字相控阵,虽然数字相控阵可设计在线的幅相校正通道,但如果数字阵上数量庞大的发射源信号的产生不能达到同步,接收信号的幅相校正结果也失去了意义。因此,数字T/R组件的同步,是相控阵雷达系统首先需要解决的问题。

1.同步系统组成

同步系统需要数字T/R组件与频综设备联合工作完成,频综设备接收雷达主控控制指令,产生全机同步信号、同步时钟,经过时钟与同步分配网络输出到每个数字T/R组件。数字T/R组件接收同步信号、同步时钟和雷达主控发送的控制指令,完成同步信号和时钟的调整,根据控制指令生成中频数字信号。

2.同步系统设计思想

通过调整同步时钟与同步信号之间的相对相位关系,将同步信号前沿控制在同步时钟的单个周期内,从而保证数字阵接收的同步信号的一致性。

通过同步时钟生成数字T/R组件内部工作时钟,并产生控制DDS的控制信号,将DDS设置为从芯片,通过控制信号的时序控制保证多个分布式DDS的同步。

达到上述两个条件后,分布式数字T/R组件之间的各个发射、接收通道相对相位关系将保持固定,选取基准通道/信号,使用幅相技术校正,即可得到相位关系相对一致的数字收发信号。

3.同步信号与同步时钟处理

3.1 同步时钟与同步信号的监测

在数字T/R组件内部实时对同步时钟与载频同步信号的相位关系进行监测,在FPGA内部产生800M时钟,分别对当前使用的同步时钟与载频同步信号进行计数采样,通过计数的采样结果,得到同步时钟上沿与载频同步信号上沿的相对位置关系,如果大于同步时钟的1/4周期时间,则为安全稳定区域,不需要做出调整;否则为临界区域,容易产生撞沿,导致解码后同步信号有一个周期的抖动,需要调整载频同步信号的上沿位置,直到满足要求。

3.2 同步信号的调整

载频同步信号的相位关系调整只能滞后不能提前,考虑到数字器件的特性,采用D触发器延时的方式,改变载频同步信号的相对相位关系。由于同步时钟与载频同步信号的载频部分信号约为十倍频率关系,因此使用与载频部分相当的频率来完成触发操作,分为四个调整区间,每个区间约90°,每次触发次数为两次。完成单个区间的相位调整后,判断一次相对相位关系,直到满足要求。

4.DDS控制时序处理

本文所介绍的同步设计方案基于ADI公司的AD9959芯片设计。

在时钟状态匹配且状态转换同步的条件下,DDS可实现同步。同步原理是在系统时钟相参的情况下,对多个DDS器件进行异步编程,通过对所有器件同时进行I/O更新来激活编程内容,达到同步效果。因此,AD9959的同步分为两个部分:

(1)系统时钟同步

AD9959的同步逻辑包括同步发生器和同步接收器,两部分均使用本地SYSCLK信号作为内部定时。REFCLK为外部参考时钟,决定SYSCLK信号源,SYNC_CLK_IN为外部同步时钟,决定SYSCLK时钟沿。当SYNC_CLK时钟与SYNC_CLK_IN时钟相位同步时,该片AD9959与外部同步时钟SYNC_CLK_IN达到同步状态,所有AD9959 SYNC_CLK时钟均与SYNC_CLK_IN同步时,各AD9959之间也达到同步,即达到分布式AD9959同步。然而多个AD9959各自所寄生的数字T/R组件安装位置不同,功分网络也有差异,上电时间也并不一致,因此仅依靠硬件的输入只能保证系统时钟的相参,相位的相对固定,并不能保证通道间相位差值,因此,还需要软件刷新寄存器,通过调整系统时钟相位,达到同步的目的。

(2)指令控制同步

AD9959上电后,可通过指令调整初始相位,达到各通道的相位同步,要保证信号捷变的同步,就必须保证所有AD9959对同一个寄存器参数同时生效。

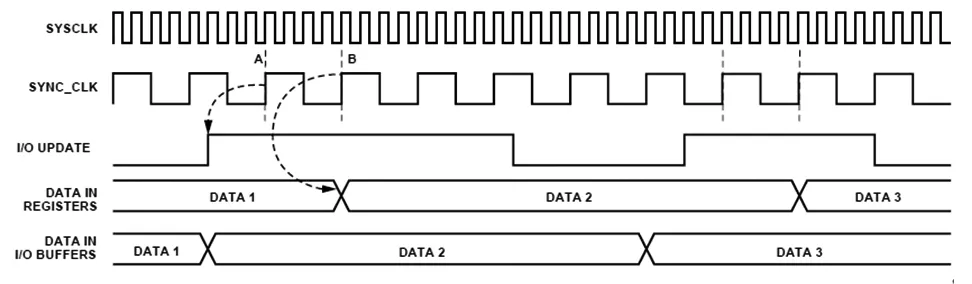

I/O_UPDATE引脚用于将串行I/O缓冲器中的数据传输到器件有效寄存器中,SYNC_CLK属于上升沿有效信号,由四分频电路对系统时钟分频后获得。I/O_UPDATE用于启动缓冲器数据转移,可以与SYNC_ CLK同步或异步。如果满足信号建的建立时间要求,则DAC输出可以获得恒定的延迟,缓冲器数据向有效寄存器传输的情况如图1所示。

图1 I/O_U P D A T E与时钟相对关系

5.结束语

数字信号的使用使数字T/R组件具备高频率分辨率、高频率切换速度、超宽的频率范围,并能实现各种调制波和任意波形。而同步技术的支持能保证频率切换时相位保持连续,单通道周期间初始相位一致,通道间初始相位一致,结合幅相校正技术,能够精准保证到每个通道每个周期的相位的稳定与连续。

[1]吴曼青.基于DDS的收发全DBF相控阵技术[J].高技术通信,2000, 10(8):42-44.

[2]吴曼青,靳学明,谭剑美.相控阵雷达数字T/R组件研究[J].现代雷达,2001,23(2):57-60.

[3]吴曼青,王炎,靳学明.收发全数字波束形成相控阵雷达关键技术研究[J].系统工程与电子技术,2001,23(4):45-47.