集成电路制造工艺技术现状与发展趋势

2017-07-31周哲付丙磊王栋颜秀文高德平王志越

周哲,付丙磊,王栋,2,颜秀文,高德平,王志越

(1.中电科电子装备集团有限公司,北京100070;2.中国电子科技集团公司第四十八所,湖南长沙410111)

集成电路制造工艺技术现状与发展趋势

周哲1,付丙磊1,王栋1,2,颜秀文1,高德平1,王志越1

(1.中电科电子装备集团有限公司,北京100070;2.中国电子科技集团公司第四十八所,湖南长沙410111)

对当前集成电路制造工艺的主要挑战、研究现状进行了综述,并对其发展趋势进行了展望。

集成电路;摩尔定律;特征尺寸;制造工艺

电子信息产业的核心与基础,是一个国家经济发展、科技发展和国防实力的重要标志。由于在计算机、移动通信、消费电子、半导体照明、汽车电子等国民经济各个领域的广泛应用,集成电路产业已经成为信息产业的基石。自1958年第一块集成电路问世以来,集成电路产业已经过50多年的发展,产业技术不断进步,分工越来越细致。集成电路制造环节仍然遵循着摩尔定律(集成电路芯片上所集成的电子元件的数目,每隔18个月就翻1倍)快速向前发展,延续摩尔定律的先导技术研究依然是全球热点。目前世界集成电路产业28~14 nm工艺节点已趋于成熟,10 nm工艺节点刚刚进入量产,7 nm及其更小节点正在处于研发阶段。在集成电路特征尺寸不断减小的过程中,微纳加工、电路互联、器件特性等方面都面临巨大的挑战。

本文综述了当前集成电路制造工艺技术的主要挑战和研究现状,并对其发展方向进行了展望。

1 集成电路前道制造工艺技术

集成电路前道工艺是指从原始晶片开始至中测封装之前的所有工序过程,即集成电路上晶体管等元器件的制备与互联过程。在集成电路特征尺寸减小、集成度增大过程中的主要技术挑战有微细加工技术、电路的互联技术、以及晶体管等器件特性的退化等。

1.1 微细加工技术

微细加工技术,尤其是光刻技术,是集成电路元器件特征尺寸减小的基础,光刻系统的分辨率R决定了可以加工的最小线宽。光刻系统的分辨率R可以用式(1)表示[1]。其中,λ为光刻机光源波长、NA为光刻机数值孔径(NA=n sin θ,n为光刻胶与物镜之间介质折射率,θ为物镜孔径角的一半)、k1为光刻机工艺因子。

从式(1)可见,光刻机分辨率与光源波长成正比,与光刻机数值孔径成反比,为了得到更细的加工线宽,就要求光源波长尽可能减小,数值孔径尽可能增大。理论上,通过不断减小光刻机光源波长、增大数值孔径的方法可以获得足够的光刻机分辨率。但是减少光刻机光源波长、增大数值孔径又会减小光刻机的焦深(DOF),如式(2)所示,其中λ为光刻机光源波长,NA为光刻机数值孔径,k2为光刻机工艺因子。

光刻机的正常工作离不开一定的焦深,焦深过小时,曝光光线无法获得满意的聚焦,因而在调整光刻机的曝光光源波长和数值孔径之外,还需要通过控制工艺因子k1、k2的方法来保证足够的分辨率和焦深。

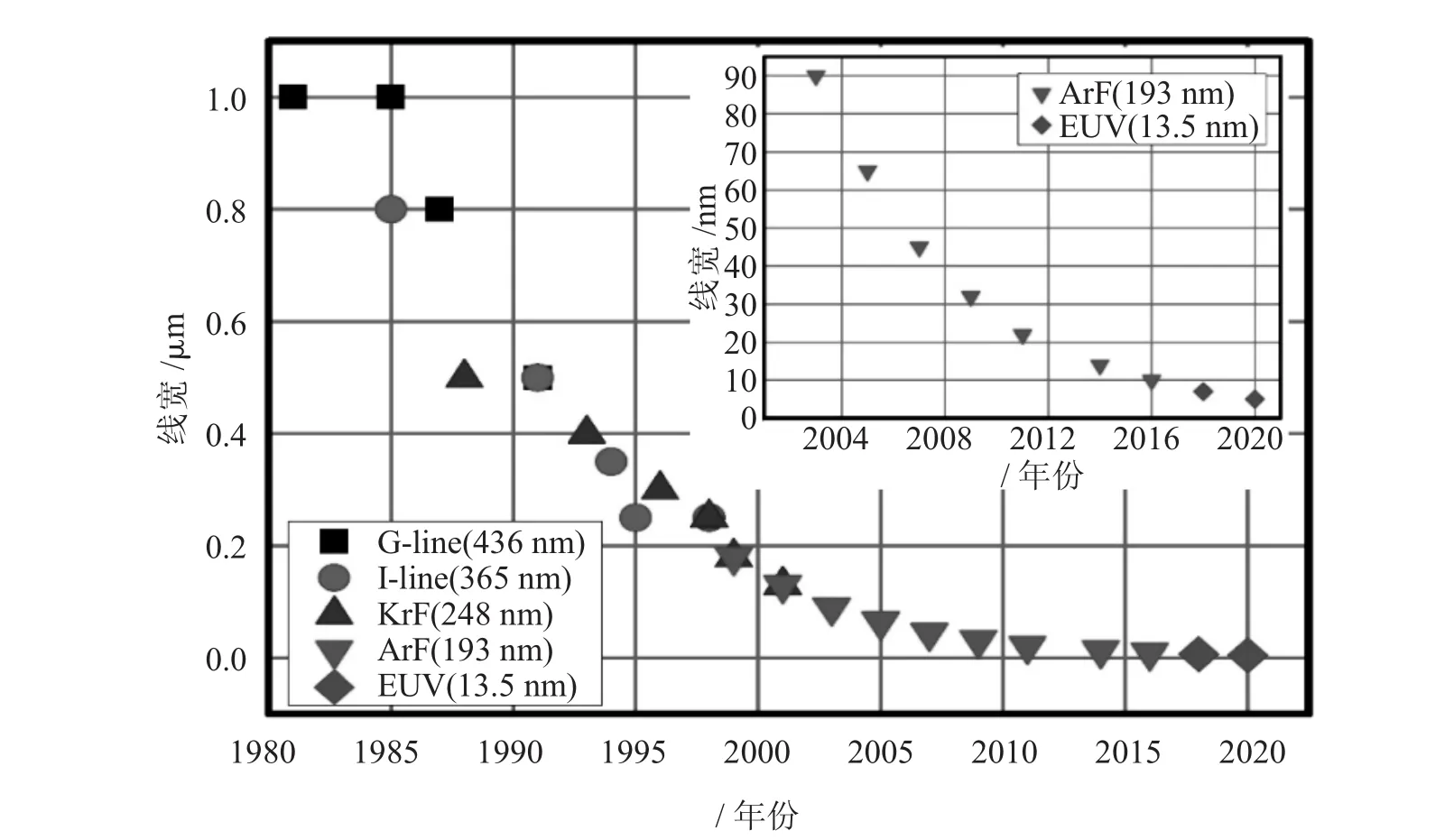

光源波长的不断缩短在光刻机的技术进步中扮演了重要的作用。首台商用光刻机为尼康NSR1010G型光刻机,使用436 nm的g线光源,分辨率为1 μm。436 nm g线光源可以满足最低至0.5 μm的光刻要求。之后365 nm的i线光源可满足0.80~0.25 μm的光刻要求,248 nm的KrF准分子激光光源可满足0.50~0.13 μm的光刻要求,193 nm的ArF准分子激光光源可以应用于0.13~10.00 nm线宽的曝光。由于EUV等更短波长光刻机研发难度巨大,传统干法光刻技术在向45 nm及以下节点发展时遇到了巨大的困难。在采用193 nm ArF光源不变的前提下,人们通过采用浸没式光刻加双重曝光的手段,成功将193 nm ArF光源的寿命延伸至45 nm、28 nm、22 nm、14 nm乃至10 nm。浸没式光刻将传统光刻技术中镜头与光刻胶之间的空气介质更换为折射率更大的液体介质(目前常用的液体介质的折射率为1.44的水),从而增大数值孔径,进一步提高光刻机分辨率[2]。进入10 nm以下节点后,如果继续使用193 nm光源,需要使用3次或3次以上的多重曝光,大大增加了光刻成本。目前,随着EUV光源功率等问题逐渐得到解决,13.5 nm的EUV光源成为10 nm以下工艺节点的首要选择。2016年荷兰ASML公司EUV机台性能逐步稳定,产能已经接近每天曝光1 500片晶圆,三星、台积电、英特尔等晶圆厂陆续宣布将在7 nm及以下节点上采用EUV技术。光刻机光源波长与特征尺寸的对应关系见图1。

在光刻机设备的开发中,除了不断开发更短光源、增大数值孔径之外,人们还会采用多种分辨率增强技术,通过降低工艺因子k1增大工艺因子k2的方法改善光刻机的分辨率和焦深,在光源波长难以取得突破性进展的情况下进一步提升光刻机性能。分辨率增强技术主要包括相移掩模技术、离轴照明技术、邻近效应校正等[3]。

1.2 电路互联技术

电路互联方面的挑战,当前集成电路芯片上集成的晶体管数量已达数十亿个,需要通过互连线为这些晶体管提供能量和时钟信号。随着集成电路特征尺寸的减小和晶体管数量的增加,金属互联线的长度不断增加、横截面积不断减小,从而引起互联线电阻的增加;互联线间距减小也会引起互联线电容的增大,同时随着工作频率的不断提高,寄生电感效应也必须考虑在内。在超大规模集成电路中,限制集成电路性能的主要因素不是器件的门延迟,而是互连线的寄生元件引起的互联延迟、电路功耗以及互连线之间信号的串扰。

图1 光刻机光源与特征尺寸的对应关系

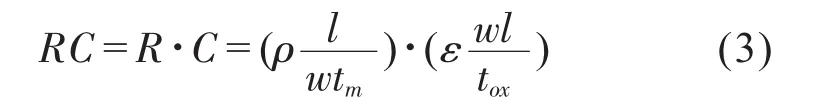

互联延迟和电路功耗:金属互联线的延迟时间以RC时间常数来表征,如式(3)所示,其中R为互联线电阻,C为互联线电容,ρ为互联材料电阻率,l为互联线长度,w为互联线宽度,tm为互联线厚度,tox为互联线间介质层厚度,ε为介质材料介电常数。

另一方面,互联线长度的不断增加、截面积的不断减小,都会导致互联线电阻上升,从而引起电路功耗增大[4]。

目前,减少互联延迟及电路功耗的方法主要由以下3种:(1)采用电阻率ρ更低且可靠性更高的材料作为互联线;(2)采用介电常数ε更低的材料作为互联介质,即低k介质;(3)采用多层布线方法,减少信号传输距离,提高单位芯片面积互联线集成度。

互联线信号串扰:当传输线传输信号时,由于电磁耦合的作用,在相邻的传输线上会产生不期望的信号干扰,有可能导致逻辑电路的误动作。在频率不断提高的情况下,互联线信号串扰日益严重,逐渐成为制约CPU频率提高的制约因素。干扰信号与介质电容成正比,因而采用选择低k介质的方式作为互联线间日益增大的信号串扰的应对手段。

综上所述,采用电阻率较低的金属互联材料,介电常数较低的介质层材料是解决超大规模集成电路互联问题的重要手段。集成电路中最早使用的互联金属材料为铝及其合金材料,具有以下优点:室温电阻率较低(2.8 μΩ·cm),与Si材料附着性好,易于沉积与刻蚀。从130 nm工艺节点开始,传统的铝合金互联已经达到其性能极限,当前一般选用电阻率和可靠性均较好的铜替代铝作为合金材料。铜的室温电阻率(1.7 μΩ·cm)相对铝更低,因而可以有效降低互联电阻,降低互联层厚度,进而减少互联层间分布电容,从而解决互联延迟、电路功耗、信号串扰问题。工艺方面,铜的熔点(1 083℃)高于铝的熔点(660℃),在较高的电流密度作用下,互联引线中的铜原子相对铝原子发生迁移的能力较低,提高了金属互联的可靠性。由于铜金属干法刻蚀困难,与传统直接刻蚀金属层制备互联线的方法不同,铜互联线的制备需要先刻蚀介电层,再填充金属,即大马士革工艺。介质材料方面,从90 nm工艺节点开始,传统的二氧化硅材料已经无法适应超深亚微米节点的工艺要求,因而需要采用介电常数更低的介质材料,即低k介质材料。低k介质材料种类很多,如掺杂二氧化硅、多孔二氧化硅、有机聚合物、无机聚合物、有机/无机混合物等,除较低的介电常数外,低k介质材料还需要有足够的机械强度以支撑多层互联线,以及与化学机械平坦化工艺的兼容性等。

1.3 器件特性的退化

集成电路的核心器件是MOS晶体管,理想的MOS器件应该有较大的工作电流,同时要求在关态时有很小的泄漏电流,以提高器件驱动能力,降低功耗。随着器件特征尺寸进入纳米尺度,栅、沟道等方面都面临较大的挑战。

1.3.1 栅极方面的挑战

栅极方面,随着器件尺寸的等比例缩小,为了保持栅极对沟道的控制能力,在栅极材料不变的情况下,需要减薄栅氧层厚度,栅氧层厚度减少到一定程度后,量子隧穿效应影响逐渐增大,引起栅漏电流的增大,会增加器件功耗,降低栅氧可靠性。

进入45 nm节点以后,为了避免栅泄漏电流的增加,人们引入了介电常数更高的绝缘材料作为栅极,即所谓的高k介质材料。高k介质研究热点集中在铪(Hf)基材料上,以二氧化铪(HfO2)为例,其介电常数高达25,与之对应的,二氧化硅介电常数仅仅为3.9。与二氧化硅栅极不同,高k介质材料无法通过简单的栅氧化工艺获得,而只能采用沉积的方式,为了获得高质量的高k介质栅极,一般采用原子层沉积(ALD)的方法。原子层沉积是一种高精度的化学沉积方式,通过交替脉冲通入两种反应前驱体,使得每个脉冲过程只生长一个原子层的薄膜,从而达到对薄膜组分和厚度的精确控制。

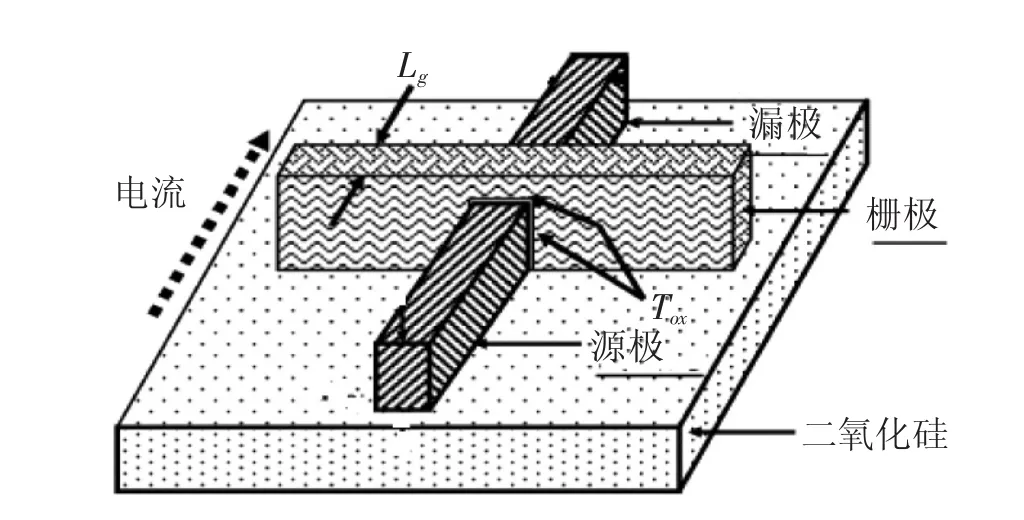

进入14 nm节点以后,为了进一步增强栅对沟道的控制能力,鳍式场效晶体管(FinFET)结构被引入先进集成电路制程,与传统平面晶体管不同,Fin-FET结构中沟道由绝缘衬底上凸起的高而薄的鳍(fin)构成,源漏两级分别在其两端,三栅极紧贴其侧壁和顶部,增大了栅与沟道的接触面积,可以有效增强栅对沟道控制,减少漏电。FinFET结构的示意图见图2所示[5]。在未来的5 nm及以下节点中,为进一步增大栅与沟道的接触面积,结合纳米线沟道的围栅(GAA)晶体管已经被提出,这种结构中沟道完全被栅极包围,具有卓越的静电控制能力[6]。

1.3.2 沟道方面的挑战

图2 FinFET结构示意图[5]

沟道方面,沟长度缩短将带来短沟道效应、热载流子效应、高场下的迁移率退化等。短沟道效应,沟道长度减少到一定程度后,源漏的耗尽区在整个沟道中所占的比重增大,栅下面的硅表面形成反型层所需的电荷量减小,因而阈值电压减小。阈值电压的减小会使得亚阈值电流指数增加,阈值电压每减小0.1 V,截止态的泄露电流将增大10倍,大大增加器件功耗。热载流子效应,器件尺寸进入深亚微米尺寸范围,器件内部的电场强度随器件尺寸的减小而增强,特别在漏结附近存在强电场,载流子在这一强电场中获得较高的能量,成为热载流子。一方面,热载流子可以越过栅极势垒,进入氧化层中,不断积累,从而改变阈值电压,影响器件寿命;另一方面,热载流子在漏极附近的耗尽区中与晶格碰撞产生电子空穴对,碰撞产生的电子/空穴形成附加的漏电流,被衬底收集则形成衬底漏电流,增大器件功耗。高场下的迁移率退化,低场下迁移率是常数,载流子速度随电场线性增加。高场下迁移率下降,载流子速度达到饱和,不再与电场有关,进而影响器件的驱动电流。

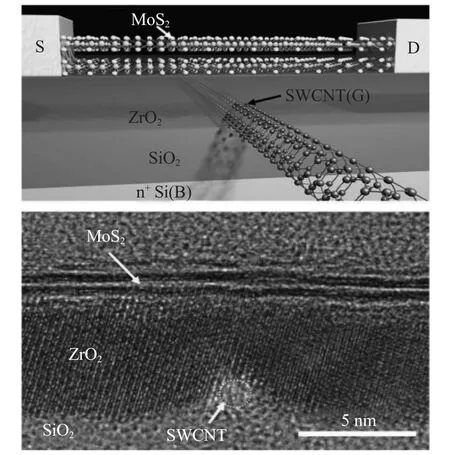

为了减小短沟道效应引起的阈值电压降低,源漏延伸区的结深需要减小,超浅结工艺技术成为研发的一个热点问题。超浅结工艺一般采用低能大束流离子注入工艺。为了应对高场下的迁移率退化,一般需要采用高迁移率沟道材料。应变SiGe相对于传统Si来说具有更高的迁移率,是晶体管能够进入90 nm节点的关键,而随着晶体管特征尺寸的进一步缩小,在7 nm及以下节点,人们开始逐渐考虑GaAs等III-V族高迁移率材料代替应变SiGe作为沟道。同时,二硫化钼(MOS2)等二维半导体材料,由于其高迁移率特性,以及天然的抑制短沟道效应的能力(为抑制短沟道效应,一般要求沟道宽度在沟道厚度3倍以上,而二维半导体的超薄厚度,可以有效抑制短沟道效应发生),近年来成为研究热点,劳伦斯伯克利国家实验室2016年研制出世界上首个栅长1nm的晶体管,沟道就是基于二硫化钼(MoS2)材料[7],栅极是由单壁碳纳米管(SWCNT)构成,图3为该晶体管的示意图和透射电镜图像。

图3 世界首个栅长1 nm晶体管[7]

2 集成电路后道制造工艺技术

集成电路后道工艺指从中测开始至集成电路完成直到出厂之间的所有工序。包括晶片减薄、划片、芯片粘接、键合、封装等工艺流程。后道封装主要有传递电能、传递的电路信号、提供散热途径、提供结构保护与支持等功能。集成电路后道封装当前向着小型化、适应高发热、高密集度、适应多引脚等方向发展,3D集成和晶圆级封装(WLP,Wafer Level Package)逐渐成为未来发展趋势。

2.1 3D集成

3D集成依赖于3D堆叠技术和TSV工艺,3D堆叠技术是把两个或两个以上不同功能的芯片或结构,减薄后,通过键合等堆叠技术,使其在Z轴方向上形成立体集成和信号连通的三维立体堆叠加工技术,TSV是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术。三维封装技术能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,大大改善芯片速度和降低功耗。同时还可以通过把不同的功能芯片(射频、内存、逻辑、数字、MEMS等)集成在一起,实现电子元器件的多功能化。

2.2 晶圆级封装

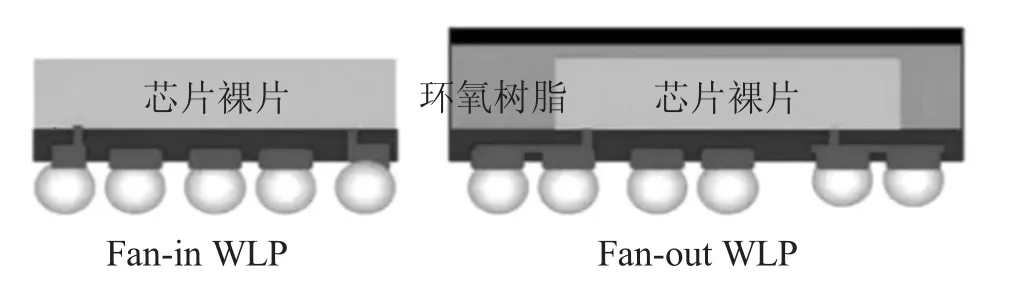

晶圆级封装的一般定义为直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割(singulation)制成单颗组件。而重新分配(redistribution)与凸块 (bumping)技术为其工艺关键。WLP封装具有封装尺寸较小,电性能较好的优势,但目前较为成熟的晶圆级封装技术,在单颗芯片上的植球数有一定限制,多用于低脚数消费性IC的封装应用,在高接脚数的芯片如通讯芯片等上应用一直受限。为了解决晶圆级封装植球数不足问题,扇出晶圆级封装(Fan out WLP)技术应运而生(见图4),扇出晶圆级封装将晶片嵌入环氧树脂等材料中,形成重组晶圆,然后利用前道隔离和平坦化工艺将互联扇出到芯片周围区域,加入焊球,有效增大了芯片可焊球面积。随着苹果在iPhone 7上的A10处理器和天线开关模组使用扇出晶圆级封装技术代替传统PCB,已发展多年的扇出封装技术未来将被更多芯片业者采纳。

图4 Fan-in和Fan-out封装

3 结束语

集成电路已经按摩尔定律的预测向前不断发展了超过半个世纪,新材料、新工艺和新结构的不断应用,仍然推动集成电路的集成度不断提高,特征尺寸进一步降低。随着集成度的进一步提高,由于互联、器件特性等方面的影响,当前集成电路速度与功耗的矛盾凸显,功耗越来越成为集成电路发展的瓶颈因素,成为集成电路制造工艺中无法回避的热点问题。

另一方面,除了进一步推动集成电路集成度不断提高、特征尺寸不断降低之外,超越摩尔定律的概念逐渐在业界产生重要影响。与追求晶体管密度不断提升的摩尔定律不同,超越摩尔定律旨在基于成熟的集成电路工艺,将IC与分立器件(如传感器、MEMS等)集成在一起,形成具有某种特定功能的集成微系统。3D集成,晶圆级封装等技术是超越摩尔定律的重要路径之一。集成微系统的发展将进一步提升各类电子设备的性能,并为多学科技术的融合应用奠定基础。

[1] 李艳秋.光刻机的演变和发展趋势[J].微细加工技术,2003,(2):1-5.

[2] 何鉴,高子奇,李冰,等.193 nm浸没式光刻材料的研究进展[J].半导体技术,2008,33(9):743-747.

[3] 冯伯儒,张锦,侯德胜,等.相移掩模和光学邻近效应校正光刻技术[J].光电工程,2001,28(1):1-5.

[4] 王鹏飞,丁士进,张卫,等.低k介质对CMOS芯片动态功耗的影响[J].自然科学进展,2001,11(3):317-321.

[5] SE.Thompson,RS.Chau,T.Ghani,et.al.In search of“forever”,continued transistor scaling one new material at a time[J].IEEE Transactions on Semiconductor Manufacturing,2005,18(1):26-36.

[6] N.Singh,A.Agarwal,L.Bera,et.al.High-performance fully depleted silicon nanowire(diameter≤5 nm)gateall-around CMOS devices[J].IEEE Electron Device Letter,2006,27(5):383-386.

[7] SB.Desai,SR.Madhvapathy,AB.Sachid,et.al.MoS2transistors with 1-nanometer gate lengths[J].Science. 2016,354(6308):99.

Current Situation and Development Tendency for the Integrated Circuits(ICs)Manufacture Technologies

ZHOU Zhe1,FU Binglei1,WANG Dong1,2,YAN Xiuwen1,GAO Deping1,WANG Zhiyue1

(1.The CETC Electronic Equipment Group Co.,Ltd.,Beijing 100070,China 2.The Research Institute of CETC,Changsha 410111,China)

The bottleneck and current research situation of IC manufacture technologies were summarized.This paper also gives a prediction of the future IC technology development

ICs;Moore law;Feature size;Manufacturing process

TN405

A

1004-4507(2017)03-0034-06

周哲(1980-),男(汉族),辽宁省大石桥市人,毕业于辽宁大学信息科学与技术学院,学士学位,工程师,现主要从事集成电路工艺设备等科研项目管理工作。

2017-05-08