可扩展级联式机载数据采集系统设计

2017-07-31胡晓峰王红亮彭晴晴

胡晓峰,王红亮,彭晴晴

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中国兵器工业集团第207研究所,山西 太原 030051)

可扩展级联式机载数据采集系统设计

胡晓峰1,王红亮1,彭晴晴2

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中国兵器工业集团第207研究所,山西 太原 030051)

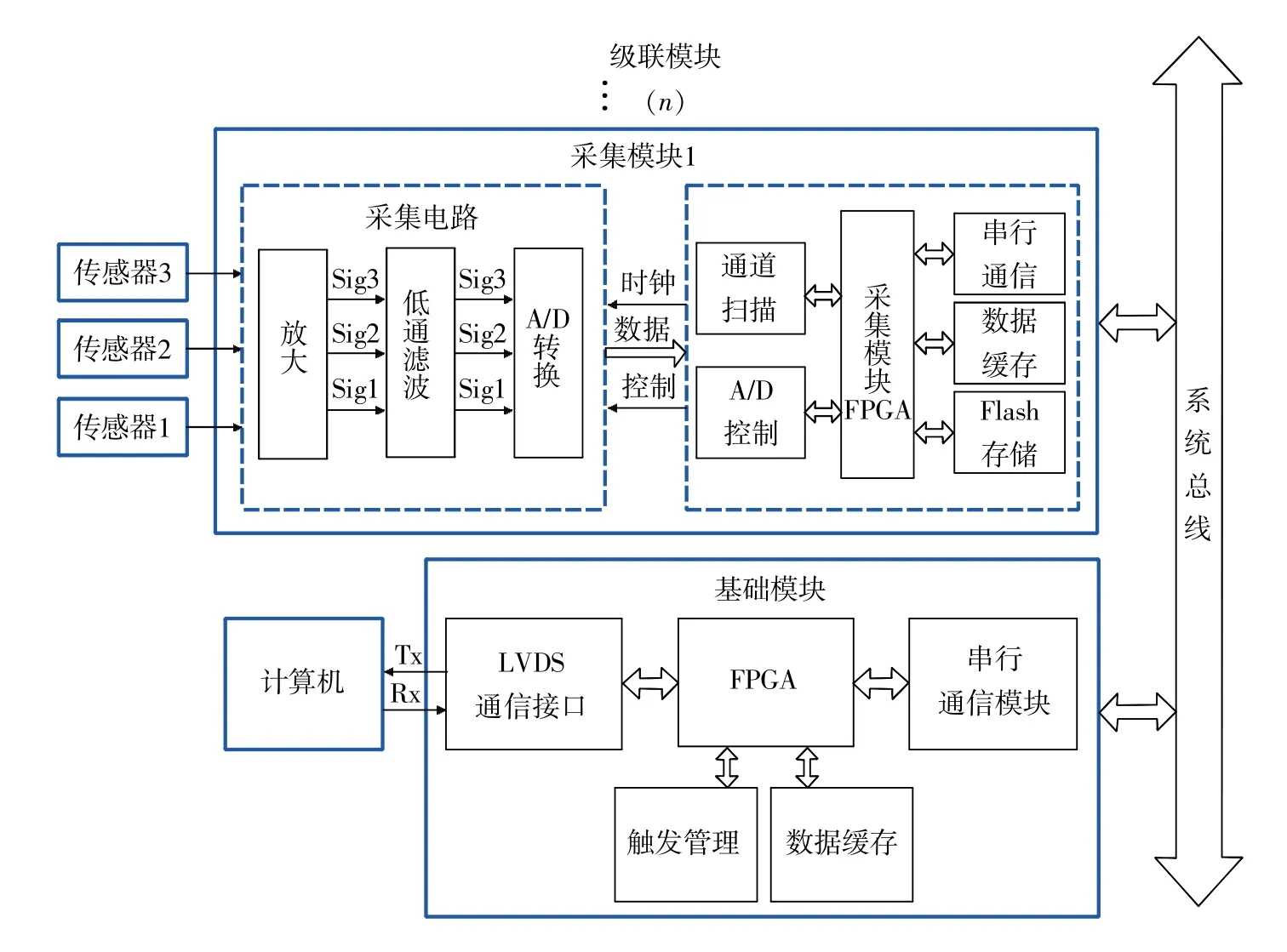

为实时采集飞行器舱体各部位的振动、冲击、压力等多路信号,设计一种通道可自由扩展的级联式机载数据采集系统。以FPGA为核心控制器设计基础模块和传感器采集模块,通过将多个采集模块堆叠级联的方式实现对任意通道的扩展。采集模块内置信号调理和采集电路、存储和控制电路,采集数据按通道编帧后分层存储。基础模块通过级联总线发送触发或读数指令,控制采集进程,并利用LVDS电缆将数据上传到计算机进行波形分析。实际测试表明:该系统能根据应用需求灵活扩展通道数量,同步采集时单通道采样率≥300kS/s,电压转换误差<0.2%,具备体积小、易维护等特点。

数据采集;通道扩展;级联;低压差分信号

0 引 言

在飞行器舱体测控系统中,对振动、冲击、压力、应变等多路信号的采集和分析是设备研发的重要一环。机载数据采集系统由于长时间工作在高速、高温、强振等恶劣环境下,对仪器结构和可靠性设计要求都较高[1-2]。为了解决当前数据采集系统存在的仪器体积过大、安装维护不便、通道固化、连线复杂等突出问题[3-4],本文采用级联式总线通信模式,设计了一种通道可自由扩展的机载数据采集系统。

级联式总线通信模式在网络交换机的数据传输中较为常见,采用级联结构不仅可以简化采集系统的物理接线方式,还便于对挂载在总线上的各个数据通道集中管理[5]。为了实现自由扩展的目的,本系统利用总线通信协议,将独立工作的采集模块层层堆叠,通过控制总线和数据总线实现采集模块与基础模块之间的数据传输。各模块内置独立控制器,当采集模块的数量发生变化时,不会对系统中的其他部分产生影响,通过增减采集模块的数量即可实现对任意通道的扩展,无需调整基础模块。

1 系统设计

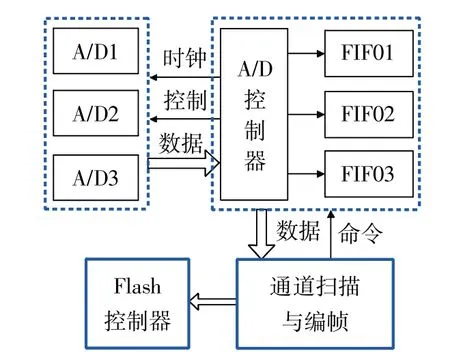

舱体振动或压力传感器输出的模拟信号带宽约为40 kHz,峰峰值约为250 mV,为满足多节点测试要求,本系统采用XILINX公司生产的SPARTAN6 FPGA作为核心控制器,将采集系统划分为基础模块和传感器采集模块两部分。系统组成框图如图1所示。

在采集模块设计中,单个采集模块外接3路压阻式传感器,传感器输入信号经过放大、低通滤波和阻抗匹配后进入3路独立A/D转换器,在FPGA的控制下模拟信号被逐路选通并采集;采集数据以一定的帧格式经过缓存后被写入Flash存储器;当采集模块收到读数指令后,FPGA控制器将采集数据按照串行通信协议送入基础模块中。采集系统的触发和读数由基础模块统一管理,基础模块一方面与上位机实时通信,将采集指令发送给各采集单元;另一方面读取各采集模块中的数据,并将数据通过LVDS接口芯片以差分码流的形式上传到计算机进行波形分析。基础模块与采集模块之间通过插针连接,通信协议自行设定。

2 硬件设计

为了满足自由扩展采集通道数量的设计要求,每个采集模块都采用相同的硬件设计,使用RFID芯片对模块“身份”进行标识[6]。采集模块硬件设计主要包括信号调理电路、A/D转换电路和存储控制模块等;基础模块设计主要包括触发管理、通信总线、LVDS接口电路等部分。

2.1 信号调理与采集电路设计

图1 级联式机载数据采集系统框图

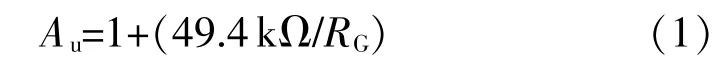

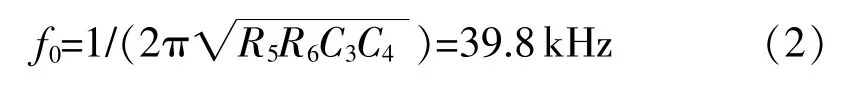

机载加速度传感器的输出为数百毫伏的微弱电压信号,为了匹配A/D转换芯片的输入量程,系统设计了前端仪表放大器、低通滤波电路和电压跟随器对信号进行调理,信号调理电路如图2所示。传感器输出的差分信号VIN+和VIN-通过耦合电容C1和C2进入仪表放大器AD8226的输入端,为满足AD8226的工作要求,使用偏置电压REF1将基准电压嵌位在1.25V。AD8226是一款高精度、宽增益的仪表放大器[7],在1~1 000的增益范围内使用单电源供电,通过调节外接电阻RG(图2中的R3+R4)的大小就可以方便设置放大倍数,具体计算公式为

根据实际需要,本文设计使用5.5kΩ的串联电阻将输入信号放大10倍后送入滤波电路。

飞行器各设备之间存在较多串扰信号,这些串扰信号产生的高频杂波容易使输出波形产生尖峰毛刺。为了获得平滑的波形曲线,在A/D转换电路前设置了2阶低通滤波电路[8-9]。在图2中,电阻R5、R6和电容C3、C4与AD8606组成2阶有源巴特沃斯低通滤波器,阻带衰减率为每倍频12dB。AD8606为内置双运放芯片,一方面为AD8226提供1.25V的偏置电压;另一方面以电压跟随器的形式将滤波信号送给A/D转换芯片,实现输出端的阻抗匹配。由于机载设备输出的振动或冲击信号最高频率不超过40 kHz,故将滤波器截止频率设置为

使用ADI公司的12位ADC芯片AD7495作为模数转换器,该芯片的输入为0~2.5V的电压信号,转换数据以串行方式输出,单通道最高采样率为1MS/s,完全满足对机载设备振动信号的采集需求,采集电路如图2所示。

2.2 存储控制模块设计

Flash芯片采用Micron公司的MT29F16G08-ABABAWP芯片,存储容量为16GB,接口位宽为8位。由于3路ADC独立工作,采集模块使用3路FIFO对A/D转换芯片输出的串行数据进行缓存,以通道扫描的方式依次判断FIFO的状态并读数。为使数据采样速率保持在平衡态,需对缓存FIFO达到半满状态的通道优先读数,避免3路数据在存储时发生冲突。为了区别不同采集通道的数据,在数据写入Flash之前先对其添加2 bit的通道标志位,将采集数据编帧处理。数据存储控制结构如图3所示。

图2 调理与采集电路原理图

图3 数据存储控制结构图

扩展之后单帧采集数据占用两个字节的存储空间,其中低bit11~0为A/D有效数据位,bit13和bit12为通道标志位,bit15和bit14为校验位。写Flash时先写入低8位,后写高8位。

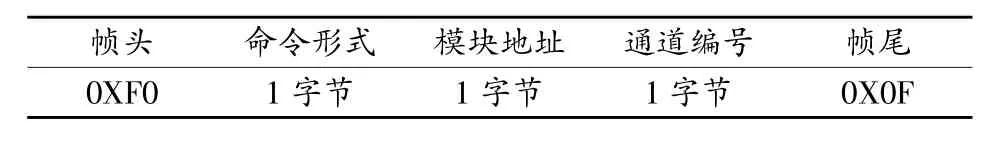

2.3 系统总线设计

基础模块具有外部触发和软件触发2种触发方式。外部触发有效时,所有的采集模块处于采集状态;软件触发有效时,可以控制一个或多个采集模块工作。根据全双工的设计要求,基础模块向采集模块发送的命令形式主要包括采集、读数、擦除和重新发送等,模块间的通信命令帧格式如表1所示。

表1 数据通信命令帧格式

本通信系统将帧头设定为0XF0,帧尾设定为0X0F,读数、擦除和重新发送指令分别设定为0X11、0X21和0X31。将指令信号最低位取反作为相应的取消指令,例如将读数指令设为0X11,停止读数指令则设为0X10。采集指令分为外部触发和软件触发两种形式,分别设定为0X41和0X51。当采集指令为外部触发时,命令帧中省去模块编号和通道编号,直接发送帧尾标志。

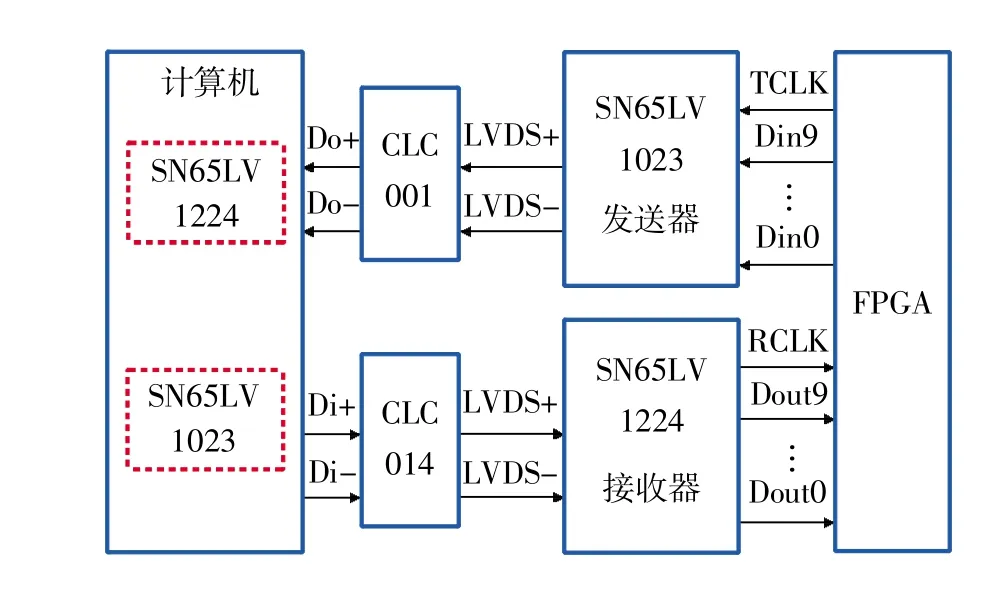

2.4 LVDS通信接口设计

基础模块收到采集数据后需要通过15 m长的电缆将数据上传到计算机进行处理。为了提高抗干扰能力、降低传输误码率,采用TI公司生产的LVDS接口芯片SN65LV1023和SN65LV1224实现长线数据传输[10]。在数据发送端使用CLC001芯片对LVDS信号进行预加重处理,在接收端使用CLC014芯片对信号进行均衡[11]。该LVDS芯片组为10位总线型应用芯片,对不同的传输速率具有自适应能力,时钟频率范围为10~66MHz,最高数据率达790Mb/s。数据发送和接收结构图如图4所示。

图4 数据发送和接收结构图

3 应用程序设计

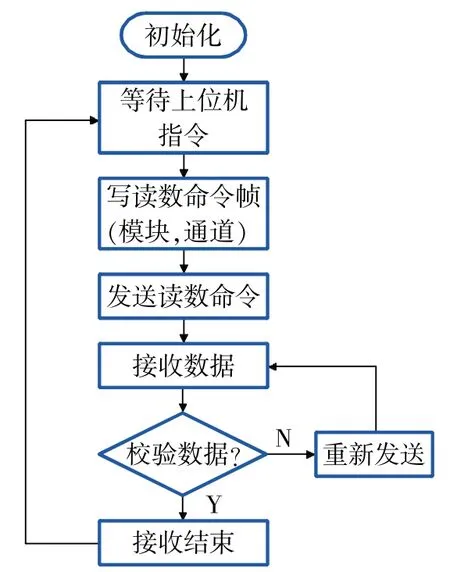

3.1 读数程序设计

基础模块发送读数指令和接收数据的工作流程图如图5所示。系统上电完成初始化设置后,开始接收上位机的读数指令,并按照通信协议将要读取的模块编号和通道信息写入命令帧中。系统对多个采集模块读取数据时,基础模块对各个采集模块轮流发送采集指令。当发送完对第i个采集模块的读数命令后,将接收数据使能端EN置为有效,开始接收地址为i的采集模块的数据。若数据在传送过程中出现误码导致校验失败,基础模块将发出重新发送数据的请求。校验成功的数据被写入基础模块的缓存FIFO中,之后开始读取下一个采集模块中的数据。

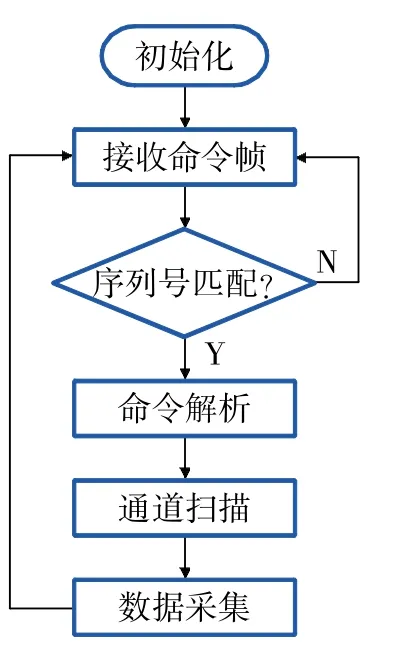

3.2 采集程序设计

数据采集的工作流程图如图6所示。初始化结束后采集模块开始接收系统指令,并将指令中的地址信息与自身序列号进行比对,只有信息匹配成功后采集模块才会接收采集指令并启动相应的采集通道。当采集模块中的多个通道同时被选通时,使用通道扫描的方式依次选通各通道,并将采集数据写入存储器中。

图5 基础模块读数流程图

图6 数据采集工作流程图

4 系统测试

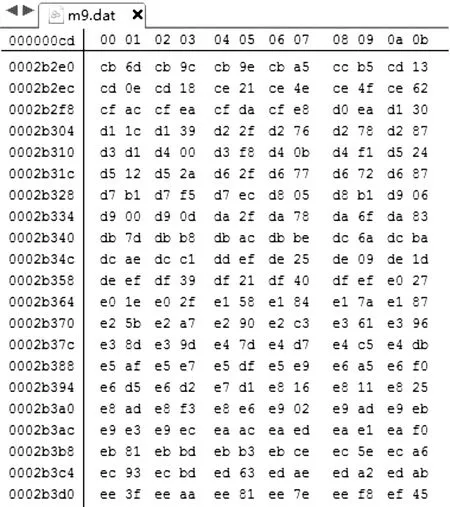

使用信号发生器作为模拟信号源,输出频率为10 kHz、峰峰值为250 mV的正弦波信号;根据舱体振动信号的输出带宽,将A/D采样频率设置为300kS/s,数据采集速率为1.8MB/s。为了测试系统的同步采集性能,把3路输入信号线接在同一采样点上,将采集数据编帧后上传至计算机,导出其中一路波形解析文件如图7所示。

图7 正弦波波形解析文件

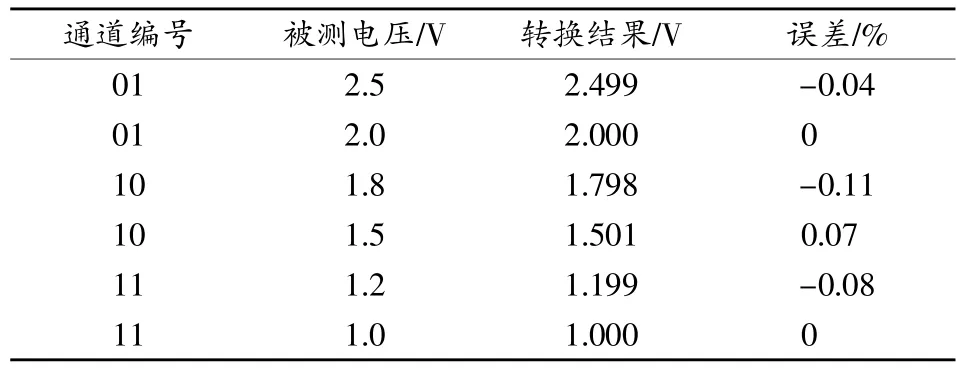

上位机收到采集数据以后,按照帧结构解析波形数据,取5次测量结果的平均值,按照AD7495电压转换公式反向计算可得到电压测量值,测量结果如表2所示。经计算可知,系统采集到的电压幅值与被测值误差小于0.2%,满足振动信号的采集精度需求。

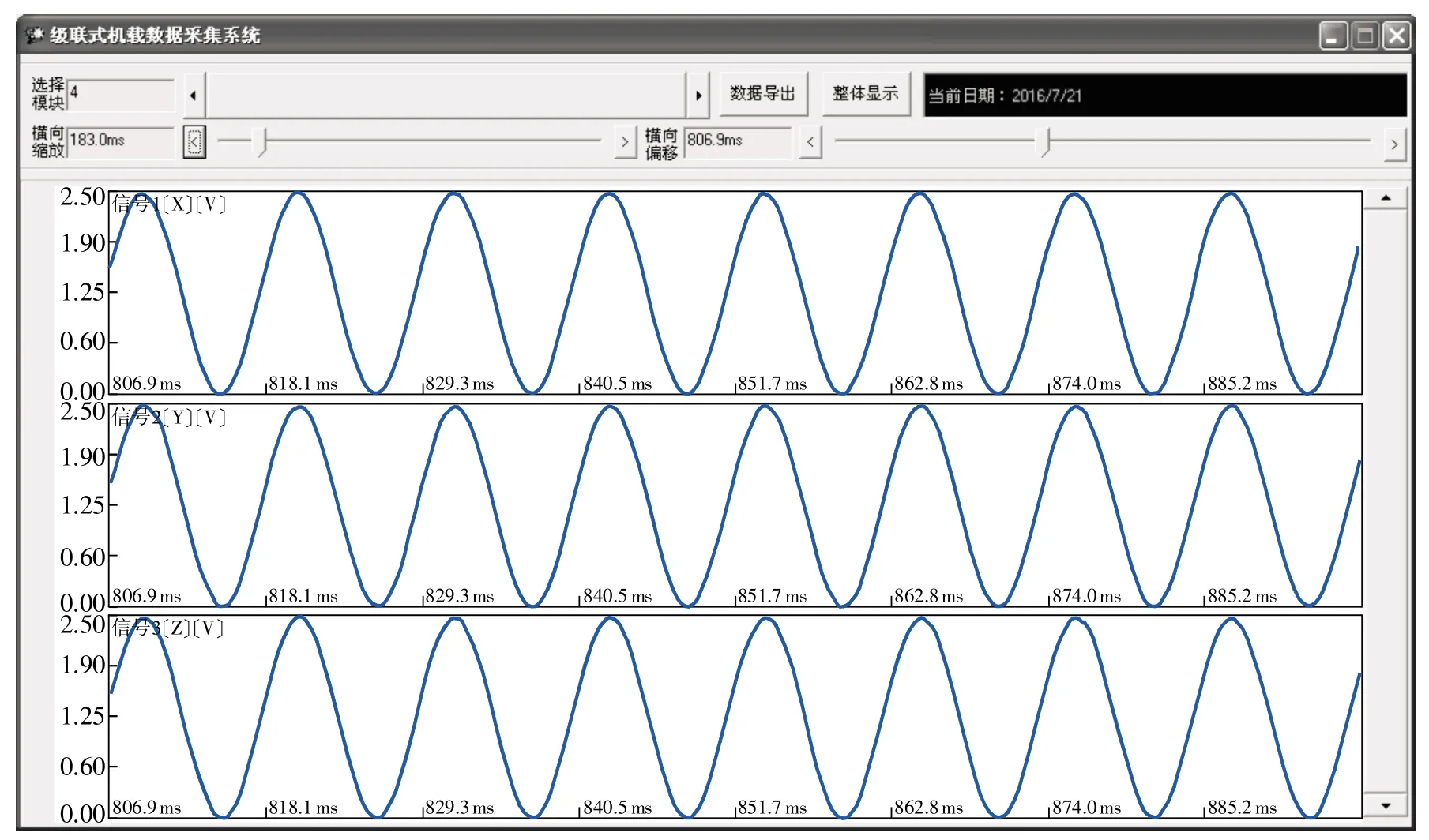

图8 采集数据波形图

表2 测量结果

为进一步验证采集系统的性能,采用多模块叠加的级联模式对数据进行采集和分析。采集结束后通过上位机选择并读取4号采集模块中的数据,其中3个采集通道的波形显示结果如图8所示。由图可知,虽然3路A/D转换器在采集过程中存在通道扫描的先后顺序,但FPGA的扫描速度为纳秒级,远高于ADC的量化和编码过程,系统对模拟信号的采集达到了伪同步的效果,由此进一步证明了采集系统的可靠性。

5 结束语

本文设计以FPGA为核心控制器,使用级联式总线通信方式,将各个传感器采集模块堆叠起来,形成一种通道可自由扩展的机载数据采集系统。采集模块之间采用插针连接,结构设计遵守相同的电气标准,简化了仪器的物理接线方式。针对装备测试过程中不能灵活扩展采集通道的问题,提出了一种有效的解决方法。

[1]霍朝晖,魏建新,覃燕.飞行试验机载网络数据采集与分析技术[J].现代电子技术,2011,34(11):144-147.

[2] 向建军,夏海宝,许蕴山.基于DSP的机载数据采集记录系统的设计[J].航空计算技术,2011,41(3):106-109.

[3] 胡海涛,索涛,李玉龙,等.飞机结构振动监测用微型测试系统研制[J].实验力学,2014,29(1):12-17.

[4]田方正,皇甫大宏,沙永忠.新一代机载数据采集系统的发展综述[J].测控技术,2007,26(3):16-18.

[5] 甄国涌,郝晓鹏.基于级联模式的多通道数据采集系统设计[J].自动化与仪表,2011,26(2):50-52.

[6] 孙克辉,熊迁.集成电路RFID芯片测试系统设计与实现[J].仪表技术与传感器,2013(11):44-46.

[7] 赵亮,刘先勇,袁长迎,等.微弱信号调理电路的设计及研究[J].西南科技大学学报,2010,25(1):64-67.

[8] 曹恒,秦颖颀,王春,等.两线制IEPE传感器前置信号调理电路[J].仪表技术与传感器,2012(11):160-162.

[9]史志辉,林君,周逢道.基于虚拟仪器的高准确度同步采集系统[J].中国测试,2016,42(2):67-70.

[10]储成君.基于FPGA的多通道模数混合采集装置的设计及实现[D].太原:中北大学,2014.

[11]张小军,廖风强,王录涛,等.多通道高速串行LVDS信号解串器设计[J].电子测量技术,2013(4):63-67.

(编辑:商丹丹)

Design of extension cascade airborne data acquisition system

HU Xiaofeng1,WANG Hongliang1,PENG Qingqing2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China;2.Chinese Ordance Industry Group 207 Research Institute,Taiyuan 030051,China)

A cascade airborne data acquisition system with extended channels was designed for real-time acquisition of vibration,shock and pressure signals from various parts of aircraft cabin.The basic module and sensor acquisition module applied FPGA as the core controller,and the extension of any channel was realized by stacking modules in a stack.Acquisition module was built with signal conditioning and acquisition circuit,storage and control circuit,and the data was stored by layer in frame of channels.Basic module transmitted the trigger or read instruction via cascade bus to control the acquisition process,and uploaded data to the computer for waveform analysis through LVDS cable.The test shows that the instrument could extend the number of channels flexibly according to the application requirements.The single channel sampling rate was not less than 300 kS/s in synchronous acquisition,and voltage conversion error was lower than 0.2%,which had characteristics of small size and easy maintenance.

data acquisition;channel extension;cascading;LVDS

A

1674-5124(2017)06-0083-05

10.11857/j.issn.1674-5124.2017.06.018

2016-10-05;

2016-11-16

国家自然科学基金项目(51425505)

胡晓峰(1990-),男,山西临汾市人,硕士研究生,专业方向为振动和冲击数据采集系统。