基于CPLD的多路数字信号复接分接技术与实现

2017-07-19曾舒婷嵇孝明徐黄涛

曾舒婷,嵇孝明,徐黄涛

(南京大学 金陵学院,江苏 南京 210000)

基于CPLD的多路数字信号复接分接技术与实现

曾舒婷,嵇孝明,徐黄涛

(南京大学 金陵学院,江苏 南京 210000)

为提高数字通信系统的信道利用率及准确率,文中提出了一种8路数字信号的复接分接系统设计方案。方案主要采用乒乓操作解决低速数据采集高速输出的数据丢失问题。并且基于QuartusII 11.0软件完成了方案的复接分接系统设计与仿真,通过在 Altera的EPM570T100C5N芯片上进行测试。实验结果表明,设计正确且稳定,可应用于多路数字信号通信的实验教学。

多路数字信号;复接;解复接;CPLD

以往数字复接分接系统大多采用ASIC设计,设计电路流程长,且成本过高[1]。而CPLD为可编程数字电路,采用CPLD实现复接分接系统,便于修改电路结构,增强了设计灵活性,并节省了系统资源[2]。本文提供了一种8路数字信号复接与分接的实现方法。其中数字信号复接,采用时分复用的方式,实现了8个支路数字信号的复接。数字信号分接,采用帧同步方法,将复接后的数字信号分解成各个支路的信号[3-6]。

1 多路数字信号复分接器系统设计

多路数字信号复分接器系统设计要求实现64 kHz的 8路8 bit数字信号的复接,并在分接电路中实现512 kHz帧数据8路8 bit的数据分解,其中一路用来传输帧同步数据。

多路数字信号拟采用按字节复用的方法,每次复接每个支路的一位码,复接以后的码序列为第1个8 bit数据为第一路数据,第2个8 bit数据为第二路数据,以此类推。多路数字信号分接器拟采用帧头为10011011的巴克码,巴克码是一种具有特殊规律的二进制码组,它的取值为+1、-1组成的非周期序列。它具有尖锐的局部自相关函数,因而在接收端较容易识别[2]。

数字复接系统分为3个模块:分频器,复接器及分接器。Altera的EPM570T100C5N芯片系统时钟是16.384 MHz,而复接器及分接器使用的频率是512 kHz和64 kHz,首先要进行分频。复接模块输入7路数据信号和1路同步信号,复接成64 bit的帧数据,并以512 kHz频率输出。分接模块输入512 kHz频率的64 bit的帧数据,并分解成7路数据信号。

2 多路数字信号复接器设计与仿真

复接器设计方案如下,首先对7路串行数字信号按字节复接,然后将数据缓存在2个64 bit的FIFO中,并采用乒乓操作实现对数据的缓冲。最后通过发送模块将数据复接为64 bit的帧数据,其中帧同步码为“10011011”。复接器包括3个模块:多路数字信号接收模块、数据缓存模块以及帧数据发送模块。

2.1 多路数字信号接收模块

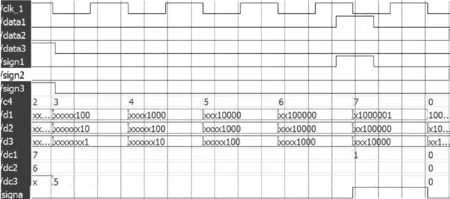

模块流程分为3步,首先识别数据的标志位sign,当接收到有效数据时,计数器便开始计数;并且不断采集数据,当采集完8 bit信号之后;发送一个控制信号使得下一个模块可以开始工作。接收模块仿真图如图1所示。

图1 多路数字信号接收模块仿真图

模块的输入信号:64 kHz(clk_1)的时钟频率;7路数据输入data n;7路数据的标志位输入sign n。

模块的输出信号:各支路接收的8 bit移位数据dn,如:第一支路的8 bit移位数据为d1;各支路实际数据的开始标识dcn,如:第一支路的实际数据的开始标识为dc1;还有7个标识符,用来标识各自支路在这一次成帧过程中是否有实际数据传入fn;若移位寄存器满8 bit,则通过控制信号signa通知数据缓存模块准备开始缓存数据。

2.2 数据缓存模块

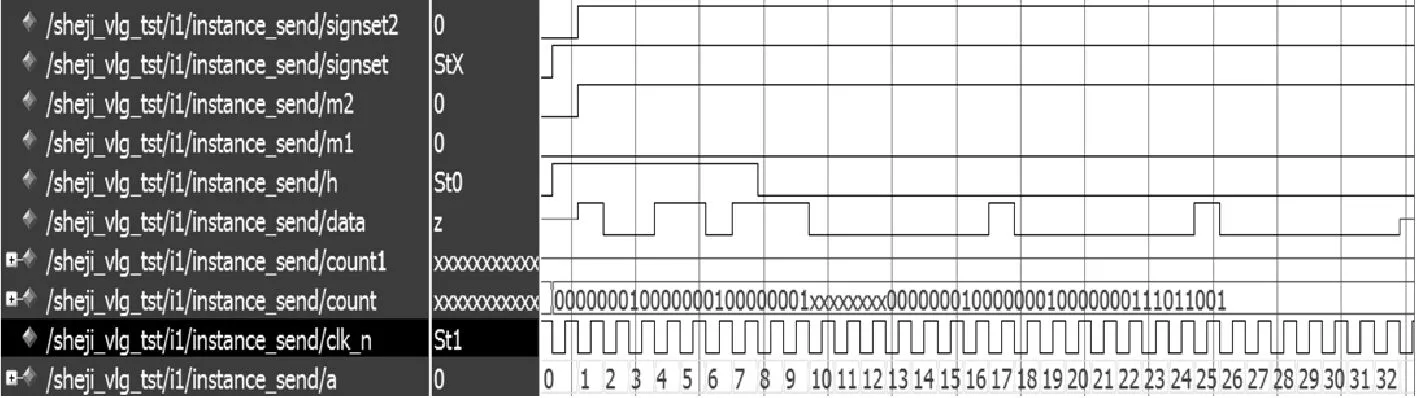

模块采用乒乓操作[7-9],当前模块的控制信号到来的时候,初始化所有有效数据后。运用一个标志符号位,控制数据存储的目的地,并建立2个寄存器组用于交替存放并行数据,使之组成一帧。当一个缓冲池数据完成存储时,标志位翻转,并控制在下一次将数据输入另一个缓冲池,运行模块间的连接性,可以将之前存储完成的缓冲池的数据释放出去。数据缓存模块仿真图如图2所示。

图2 数据缓存模块仿真图

模块的输入信号为多路数字信号接收模块的输出。

模块的输出信号:控制信号signset;帧寄存器组count[63:0],count1[63:0]。

2.3 帧数据发送模块

模块接收来自数据缓存模块的数据,加入帧同步信号[13-15],并在512 kHz时钟驱动下,帧数据按照计数器的数值不断串行发送帧数据。帧数据发送模块仿真图如图3所示。

图3 帧数据发送模块仿真图

当signset==1时,count[63:0]为有效发送端,通过计数器与时钟,以此在data数据线上发送数据,反之,则为count1[63:0]为有效发送端。模块完成在512 kHz时钟驱动下的帧数据发送,这样8路数字信号复接成功。

2.4 复接器整体仿真

复接器整体仿真图如图4所示。

图4 复接器整体仿真图

复接器输入:CLK(16.384 MHz),rst复位,7支路信号sign1~7及数据data1~7,各支路的数据都为:10000000。复接器输出串行数据:10011011_10000000_10000000_10000000_10000000_10000000_10000000_10000000。

3 多路数字信号分接器设计与仿真

分接器设计方案如下;首先检测帧头;帧头检测成功后开始按字节接收帧数据,并分别将7路8 bit数据分别存储;最后在64 kHz的时钟频率下输出分接数据。分接器包括3个模块:帧同步模块、串转并缓存模块以及各支路数据发送模块。

3.1 帧同步模块

模块采用帧头为10011011的巴克码,通过有限状态机识别帧头,检测完毕后通过帧标志frame_flag标识。实现帧同步方法是在发送端预先规定的时隙插入一组特殊的雄武的帧同步码组;在接收端由帧同步检测电路检测码组以保证收发同步[10-12]。帧同步模块仿真图如图5所示。

图5 帧同步模块仿真图

模块的输入信号为输入时钟512 kHz、64 kHz、sda数据码流,sda为8路8 bit数据复接成一路512 kHz的帧数据。模块的输出信号为帧标志frame_flag。

3.2 串转并缓存模块

模块采取移位操作,将64 bit帧数据在512 kHz的时钟驱动下,按位接收各支路的8 bit数据,并通过slotn_flag区分不同支路的数据。模块主要通过移位实现串并转换。

3.3 各支路数据发送模块

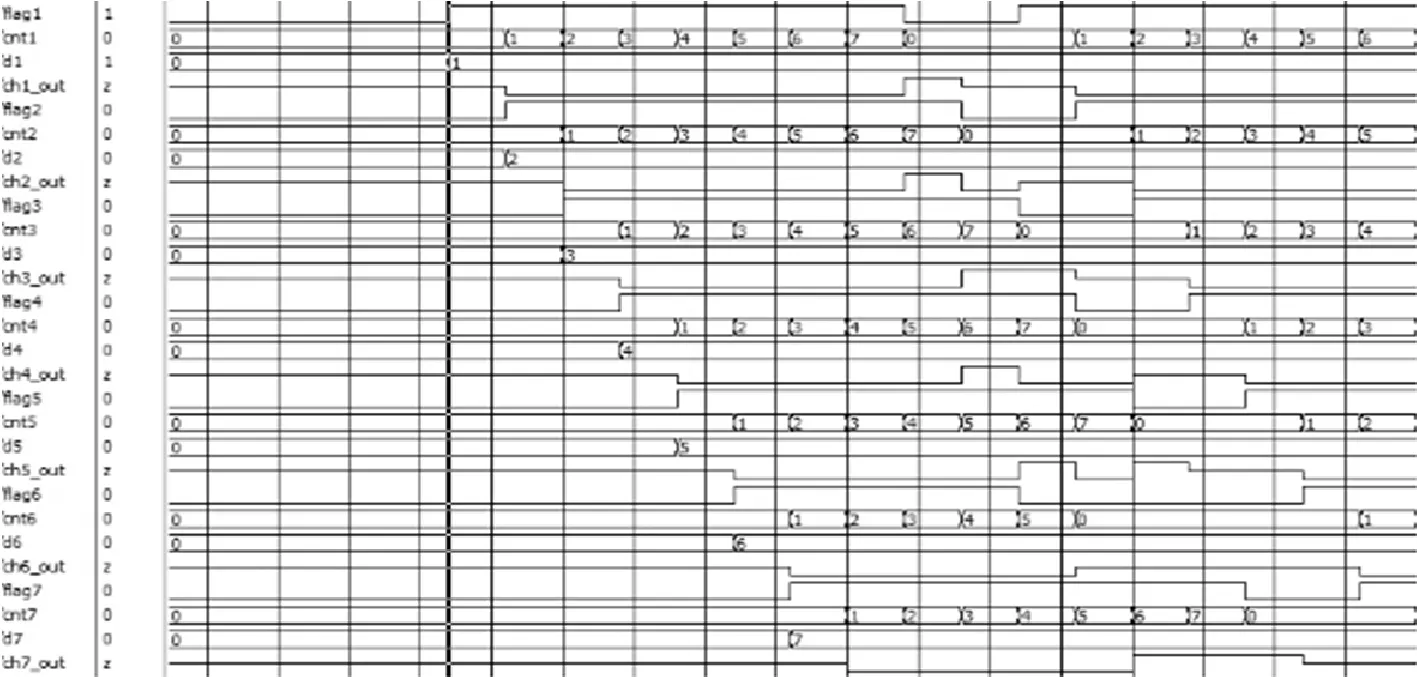

模块将串转并缓存模块输出的各支路的8 bit数据按位输出,通过标志位区分各路数据。各支路数据发送模块仿真图如图6所示。

图6 各支路数据发送模块仿真图

模块输入信号,flagn表示第n组数据正在传输;dn中存放第n组数据的数值。

模块输出信号:chn_out为第n路串行输出信号。

3.4 分接器整体仿真

将分接器的3个模块帧同步模块、串转并缓存模块以及各支路数据发送模块集成仿真,结果正确。分接器整体仿真图如图7所示。

图7 分接器整体仿真图

分接器输入sda输入的8路数据为10011011_00000001_00000010_00000011_00000100_00000101_00000110_00000111。从仿真结果看分接器输出的7路数据正确。

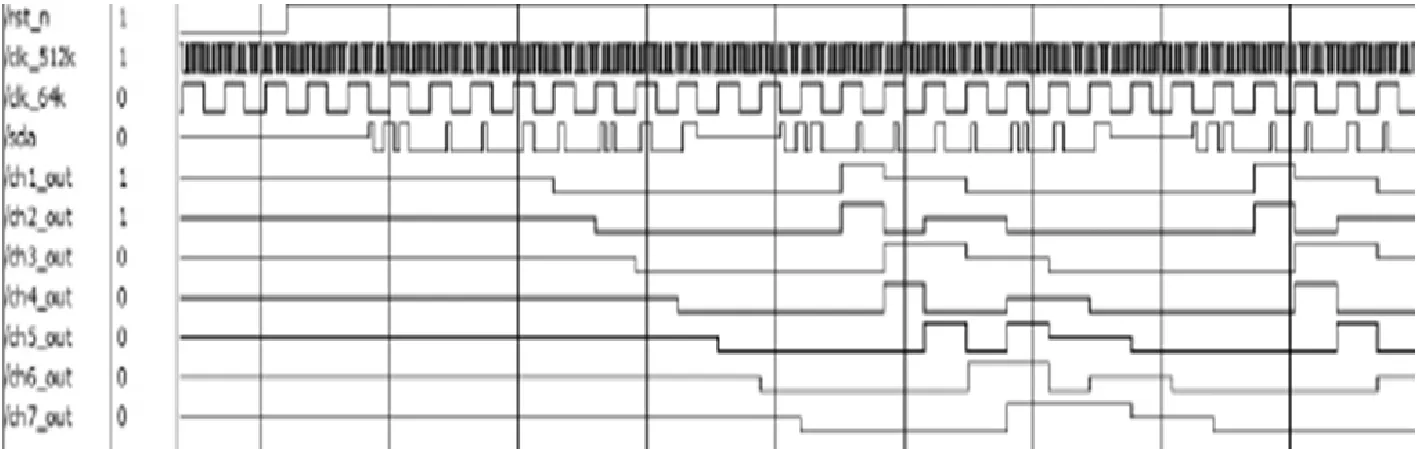

4 多路数字信号复分接器硬件实现

设计使用Altera的EPM570T100C5N芯片,在QuartusII11.0开发平台上使用Verilog HDL对各模块设计仿真。下载到芯片后,分别输出7路数字信号,通过示波器观察复接信号如图8所示,复接后的信号为10011011_10010010_01110010_00111001_10101011_00010000_01010100_10001101。

图8 复分接器示波器采集图

5 结束语

本文给出了8路复分接器系统切实可行的方案。复接器按位采样7路数字信号,且每路信号按字节缓存,并采用乒乓操作解决低速数据采集高速输出的数据丢失问题。分接器采用巴克码检测帧头,通过串行数据采样并行缓存再串行输出,成功恢复了采样7路数字信号。本系统各模块均在QuartusII 11.0中得到了仿真验证,并下载到Altera的EPM570T100C5N芯片得了验证。本系统稳定可行,可应用于多路数字信号通信的通信实验教学。

[1] 张应中,张德民.数字通信工程[M].北京:人民邮电出版社,1996.

[2] 段吉海,黄智伟.基于CPLD/FPGA的数字通信建模与设计[M].北京:电子工业出版社,2004.

[3] 王兰勋,张锁良.一种帧同步码检测方案及实现[J].河北大学学报:自然科学版,2004,24(2):180-183.

[4] 宋学瑞,蔡子裕,段青青.基于FPGA的同步数字复接系统设计与实现[J].计算机测量与控制,2008,16(8):1174-1176.

[5] 曲昱,曹辉,段鹏.基于FPGA的帧同步数字复接系统设计[J].信息安全与通信,2007(3):43-45.

[6] 王志,石江宏,周剑扬,等.同步数字复接的设计及其FPGA实现[J].电子技术应用,2005,31(4):77-80.

[7] 龙光利.巴克码识别器的设计与FPGA的实现[J].科技广场,2006(4):110-112.

[8] 魏芳,刘志军,马克杰.基于Verilog HDL的异步FIFO设计与实现[J].电子技术应用,2006(7):97-99.

[9] 张德,马淑芬,李海,等.专用异步串行通信电路的FPGA实现[J].微计算机信息,2005,21(3):152-153.

[10] 赵怡,但涛.基于FPGA的多路数字信号复接系统设计与实现[J].电子科技,2013,26(12):37-39.

[11] 郝建强.八路异步数据统计复接器设计[J].军事通信技术,2001, 40(1):72-74.

[12] 谢润华,黄佩伟.多速率码流同步复接方案设计与实现[J].通信技术,2001(5):20-22.

[13] 张景悦,王明磊,王莹.基于FPGA 的数字复接系统帧同步器设计与实现[J].国外电子元器件,2005(5):4-6.

[14] 管立新,沈保锁,柏劲松.帧同步系统的FPGA设计[J].微计算机信息,2006,22(26):177-178.

[15] 吴玉成,许太火,王黎明.帧同步电路的设计[J].现代电子技术,2003(4):69-71.

Multichannel Digital Signal Multiplexer/de-multiplexer Technology and Implementation Based on CPLD

ZENG Shuting,JI Xiaoming,XU Huangtao

(Jinling Institute,Nanjing University,Nanjing 210000,China)

Digital multiplex and de-multiplexing is an important technique in digital communication. In order to improve channel utilization and accuracy of the digital communication system.This paper introduces the 8 road digital multiplexer and de-multiplexer system design scheme. It mainly uses the ping-pong operation solve the problem of low speed data acquisition high speed output data loss. And based on software QuartusII 11.0 completed the multiplexer and de-multiplexer system design and simulation,and finally in Altera EPM570T100C5N chip was tested.The design is stable and flexible.The experimental results show that the design can be applied to multi-channel digital signal communication in communication experiment teaching.

multichannel digital signal;multiplexer;de-multiplexer;CPLD

2016- 09- 18

曾舒婷(1986-),女,讲师。研究方向:片上系统,嵌入式。

10.16180/j.cnki.issn1007-7820.2017.08.041

TN911.72

A

1007-7820(2017)08-150-03