32通道高速一体化测时仪研制

2017-07-18王广军

吴 镝,王广军,周 青

(1.成都胜英测控技术有限公司,四川 成都 610051;2.中国工程物理研究院流体物理研究所,四川 绵阳 621900)

32通道高速一体化测时仪研制

吴 镝1,王广军2,周 青1

(1.成都胜英测控技术有限公司,四川 成都 610051;2.中国工程物理研究院流体物理研究所,四川 绵阳 621900)

基于分布式-嵌入式技术,研制一种集成激励源、测量一体化全数字测时仪器,在信号检测中采用测量回路电流的方法,有效地解决测量过程中的多种干扰问题。该测时仪器将激励源、信号处理、记录、数据传输等功能部件完全集成在一台仪器中,较好地保证信号完整性和系统的方便易用性能,实现32个完全隔离的测试通道、测时范围100ns~2s、分辨力3.3ns、不确定度优于±7ns的指标,为爆炸外场试验中实现信号抗干扰,增强信号完整性、可信度,缩短测试准备时间等提供有效的技术支撑。

测时仪;分布式-嵌入式系统;激励-测量一体化;爆轰电离;通断靶

0 引 言

大型战斗部和巨型火炮试验中,常用通断靶来测量弹丸或破片的速度[1-3];在爆轰测试中,也常用放置系列电探针的方法来测量其电离等离子体的导通时间,从而获得爆轰速度[4-6]。通断靶或电探针均是无源装置,需要额外的激励源对其进行激励,以产生电信号。在这些外场试验中,掩体距离测量靶位大都在200~400m位置,多点测量时激励源需要埋设大量相应长度的测试线缆,不仅布线耗时费力,且过长的电缆会引入较强的干扰,导致测量的精度很难保证,成为能否实现准确测时的主要障碍。电缆引入的干扰信号主要来自两方面:1)通断靶或电探针的天线效应、分布参数效应,传输线的长线效应等;2)来自由于各通道间的电压、电流相互影响的通道串扰[7]。目前采取的多种消除干扰的方法,如硬件设计中的抗干扰措施、滤波,软件后处理中的模式识别等,处理结果都不够理想。本文针对上述问题,采用检测通断靶或电探针电流信号,提高被测信号的信噪比;通过独立隔离升压技术实现了通道间相互完全隔离;提高采样速率到300MS/s,实现高精度测时。将激励源、信号采集、数据通信、系统电源等集成为一体可以有效缩短埋设测量电缆的长度,以尽量降低干扰的影响。

1 设计原理

采用通断靶或电探针测试脉冲时间的原理是弹丸触靶/爆轰产生电离体时使其导通,然后用仪器获取导通脉冲的时间信息。

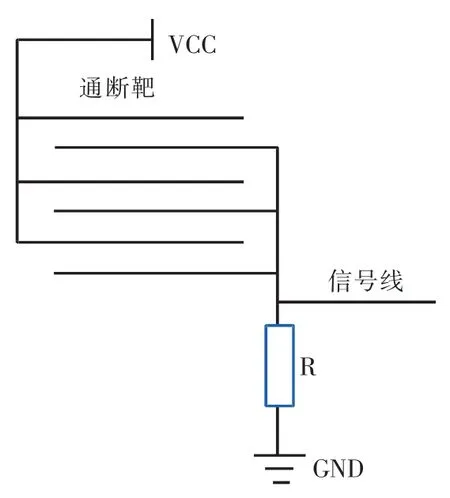

1.1 信号取样方式比较

在传统的信号取样方法中,一般采取在取样电阻上采集其两端电压的方法,如图1所示。在本文设计中,采取了对通断靶中电流进行取样的方法,如图2所示。图2中虚线右侧为在仪器内部的电路,其中R为限流电阻,保护高速光耦。

图1 传统信号取样方法

图2 本文设计的信号取样方法

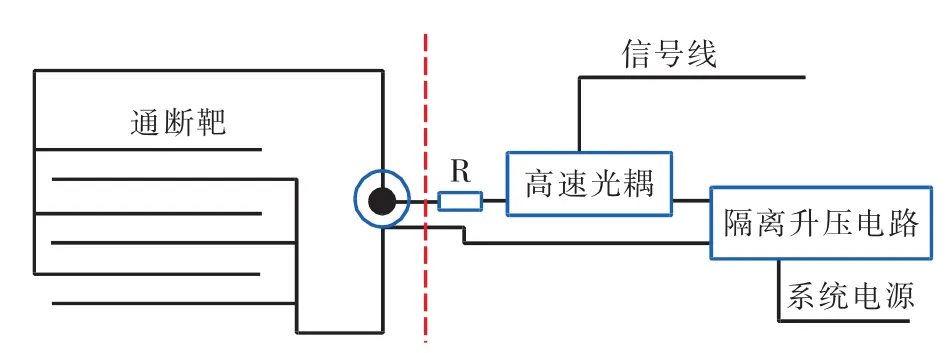

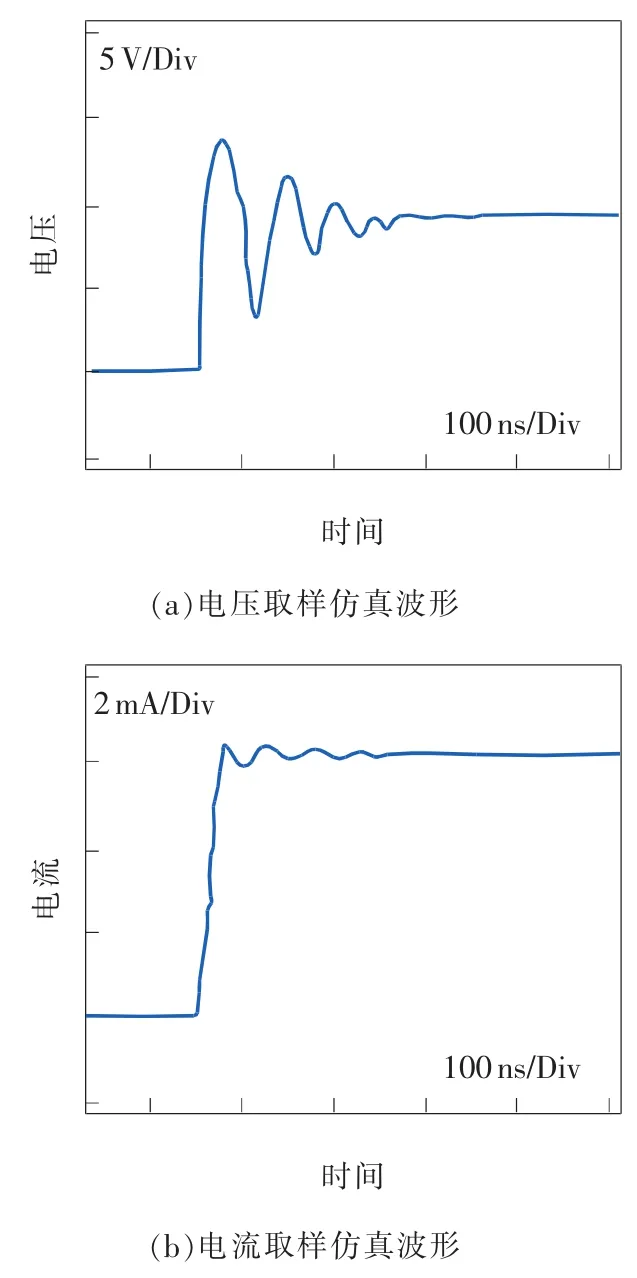

网靶的两种电路模型如图3所示。考虑分布参数电路模型下电压取样与电流取样的比较如图4所示。

图3 网靶和弹丸的电路模型

图4 分布参数电路模型下电压取样与电流取样的比较

可以直观地看到,电流取样的波形明显比电压取样的波形波动幅度小且收敛更快。从网靶到测时仪这段电缆的信号传输而言,叠加在电流信号上的噪声纹波比叠加在电压信号的噪声纹波明显降低,有效地提高了信噪比,从而在抗干扰能力上具有优势,这与传感器中广泛采用的4~20mA电流环的方法原理一致[8-9]。

由于多个网靶的物理结构、尺寸基本相同,因而其电磁共振引起的干扰即天线效应不可忽视。对于网靶而言,其结构在算其辐射强度时可等效为环形天线,辐射强度计算公式为

式中:E——电场强度,V/m;

f——电流频率,MHz;

S——环天线面积,m2;

I——电流强度,A;

r——发射与接收点之间的距离,m。

在电压取样方法中,为提高有效信号识别度,往往在网靶两端施加较高的电压(如150V),而取样电阻一般取得较小(50~1000Ω,通常采用 50Ω),所以弹丸触靶时的环路电流在数百毫安培乃至数安培的数量级。

而在电流取样的方法中,高速光耦的导通电流仅需数毫安培。由此可以得出结论,在不改变其他因素的情况下,根据式(1),两种信号取样方式产生的辐射干扰电场差异可达数十倍乃至百倍以上,即30~40dB。

综合上述两种信号取样方式的比较,在分布参数影响、电缆传输的长线效应、天线效应等方面,电流取样都比电压取样方式有明显的优势。

1.2 多通道间的隔离设计与实现

在爆炸外场试验中,经常需要测量爆心不同距离处的信号,测量多个测点的数据,所以多个测试通道的设计是十分必要的。多通道设计的关键是多通道的实现与通道之间的隔离。

通道间的串扰信号主要通过激励源与信号采集模块传播,为了实现隔离多通道的集成设计,达到抑制通道间串扰的目的,必须将各通道激励源之间、信号采集电路之间完全隔离。

在隔离激励源设计中,本方案采取的是独立隔离升压的方法,每一通道采用一个彼此隔离的激励源,一方面实现通道间的隔离,另一方面实现每一通道与本机电源的隔离。采用DC/DC芯片将系统直流电源变为开关脉冲,经隔离变压器和整流、滤波电路及稳压电路提供激励。激励电压为10V,电流驱动能力大于20mA。DC/DC采用了LTC公司的LT8300芯片,具有独特的隔离稳压功能,输出纹波小于10mV。

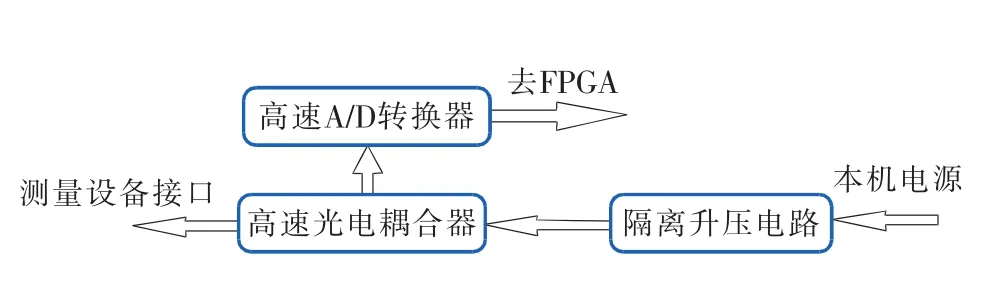

在信号隔离处理中,采用高速光电耦合器将检测到的网靶通断电流脉冲信号隔离耦合至高速A/D转换器转换为数字信号。经过这样的处理,实现了各通道的网靶通断脉冲信号在电气上完全隔离,这样可以将转换后的各数字信号送至同一个FPGA中做嵌入式算法处理。单一通道的隔离激励-信号检测模块示意图见图5。

通过上述两方面的设计处理,实现了各通道间的完全隔离。

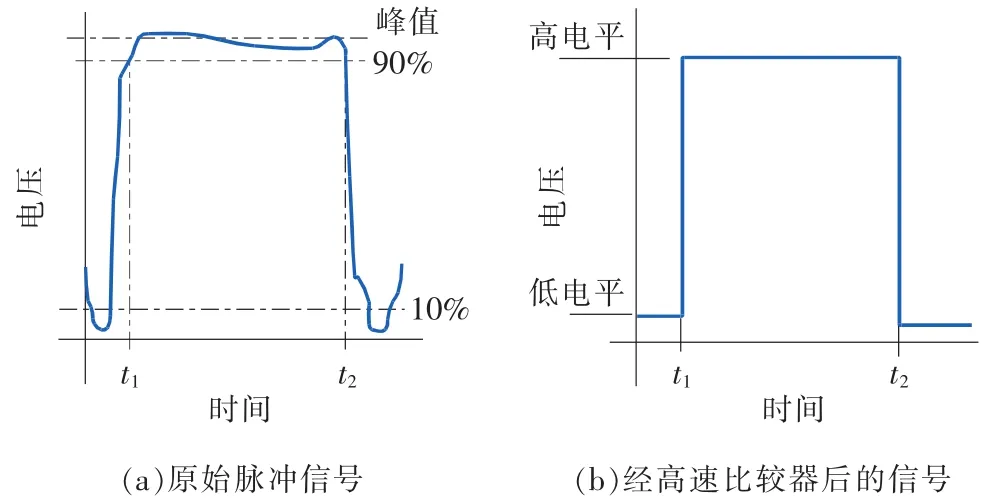

转换后的数字信号在FPGA中用嵌入式算法处理:计算提取上升、下降沿,然后计算出脉冲信息,如图6所示。这些算法在FPGA中实时处理,处理后的脉冲信息存入DDR RAM中[10-12]。

图5 单一通道的隔离激励-信号检测模块示意图

图6 脉冲波形及脉冲信息提取

1.3 电源管理

在集成仪器设计中,一个突出的重点和难点是电源管理。因为在系统电路中,存在多组电源轨:MCU、FPGA、存储器、TCP/IP模块、激励——测量模块等,它们的工作电压在1.2~10 V不等;此外,本机需驱动32路隔离升压电路,开关机过程中系统上电、掉电的瞬态电流变化很大,可达数十安培[13]。

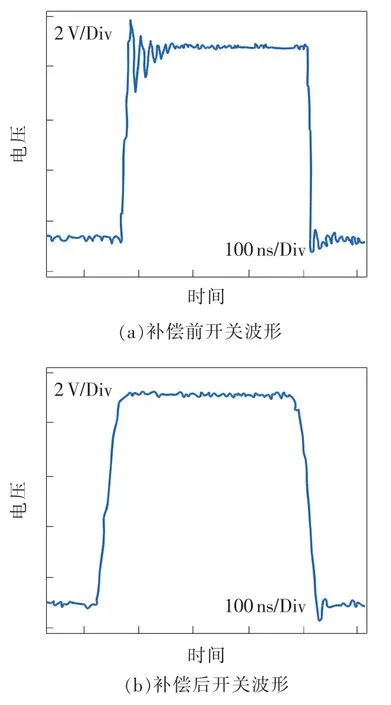

针对开关机的瞬态过程,用上电顺序管理电路来管理整机的上电过程,使各模块顺序上电,有效地降低了上电瞬态电流,将其降至3A左右,降低了上电过程对元器件的冲击,提高了仪器的MTBF(平均无故障时间)。在掉电时,其掉电顺序与上电时相反。针对本仪器中的多组电源轨,大量使用DC-DC技术。DC-DC技术带来的问题是噪声较大,易对精密测量电路带来影响。对此采用开关频率达2MHz的开关电源IC,同时对其开关电路进行补偿,消除开关电路的寄生震荡从而去除开关波形的尖峰与纹波,如图7所示,降低了其开关信号的频谱宽度,从而降低其噪声。DC-DC电路的噪声从平均50mVp-p降至10mVp-p左右,有效地抑制了电源干扰。此外,对敏感区域加装铁磁屏蔽罩,进一步改善其抗干扰能力。

1.4 高采样频率的设计

为实现高速、高精度的脉冲时间测量,采用FPGA自身的PLL锁相环,对石英晶体的40MHz时钟倍频,在FPGA内部产生300MHz的时钟,以该时钟对脉冲信息进行判读。将设计计时的时钟频率从目前业界多采用10MS/s以下的采样频率提高到300MS/s。

在300 MHz时钟下工作的电路要求较高,采用了4层印刷电路板,BGA封装的FPGA、DDR RAM,同时PCB设计时严格进行时序、信号完整性仿真验证,实现了电路的稳定性工作。

图7 DC/DC补偿前后开关波形比较

2 系统构成

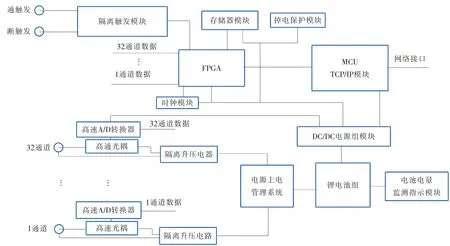

系统由激励——信号检测模块、FPGA——存储器模块、MCU——网络通信模块、电源管理模块、隔离触发模块等构成,辅之以上位机软件,即可方便地实现远距离测时、测速。基于这一系统,研制了VIDRI 32通道高速一体化测时仪,系统构成见图8。

系统的数据通信通过MCU——网络通信模块来实现。MCU——网络通信模块是本仪器与上位机的接口,实现了基于TCP/IP的百兆以太网通信接口。其带来的技术优势明显:传输距离长(无中继时可达100m,可用中继或光纤扩展通信距离)、可多台设备方便地组网、可接入广域网或将测量数据上传到云端等;另外,外场实验中,可将本仪器就近放置在测试设备附近,使模拟小信号的传输距离最短,从而有效地降低信号干扰,提高测量的质量。

此外,针对一些爆炸现场难于布线或通信网线易被炸断的特点,设计了“黑匣子”功能,当这个功能开启时,仪器可以脱离网络进行采集,采集完成后再将仪器收回,联网读取其中的数据。

图8 系统构成示意图

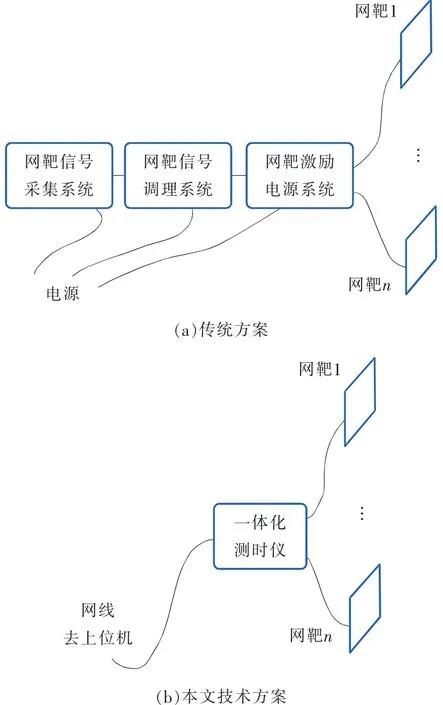

图9 是传统靶网测试方案与本文技术方案的对比示意图。配套的上位机软件对仪器采集到的数据进行解析、显示和存储,并对原始数据进行计算、分析和处理,得到每一路通断靶相对于触发信号的导通时间。该软件显示的数据有两种:1)表格形式的各通道靶脉冲个数、到达时间;2)可任意选择的8个通道脉冲波形显示。软件还可以对图形进行局部放大,以观察波形的细节,同时提供双光标操作,可以手动精确地测量图中的时间间隔。

图9 技术方案对比示意图

3 误差分析

对于测时结果的误差,主要来源于FPGA计时误差和模拟通道延时误差。

1)FPGA计时误差。由于系统采用高精度的晶体震荡器作为时钟源,而晶体震荡器的相对误差小于10-7,所以计时误差主要来源于晶体震荡器的工作频率,即计时的最小时间间隔。本系统中,采用40MHz的石英晶体,经FPGA的PLL将其倍频到300 MHz作为主时钟,其计时的最小间隔为3.3ns,FPGA计时误差以3.3ns计。

2)模拟通道延时误差。本系统中,通断信号经高速光电耦合器进入高速模拟比较器,所以除开线缆带来的时延,主要的模拟通道延时来自高速光电耦合器和高速模拟比较器。由于采用的是信号带宽不小于50 MHz的高速光电耦合器,所以模拟通道的延时可以估计为带宽的倒数,即20ns左右。高速模拟比较器的群延时正是其带宽的倒数,为3ns。

计时仪真正关心的是各通道脉冲信号之间的时间差,而每个通道都是经过相同设计的电子线路,所不同的仅是器件之间的差异。所以在计算脉冲宽度时,模拟通道的延时是被抵消掉的(同一个通道,同样的器件),而测量不同通道之间的脉冲时间差时,没有抵消完的是器件之间的差异,这个值远小于20ns,可以估计为最大3ns。

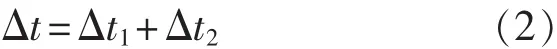

系统计时误差是上述两种误差之和:

式中:Δt1——FPGA计时误差;

Δt2——模拟通道延时误差。

可得系统计时误差为Δt≈6.3 ns。

4 爆轰测量实验

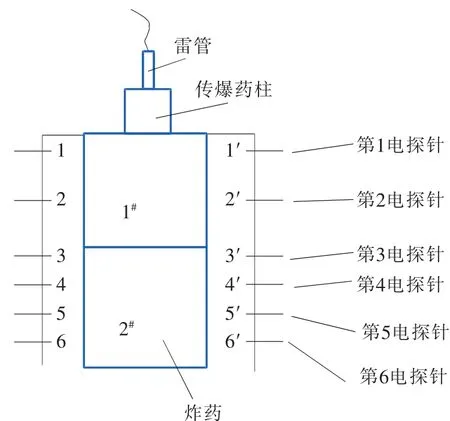

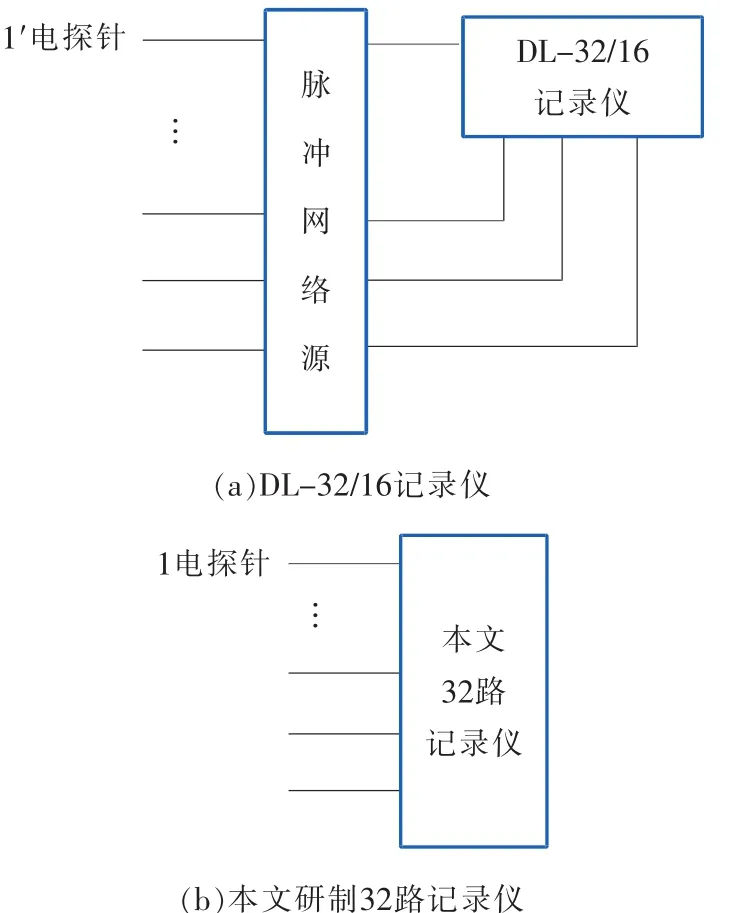

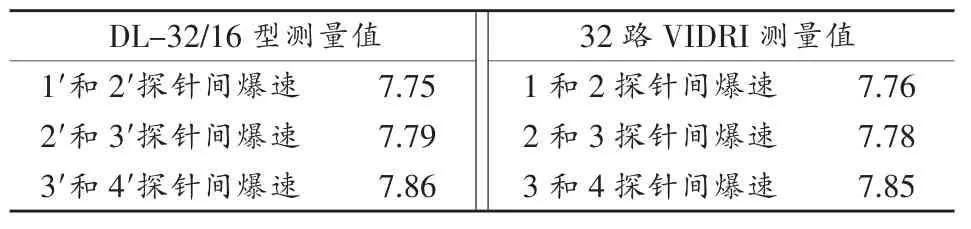

采用本文研制的VIDRI 32通道高速一体化测时仪与DL-32/16型多路时间间隔测量仪同时测量爆速进行实验对比[14]。试验装置如图10所示,仪器连接见图11。

图10 爆轰测速试验示意图

图11 爆轰测速试验仪器连接示意图

表1 爆速测试试验结果 mm/μs

DL-32/16型多路时间间隔测量仪32路的起始和停止脉冲由CM01型网络信号发生器产生,幅度为150V,前沿优于20ns。本文仪器的激励源由内部电路产生,幅度为10V,前沿优于20ns。实验结果见表1。

DL-32/16与本文仪器测量同一组信号的最大偏差为12ns,最小为1ns。测速偏差为0.01mm/μs,相对偏差≤0.13%,因此本文仪器与现有的精密测时仪测量结果一致。此外,仪器送检中国测试技术研究院,与高速示波器并测同一脉冲信息,得到的结果偏差≤10ns。

5 结束语

现场实验结果表明,本文提出的电流取样技术、通道隔离升压技术、高采样频率技术等有效提高了测时精度与速率,设计制作的32通道高速一体化测时仪,可准确、快捷地测量爆轰探针、靶网等的通断脉冲时间参数。对于在外场实验中使用的测试设备,一体化分布式-嵌入式技术的优点十分显著,微弱信号的就近数字化,仪器的低功耗、高集成度,直接带来高抗干扰能力和系统安装、操作的便利。

[1]杨桂红,王广军,龚晏青,等.梳状靶法研究爆轰驱动全预制破片的飞行规律[J].含能材料,2013(5):656-659.

[2]侯旷怡,何正文,张新伟.战斗部破片群初速、压力测试方法[J].四川兵工学报,2012,33(4):28-29.

[3]LU S T, YU A T, CHOU C.Electro-Optics target for position and speed measurement[J].IEEE Proceedings-A,1993,140(4):623-628.

[4]谢盘海,曾凡群,马冰.破片群初速的电探针测量法[J].爆炸与冲击,1994,14(4):363-368.

[5]王广军,龚晏青,汪斌.不同类型电探针在凝聚炸药爆速测量中的应用[C]∥全国爆炸力学实验技术学会会议论文集,2012.

[6]孙永强,何智,王珺.一种高精度爆速测量方法[J].含能材料,2012,20(3):329-332.

[7]张艳,孙闽红,覃章健.炮弹爆炸弹片平均飞行速率测试方法研究[J].微型机与应用,2004,23(11):44-46.

[8]吕津,韩震宇,汪炼.一种对20mA电流环的改进方法[J].中国测试技术,2003,29(2):37.

[9]武文斌,陈先.4~20 mA电流环串行通信接口抗干扰研究[J].现代电子技术,2014(12):116-118.

[10]潘松,黄继业.EDA技术使用教程-Verilog[M].4版.北京:科学出版社,2010:51-76.

[11]吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版,2010:42-60.

[12]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版,2003:70-83.

[13]曹志鹏.便携式仪表电池管理系统研究[D].杭州:杭州电子科技大学,2010.

[14]邵英斌,董金轩,曹科峰.DL-32/16型多路时间间隔测量仪及其应用[J].爆炸与冲击,1995,15(1):91-96.

(编辑:李刚)

Development of high speed integrated electrical chronometer with 32 channels

WU Di1,WANG Guangjun2,ZHOU Qing1

(1.Chengdu Scienic Measurement&Control technology Co.,Ltd.,Chengdu 610051,China;2.Institute of Fluid Physics,China Academy of Engineering Physics,Mianyang 621900,China)

Based on the distributed-embedded technology,an all-digital integrated signal excitation&detection electrical chronometer is developed,which effectively solves the problem of various disturbances in the measurement by measuring circuit current in signal detection.Integrating the functions including signal excitation,signal processing,signal recording and data transmission,the instrument ensures signal integrity and system availability,realizes 32 safely isolated test channels,measuring range of 100 ns-2 s,resolution of 3.3 ns,precision of ±7 ns and provides technical support for signal anti-interference,signal integrity and reliability in out-field explosion test and shortening of test preparation time.

electrical chronometer; distributed-embedded system; integrated signal excitation&detection;ionization in detonation;on-off target

A

1674-5124(2017)04-0078-05

10.11857/j.issn.1674-5124.2017.04.017

2016-09-10;

2016-11-18

吴 镝(1968-),男,四川成都市人,高级工程师,主要从事光电测试及高速模拟信号采集工作。