极小嵌入式系统中闪存转换层的设计与实现

2017-07-06任小平万瑞罡罗正华黄建刚

任小平, 万瑞罡, 罗正华, 黄建刚

(成都大学 信息科学与工程学院, 四川 成都 610106)

极小嵌入式系统中闪存转换层的设计与实现

任小平, 万瑞罡, 罗正华, 黄建刚

(成都大学 信息科学与工程学院, 四川 成都 610106)

为解决极小嵌入式系统中大数据量的存储问题,在对嵌入式设备广泛采用的NAND Flash的特点进行深入研究的基础上,设计了一种极小嵌入式设备NAND Flash存储系统的解决方案.说明了其系统分层结构和功能用途,详细阐述了闪存转换层中地址映射、纠错、坏块管理、磨损均衡及垃圾收集等算法的设计与实现,并在STM32微控制器上实现了NAND Flash的驱动和管理,验证了设计的可行性和有效性.

极小嵌入式系统;闪存转换;磨损均衡;地址映射;坏块管理

0 引 言

嵌入式系统主要由微控制器、存储设备、系统总线及I/O外设等结构组成[1].嵌入式系统的存储能力决定了系统的可定制性、模块化程度和可编程能力.NAND Flash因其存储容量大、相对成本低、对机械振动耐受程度高等特点,成为嵌入式设备的主要存储解决方案[1].随着智能互联的发展,在极小嵌入式系统中引入NAND Flash存储设备已经成为趋势.由于极小嵌入式系统的资源严重受限(RAM<20 KB,ROM<128 KB),因此,系统在引入NAND Flash时需要设计高效的管理算法,并提高NAND Flash的纠错能力,增强系统的可靠性和掉电恢复能力.

目前,NAND Flash的管理算法[2]分为2种:一种是设计专用的Flash文件系统,这样具有开销小、吞吐量大且对Flash友好的特点,但此种方式无法兼容广泛流行的传统磁盘文件系统,并且移植困难;另一种是通过设计NAND Flash和传统磁盘文件系统之间的转换层(flash translation layer,FTL)来解决上述专用Flash文件系统存在的问题.第2种方式虽然开销相对较大,但其可兼容磁盘文件系统,方便文件交流,并且对系统改动较小,移植方便,因而得到了广泛的认可和应用.本研究基于STM32F103C8T6微控制器和GD5F1GQ4UAYIG NAND Flash(规格为1 024块,每块64页,每页2 112 Byte)的硬件平台,设计了FTL层,实现了在极小嵌入式系统中NAND Flash存储系统的有效管理.

1 NAND Flash存储系统结构

NAND Flash存储系统总体框图如图1所示.硬件部分由NAND Flash器件及其辅助电路组成;软件部分分为用户层、文件系统层、FTL层与存储技术设备(memory technology device,MTD)层.

图1 存储系统框图

系统的用户层主要为用户提供文件访问服务.文件系统层由通用的文件系统实现(如FAT16/FAT32等),主要完成文件管理和为用户层提供服务接口.FTL层主要实现逻辑的数据读取与地址管理等功能,对上层提供类似磁盘的固定512 Byte的扇区式操作接口.另外,由于NAND Flash的存储原理和制造工艺,在设计FTL层时,还需要考虑坏块的检测、管理与维护、碎片回收、磨损均衡及异常恢复等情况[3].MTD层实现对Flash类设备的抽象化管理,对上层提供读、写、擦除及拷贝页等功能接口,对下层实现硬件的操作,是系统内最底层的驱动程序.

2 NAND Flash FTL的实现

从功能上划分,FTL层主要完成地址映射、纠错、坏块管理、磨损均衡及垃圾收集等.

2.1 地址映射

地址映射方式有多种,大体上可以分为3类:页映射、块映射及混合映射[4].综合考虑RAM开销与系统I/O开销,可以采用以下几种方法实现地址映射:使用树状页映射,如μ-FTL等;使用缓存映射表算法,如DFTL等;使用混合映射算法,如BAST、LAST、FAST、KAST及Super Block等[5].

在极小嵌入式系统中,受限于系统资源,选择BAST算法较为合适,同时,也可以通过对BAST算法进行针对化的优化,使其效率得到有效提高.

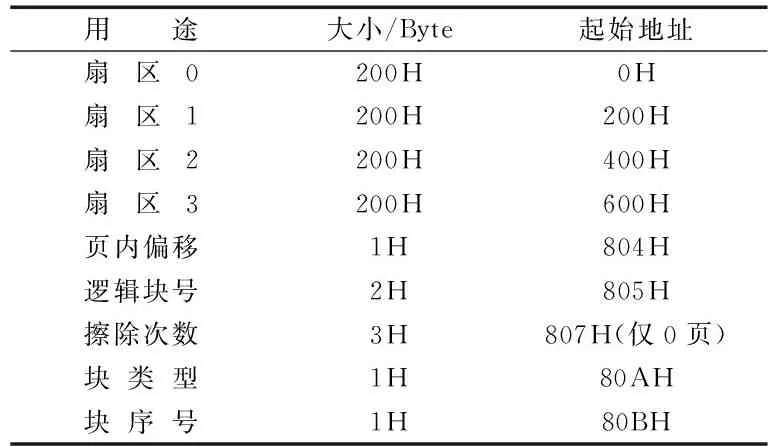

本设计中,保留5%的物理空间,以3%的数据块作为日志块(即32块).在初始无坏块的情况下,NAND Flash的用户空间容量为120 MB.块地址映射表将包含972个条目,一共2 KB.映射表数据结构如表1所示.

表1 映射表数据结构

单个日志块的映射表大小为64 Byte,则32个日志块的映射表大小为2 KB.采用二叉查找树(binary search tree,BST)构建查找表,地址映射部分仅占用4 KB内存,很好地平衡了内存开销和I/O调用,满足了设计要求.

2.2 纠错算法

NAND Flash由于工艺上的限制,位翻转的问题较NOR Flash和EEPROM严重.因此,设计FTL层时必须考虑纠错算法.本设计采用GD5F1GQ4UAYIG数据手册中建议的ECC码,通过使用芯片本身内置的Hamming ECC引擎来实现数据的纠错.其数据结构如表2所示.

表2 每页数据结构

2.3 坏块管理与保留块

在初始化NAND Flash时,由于NAND Flash厂商保证第0块为好块,因此FTL将选择第0块及后续完好的一块作为保留块,写入坏块表和擦写次数等信息,并在系统初始化时载入内存.每块占用2 bit,块状态定义如表3所示.

表3 块状态表

作为嵌入式系统,稳定性和可靠性应为系统的最基本要求.若系统在运行过程中出现坏块率大于阈值(2%)或平均擦除次数接近NAND Flash理论擦写总次数的5/6时,系统将自动进行写保护,并将出现的不稳定情况通知上层文件系统NAND Flash.

2.4 磨损均衡

GD5F1GQ4UAYIG NAND Flash为SLC结构,单块仅10 000次的擦写寿命,因此需要对其实现动态磨损均衡功能,避免对常用块的频繁擦写而出现坏块.常用的磨损均衡算法可参见文献[6]所述.与其他算法相比,HWL算法在内存较低的情况下拥有更好的磨损均衡效果,故本研究选择HWL算法来实现磨损均衡管理.HWL算法本身是不确定性算法,所以在实现该算法时,本研究通过使用在擦除块/重写块时统计每个块的擦除次数并写入该块的方法来统计Flash的预期寿命,进而实现磨损均衡管理.

2.5 垃圾回收算法

根据实际情况,本设计在实现垃圾回收时设定垃圾回收的阈值为系统日志块的1/2.当日志数量大于日志块容量的1/2时,系统监视进程将依据HWL算法的计算结果选取相对最“冷”的日志块与其数据块进行合并.当系统的日志块数量接近用完时,程序设计为在写扇区过程中自动进行日志块的整理.

被动垃圾回收操作由文件系统实现.文件系统在删除文件后调用FTL层的删除扇区命令,然后FTL层将计算扇区范围和删除扇区的开销,若满足含有1个或多个连续块的情况,则会启动垃圾回收算法.

2.6 读写操作

在读操作时,依次对块映射表和页映射表的内容进行判断.如果逻辑地址不存在于块映射表中,则返回空数据,否则对页映射表进行判断.如果逻辑基站不存于页映射表中,则返回块映射表内容,否则返回页映射表中对应内容.其流程图如图2所示.

图2 读操作流程图

在写操作时,由于应用层以512 Byte作为扇区的大小,而NAND Flash每页的容量为2 048 Byte,所以程序先将数据写入缓冲区,在下列情况之一发生时,执行写入操作:系统刷新周期;应用层要求回读;向其他扇区写数据,会破坏缓冲区原本数据内容.

具体在写操作时,先读取块映射表,若块映射表无此逻辑块的映射信息,则由HWL算法选择一个空块,在指定偏移处写入数据并修改映射表.若块映射表中有此逻辑块的映射信息,则判断此偏移页是否为空.如果逻辑地址偏移页为空,则写入数据,否则,判断此逻辑块的映射信息是否存在于页映射表中.如果逻辑块的映射信息存在于页映射表中,则判断日志块是否有空页,否则,以HWL算法分配空块,并新建页映射条目.若日志块的映射状态为完全连续的状态,则擦除数据块,并将原映射块标记为数据块.若出现日志块满的情况,则启动垃圾回收.其流程图如图3所示.

2.7 FTL接口实现

根据系统工作原理,本研究针对不同的功能,软件分模块实现为不同的函数.各函数接口名称和功能如表4所示.

表4 FTL函数定义及功能说明

图3 写操作流程图

3 MTD子系统的实现

MTD子系统实现对Flash的实际操作,具体函数定义及功能说明如表5所示.

表5 MTD函数定义及功能说明

4 测试与结果

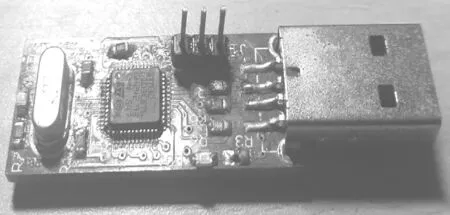

测试在STM32F103C8T6与GD5F1GQ4UAYIG组合的硬件平台上完成,设置通信速率为18 Mibit/s,以保证不影响NAND Flash的读写性能,其硬件实物如图4所示.

图4 硬件实物图

在硬件平台上运行整个软件系统,共占用8 KB SRAM与20 KB ROM(包括调试符号),实现了在极小嵌入式系统中大容量存储系统的高效访问.同时,对存储系统进行大块数据访问的情况下进行测试,其测试结果如图5所示.

图5 大块数据访问测试结果

由图5可知,随着Flash剩余存储容量的减少,对Flash访问速度并未受到影响,系统工作正常.

最后,对系统进行掉电测试,其测试条件为系统正在写入日志/数据或垃圾回收时,关断系统电源.测试结果表明,在循环进行1 000次后,系统可顺利回滚到上一状态,没有出现数据破坏或数据结构损坏的情况.

5 结 论

在资源极度受限的极小嵌入式系统中,本研究通过合理设计FTL层实现了大容量存储器的访问,为设备的智能互联提供了可能.后续的研究可进一步从主动垃圾回收和应用新的页/日志搜索树的方式等方面来进一步提升系统的吞吐量和实时性能,实现在极小嵌入式系统中以较低的资源消耗达到类似NAND Flash专用文件系统的效果.

[1]秦晓康,徐惠民.嵌入式设备NAND Flash存储系统的设计与实现[J].计算机工程与设计,2010,31(3):514-517.

[2]Park C,Cheon W,Kang J,et al.AreconfigurableFTL(flashtranslationlayer)architectureforNANDflash-basedapplications[J].ACM Trans Emb Comp Sys,2008,7(4):202-208.

[3]Chung T S,Park D J,Park S,et al.AsurveyofFlashTranslationLayer[J].J Syst Arch,2009,55(5-6):332-343.

[4]Gupta A,Kim Y,Urgaonkar B.DFTL:aflashtranslationlayeremployingdemand-basedselectivecachingofpage-leveladdressmappings[C]//Proceedingsofthe14thInternatioanlConferenceonArchitecturalSupportforProgrammingLanguagesandOperatingSystems.Washington,DC,USA:ACM Press,2009:229-240.

[5]Lee Y G,Jung D,Kang D,et al.μ-FTL:amemory-efficientflashtranslationlayersupportingmultiplemappinggranularities[C]//ACMInternationalConferenceonEmbeddedSoftware,EMSOFT2008.Atlanta,GA,USA:ACM Press,2008:21-30.

[6]Chang L P.Onefficientwearlevelingforlarge-scaleflash-memorystoragesystems[C]//SAC’07Proceedingsofthe2007ACMSymposiumonAppliedComputing.Seoul,Korea:ACM Press,2007:1126-1130.

Design and Implementation of Flash Translation Layer in Small Embedded System

RENXiaoping,WANRuigang,LUOZhenghua,HUANGJiangang

(School of Information Science and Engineering, Chengdu University, Chengdu 610106, China)

In order to meet the demands of intelligent interconnection development and to deal with the problems of big data storage in small embedded system,the paper,based on a thorough study of the features of the widely used NAND Flash in embedded device,designs a solution to deal with the problems in NAND flash storage system in small device system.The paper also introduces the hierarchical structure of the system and its functions,giving detailed account of the design and implementation of the address mapping,error correction,bad block management,wear leveling,and garbage collection in flash translation layer.Meanwhile,the driving and management of NAND Flash are realized on a STM32F103 board.Furthermore,the study verifies the efficiency and feasibility of this design.

small embedded system;flash translation layer;wear leveling;address mapping;bad block management

1004-5422(2017)02-0168-04

2017-05-02.

任小平(1990 — ), 男, 硕士, 从事嵌入式系统与无线自组织网络研究.

TP333

A