高速航电总线数据实时遥测技术研究

2017-05-24宫海波张振华

宫海波,徐 茜,张振华

(中国飞行试验研究院,西安 710089)

高速航电总线数据实时遥测技术研究

宫海波,徐 茜,张振华

(中国飞行试验研究院,西安 710089)

为了解决飞行试验中高速航电总线数据实时遥测的测试需求,研究了高速航电总线数据采集及实时遥测的测试技术;面对全新总线架构以及海量实时传输数据,传统的总线测试技术无法满足新的测试需求,设计了高速航电总线数据监听以及遥测传输的测试系统,成功将高速总线数据融合到网络数据采集技术及数字遥测技术中;实际的试验结果表明,该方案能够准确、有效地完成机载高速航电总线数据采集及实时遥测传输,该方案的成功应用,为今后相关的高速总线数据测试提供了重要的参考价值。

高速总线;飞行试验;实时监控;FPGA

0 引言

随着航空领域相关技术的发展,尤其是网络技术、计算机技术以及微电子技术的飞速发展,机载航电设备采用了大量新技术,设备的复杂程度以及信息化程度都发生了极大的变化,航空电子系统进一步向模块化和集成化方向发展[1-3],航空电子系统对总线网络的通信需求也越来越高,航空机载数据总线面临着挑战和变革[4],传统的ARINC429、1553B总线的传输速率已经远远不能满足航空电子系统通信的需求。新型高带宽航电数据总线的出现,解决了各类机载设备尤其是复杂电子设备、航电系统等复杂程度越来越高所带来的传输受限问题[5]。

国外先进机载设备采用了新一代高速航空总线,随着复杂航电设备的不断升级,新型总线速率可达到1553B总线传输速率的1000倍以上,新一代高速航空总线已成为未来航电统一网络的首选[6-8]。高速航电总线规模及拓扑结构异常复杂,传统RS422、ARINC429、1553B等总线测试技术根本无法满足新技术的发展,与传统数据帧固定,单一总线数据的测试环境相比,新型高速航电总线呈现出可变包的数据帧以及复杂的多种数据集合的网络测试环境[9]。

针对全新总线架构以及较高的实时总线数据速率的现状,如何完成高速航电总线数据的采集以及实时遥测,对机载测试来说是一项极具困难的挑战[10]。本文在航电总线理论研究的基础上,将高速航电总线数据融合到网络数据采集技术及数字遥测技术中,对高速航电总线数据实时遥测传输技术提出了一套解决方案。

1 测试系统组成及工作原理

机载设备的大量信息通过机载高速航电总线进行传输,其中部分关键数据信息是地面实时监控人员所关心的,所以需要实时解析用户关心的某些总线数据,将其变换为机载测试系统能接收的数据格式,由机载测试系统将机载高速航电总线数据与其它测试数据整合后,通过机载遥测传输设备发送到地面,进而完成测试参数监控需求。因此,机载高速航电总线测试系统必须实现如下功能,首先是建立正确的拓扑连接,保证在不影响飞机航电系统信息传输结构与特性的前提下,能够获取机载航电总线上的信息;其次是建立统一的测试系统时间协调机制,能够对采集的机载高速航电总线数据添加统一的测试系统时间标记,从而确保机载高速航电总线数据与其它测试参数的时间协调一致性。

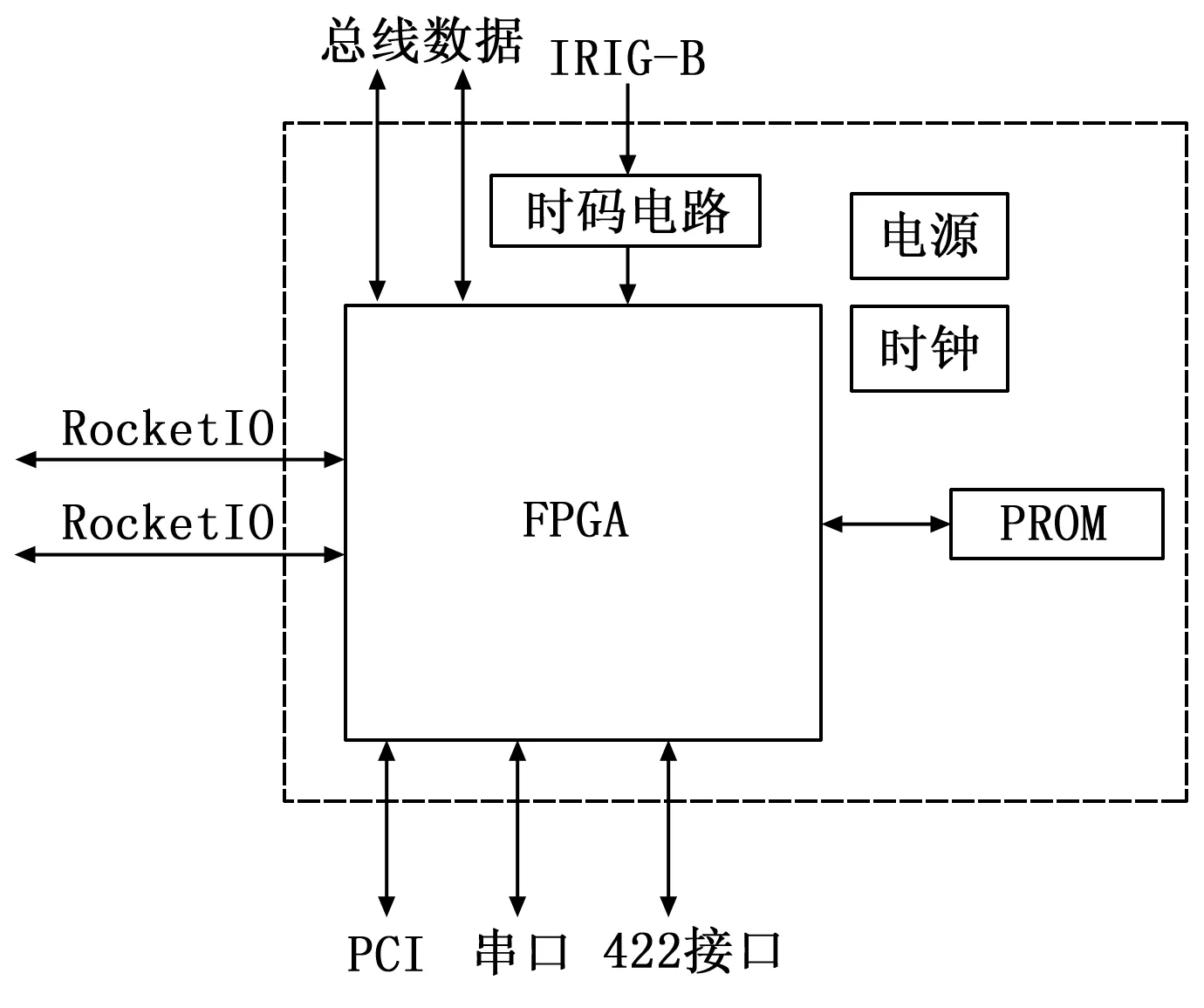

机载高速航电总线数据采集测试系统主要由电源模块、高速总线数据接收模块、B码接收模块、数据处理模块、主控制器模块、存储模块等组成,测试系统框图如图1所示。

图1 机载高速航电总线数据测试系统框图

电源模块将输入28 V电源转换成系统内部各模块的5 V直流供电;母板完成各个模块间以及对外接口的互连;机载高速航电总线数据接收模块主要完成网络数据采集、余度去除、数据过滤、时码信息解析和处理;数据处理模块完成数据格式转换和缓冲存储处理;主控制器模块负责完成系统配置加载、初始化、参数挑数、IENA格式数据打包以及通过以太网发送IENA数据的功能。

2 系统硬件设计

2.1 电源模块设计

电源模块将飞机上28 V电源转换成测试系统所需的二次电源,电源工作特性、电源品质和用电要求满足GJB181-86的相关要求,具有输出过压和短路保护功能、耐输入过压浪涌功能、耐输入尖峰浪涌功能和掉电保持功能。

电源模块原理框图如图2所示,由输入滤波、辅助电源、防过压浪涌电路、欠压储能电路、输出滤波、5 V功率模块等组成。

图2 电源模块原理框图

2.2 高速航电总线数据接收模块设计

高速总线数据接收模块主要由两个相同的模块组成,每个模块完成一路高速总线数据的采集工作。高速总线数据接收模块主要完成两路网络数据采集和过滤,解析时间信息,采集过滤之后,每路网络数据分为两路,其中一路数据通过PCI接口发送至主控制器模块进行处理,一路数据通过RocketIO接口发送至数据处理模块进行处理。

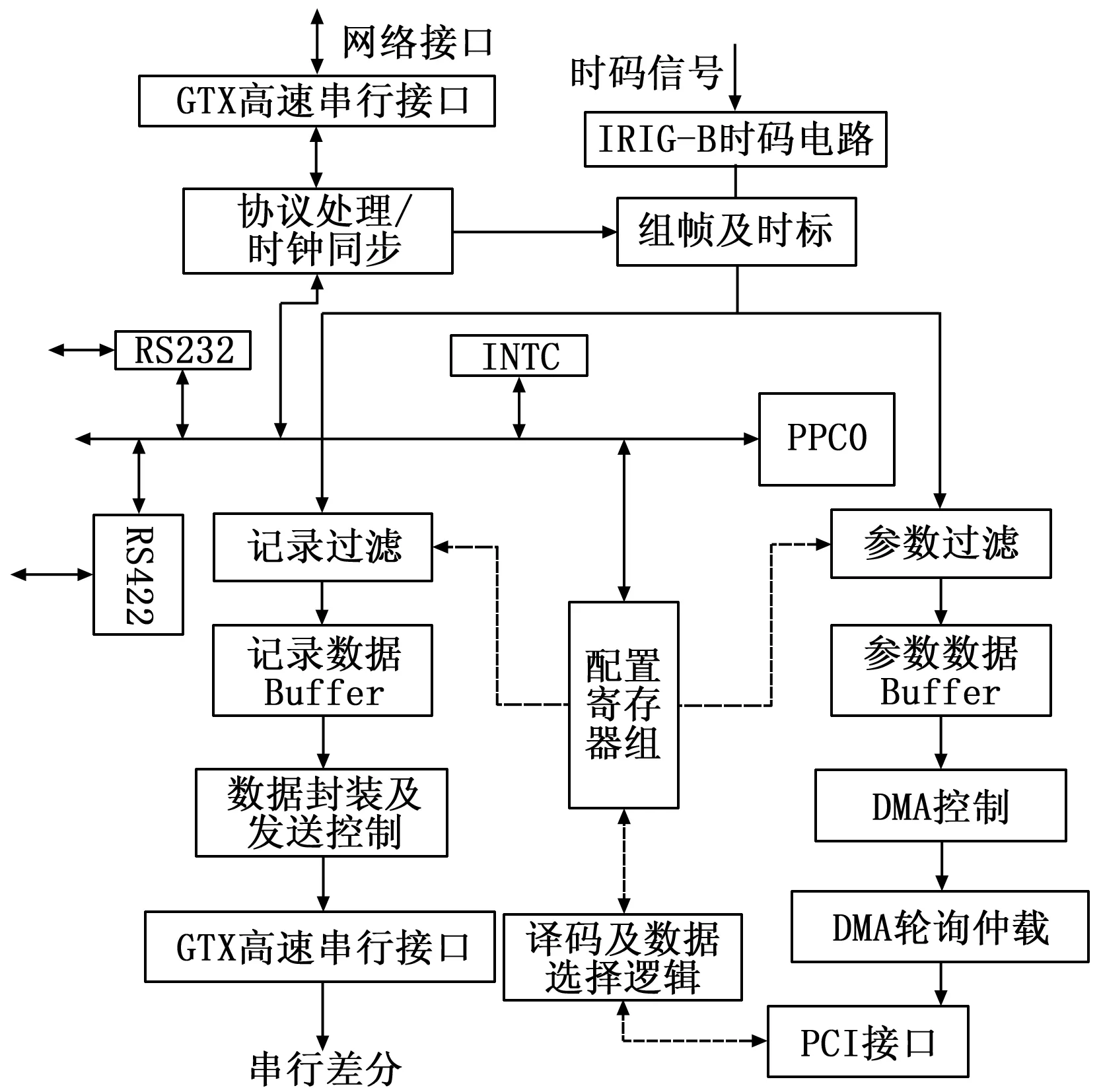

模块主要电路包括电源变换电路、复位电路、存储器电路、时间码元输入电路、调试串口、422接口电路等。高速总线数据接收模块系统结构如图3所示。

图3 高速总线数据接收模块原理框图

FPGA作为高速航电总线数据接收模块处理核心,主要实现高速航电总线数据的采集和过滤输出,包括总线网络接口、系统RTC授时、时钟同步原语解析、IRIG-B时码电路及本地RTC、数据帧组帧、时标及过滤、记录数据发送以及PCI接口等功能。系统设计中,数据记录、过滤电路以及2路总线接口互相独立,分别由PPC0和PPC1管理,2路使用同一个PCI主机接口。采集逻辑功能架构如图4所示。

图4 采集逻辑功能架构

2.3 数据处理模块设计

数据管理单元通过可编程控制逻辑器件实现处理器局部端总线的控制逻辑,通过FPGA实现数据的输入/输出和中断控制,通过2路 PCIe 4Lanes接口和数据接收单元进行交联,数据传输速率可达2.5 Gbps,并输出两路千兆以太网到数据输出单元,数据输出单元根据高速总线数据协议,对总线数据进行解析。

当数据管理单元将一帧数据写入FIFO后,通知协议解析单元,该单元将完整一帧数据读入到RAM,根据高速总线数据协议,首先对包进行分类,然后根据预先编程的设置进行过滤,过滤掉不需要的帧数据,针对所需要的数据帧进一步根据参数定义,从数据帧中取出被定义的数据。数据处理模块结构示意图如图5所示。

图5 数据处理模块结构示意图

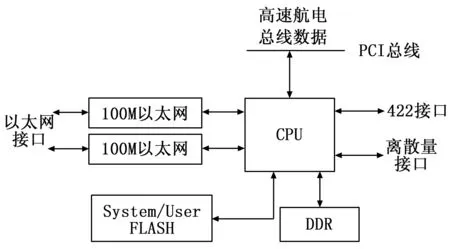

2.4 主控制器模块设计

机载高速总线网络系统主要由机载航空电子设备、设备连接端口及网络处理模块构成,飞行试验所需的总线消息传输至网络处理模块中的监控端口,根据测试任务需求,将海量网络数据中部分数据消息配置到测试监控端口。针对飞机上测试端口的高速海量网络数据,采用网络监控模块IP核,结合测试任务开发专用数据接收模块在不占用逻辑资源的情况下提供高速处理的通信接口,完成数据格式转换、解码、同步、数据重构后进行完整性检测和余度去除处理,最后将符合要求的数据帧通过高速DMA接口输出给数据管理单元。

高速航电总线关键参数的实时遥测监控部分,必须考虑与目前测试系统能够兼容,为了满足高速航电总线关键参数的实时遥测监控,数据解析完成后,根据事先准备好的配置文件,可从解析的数据中挑选关键参数,并且按照IENA标准将挑选的数据打包,进而将数据传给多功能数据采集系统。利用网络接收模块接收符合IENA标准的网络包,多功能数据采集系统将高速航电总线网络包数据融合到PCM流中,进而完成关键参数的实时遥测。

主控制器模块实现特征参数缓存打包和以太网发送,以及配置接口等功能。主控制器模块与高速航电总线数据接收模块之间接口为PCI,高速航电总线数据接收模块将收到的数据帧通过PCI接口送到主控制器模块的内存中,主控制器模块CPU从内存中读取数据并进行特征参数提取和数据打包处理,完成IENA打包后由以太网接口发送出去,主控制器模块功能如图6所示。

图6 主控制器模块功能图

3 技术关键点分析及解决途径

试飞测试数据处理中,采集的高速航电总线数据不是孤立的,它需要与试飞用传感器测量数据进行相关处理,所以需要建立这两条异步数据的时间协调,这是总线测试的技术关键之一。通过接收机载测试系统中的IRIG-B授时码,使高速航电总线采集系统内部建立与机载测试系统高度统一的时间。在每个数据帧到来时,该帧数据打上时间标记,这样就可以确保高速航电总线数据与试飞用传感器测量数据的时间协调。采用时间戳的多源时间同步解析技术,实现机载高速航电总线多源时统解析和时统标注,以及全局时钟以太网同步测试方法的应用,进行了时间精度分析,实现遥测实时监控的测试需求。

在采集高速海量航电总线数据的情况下,保证设备正常工作并为了减小数据的时延,可根据监控数据速率配置,选择固定缓冲区大小或是固定数据帧数来作为提交数据量的大小,完成数据挑选打包。

测试系统中时间码接收部分实现对机载时间码发生器输出的IRIG-B时间码进行解调,并产生与外部授时时间高精度同步的内部并行BCD时间,从而实现采集到的总线数据与机载测试系统的其它参数时间相协调,为了有效实现测试参数的时间一致性,网络数据包包含系统RTC时间和IRIG-B时间,最小单位100ns。由于机载网络数据源分布机身,并且不同消息源的信号周期不同,为了减小数据的时间延迟,尽量把来自同一消息的信号放到一个IENA包中,最好是相同类型或周期的信号在一个IENA包中。如果IENA包很大,数据经过采集、编包以及传输会产生比较大的时间延迟,甚至导致信息丢失。如果IENA包太小,势必需要增加网络包的数量,增加系统的处理负担,使得网络的传输效率降低。因此,在不超过系统最大传输数据容量的情况下,网络包长度与网络包数量自由设置。

4 实验验证及分析

该测试方案在实际的飞行试验中得到了应用,为了了解该测试方案工作的情况,验证测试系统工作稳定的同时验证机载高速航空总线实时遥测数据及记录数据的稳定性、正确性,选取试验数据的1553B总线参数做参考,某试验中以固定20帧的帧数来作为打包的数据量定义,选取机载高速航空总线与1553B总线中同一参数高度做比对,由图7试验数据可见,机载高速航空总线数据与1553B总线数据一致性很好,在机载高速航空总线总数据量330 Mbps的情况下,周期25 ms的总线数据时延是650 ns左右,整段试验记录数据不存在丢帧的问题,地面实时遥测数据接收显示正常,整个测试系统工作稳定。

图7 高度数据比较图

针对海量机载高速总线数据,利用PCIe实现机载网络交换机与主机之间的高速数据通信,在数据传输上采用流水线式结构和FIFO的数据缓冲机制,同时采用大规模可编程FPGA,利用其高速、纯硬件、可并行工作的特点解决了突发海量数据实时传输问题。对于协议复杂的机载高速航电总线数据,要在实时条件下实现数据解析,其难度相当大,采用“软件硬件化”设计思路,充分利用FPGA高速特性,根据机载高速航电总线上层协议,利用VHDL语言建立协议模型,将其固化到FPGA内部,从而实现纯硬件化高速解析上层协议。

5 结束语

本文论述了机载高速航电总线的数据采集及实时遥测技术,设计了相应的试飞测试系统,解决了传统测试方案无法满足机载高速航电总线数据采集技术的难题。该套机载高速航电总线试飞测试系统已成功应用于飞行试验中,完成了全新总线架构下海量实时数据的采集、记录以及实时遥测传输的问题。该方案的成功应用,为今后相关测试研究提供了重要的参考价值。

[1] 张 杰. 机载高速数据总线技术的应用研究[J]. 电子测量技术,2016,39(6):163-166

[2] 张英静,熊华钢,刘志丹. 可用于航空电子系统的时间触发以太网[J]. 电光与控制,2015,22(5):49-53.

[3] 曲 芳,王 剑,孙国强. 高速数据总线测试概述[J]. 计算机与数字工程,2010,38(9):101-104

[4] 田 泽,徐文龙,许 恒,等. FC光纤通道技术研究综述[J]. 电子技术应用,2016,42(9):143-146

[5] 苏连栋. 光纤通道在综合航电系统应用中的关键技术 [J].飞机设计,2007,27(4):66-70

[6] 沙永忠,冯巧宁,刘 明,等. 光纤通道航电总线数据采集器设计 [J].测控技术,2014,33(3):106-109

[7] 杨 哲,王 鹏,徐 茜. 基于RTR的遥测数据实时处理软件的设计与实现[J]. 计算机测量与控制,2016,24(1):165-167

[8] 冻伟东,鲜 峰,吕 晔. 实时遥测数据信源压缩技术[J]. 计算机测量与控制,2011,19(5):1120-1123

[9] 袁炳南,于 艳,张俊芳. 飞行试验多目标遥测监控及其技术实现[A]. 2008年航空试验测试技术论文集[C].2008.

[10] 贺思捷,刘大同,彭 宇. 遥测数据驱动的无人机飞行状态识别方法[J]. 仪器仪表学报,2016,37(9):2004-2013

Research on Real Time Telemetry of High Speed Avionics Bus Data

Gong Haibo, Xu Qian, Zhang Zhenhua

(Chinese Flight Test Establishment, Xi’an 710089,China)

In order to solve the test requirement of real-time data telemetry of high speed avionics bus in flight test, the test technology of high speed avionics bus data acquisition and real-time telemetry is studied. In the face of the new bus architecture and massive real-time data transmission, the traditional bus testing technology can not meet the new test requirements, the test system of data acquisition and telemetry transmission of high speed avionics bus is designed. The high speed bus data is fused to the network data acquisition technology and the digital telemetry technology. The test results show that this scheme can accurately and effectively complete the airborne avionics bus high-speed data acquisition and real-time telemetry transmission, the successful application of this project, provides an important reference value for the future high speed bus data related test.

high-speed bus; flight test; real time monitoring; FPGA

2017-02-15;

2017-03-13。

宫海波(1982-),男,陕西西安人,工程师,硕士研究生,主要从事机载测试技术方向的研究。

1671-4598(2017)05-0014-04DOI:10.16526/j.cnki.11-4762/tp

TB

B