双核SoC芯片扫描链测试设计与实现

2017-05-10刘广东石国帅徐浩然

刘广东,石国帅,徐浩然

(北京计算机技术及应用研究所,北京 100854)

双核SoC芯片扫描链测试设计与实现

刘广东,石国帅,徐浩然

(北京计算机技术及应用研究所,北京 100854)

针对芯片生产过程中可能引入短路和断路等制造缺陷的问题,实现了基于扫描链测试的双核SoC芯片可测性设计电路;根据双核SoC中DSP硬核、CPU软核特点采用不同的扫描链设计方案:利用DSP硬核中已有扫描链结构,将DSP测试端口复用到芯片顶层端口,在CPU软核和其它硬件逻辑中插入新的扫描链电路;扫描链测试支持固定型故障测试和时延相关故障测试;针对时延故障测试,设计了片上时钟控制电路,利用PLL输出高速时钟脉冲进行实速测试;采用自动测试向量生成工具产生测试向量,结果表明,芯片固定型故障的测试覆盖率可以达到97.6%,时延故障测试覆盖率可以达到84.9%,满足芯片测试覆盖率要求。

可测性设计;扫描链测试;双核;片上时钟控制

0 引言

在芯片制造过程中,各种随机因素及生产线自身缺陷都可能导致芯片制造故障,使芯片不能正常工作,故需要对生产出的芯片进行测试[1]。单个芯片上可以集成多个处理器核,内部IP越来越多,其时序结构也更加复杂,对芯片的测试难度大大增加。为了达到测试目标,必须采用可测性设计(DFT)技术,通过增加测试逻辑和测试引脚,解决芯片的有效和自动测试问题。可测性设计技术主要包括扫描链测试(Scan),存储器内建自测试(MBIST)和边界扫描测试(BSD)等[2]。可测性设计关系到芯片的测试成本及良率,需要以较短的测试时间和较低的测试成本来获得较高的测试覆盖率和测试质量[3]。在0.13 μm工艺和以下,与时序相关故障所占比例越来越大,而通常由测试机提供慢速时钟的测试无法覆盖时序相关的故障,由于这些原因,实速(at-speed)测试已成为一种必需的测试手段。

1 扫描链测试的基本原理

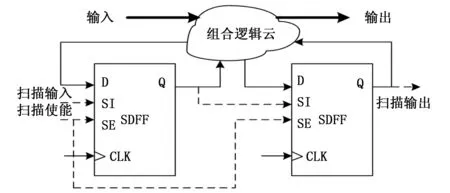

SoC芯片为一个大规模的时序电路,其电路可以通过组合网络和触发器的反馈建模,如图1所示。这些触发器的值代表电路的状态,但由于很难控制或观测触发器值,故难以直接对时序电路产生测试向量。扫描链测试技术就是把普通触发器修改为扫描触发器,并通过扫描输入端口将触发器串联成扫描链。根据是否将所有触发器替换成扫描触发器,扫描设计分为“全扫描设计”和“部分扫描设计”。扫描链测试向量通过扫描链测试输入管脚输入,对扫描触发器值进行控制,扫描测试结果通过芯片扫描输出管脚输出,可以观测扫描测试结果。通过扫描移位,扫描触发器值既是测试数据的输入,又可以作为测试响应的输出。扫描链测试分为扫描移位阶段、捕获阶段和扫描输出阶段,扫描移位阶段是将测试向量通过扫描触发器串行地输入扫描链,捕获阶段是通过触发器捕获组合逻辑输出的状态,扫描输出阶段是将捕获的组合逻辑输出值通过扫描链输出,通过比较扫描链输出与期望结果判断芯片内部是否出现故障。

图1 时序电路模型图

扫描链测试分为基于固定型故障的测试(stuck-at测试)和基于时延故障的测试(实速测试),两者的区别仅在于捕获阶段不同,stuck-at测试捕获阶段使用的时钟为慢速的扫描移位时钟,时钟频率通常为数十MHz,只需要一个时钟脉冲,而实速测试捕获阶段使用高速功能时钟脉冲,通常为数百兆赫兹甚至数吉赫兹,捕获阶段需要2个及以上捕获时钟脉冲。

2 扫描链设计方案

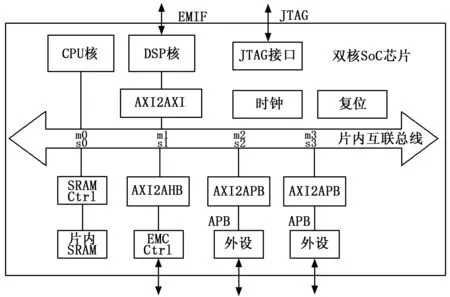

异构双核SoC芯片是一款系统级超大规模集成电路,芯片架构框图如图2所示。SoC芯片内部集成了CPU软核,DSP硬核、存储器、总线系统、数据处理和通信模块及多种IO接口,各模块通过片内互联总线通信。由于SoC芯片内部模块的类型及来源多种多样,需要采用不同的可测性设计方法。SoC芯片需采用的DFT测试方法包括:扫描链测试[5]、存储器内建自测试和边界扫描测试[6],本文主要针对扫描链测试进行研究。

图2 异构双核SoC架构框图

综合生成网表后即需要进行扫描链测试插入扫描链设计,由于双核SoC中的DSP采用的是硬核设计,硬核内部已经插入扫描链结构,扫描测试的端口也已经引出到硬核端口上,故不需要对DSP硬核进行专门的插扫描链设计,只需要将硬核的扫描端口通过pad复用或分配专用pad的方式引出到SoC的顶层端口上即可。对于CPU软核和硬件逻辑,采用扫描链插入工具采用自顶向下的方式插入扫描链。

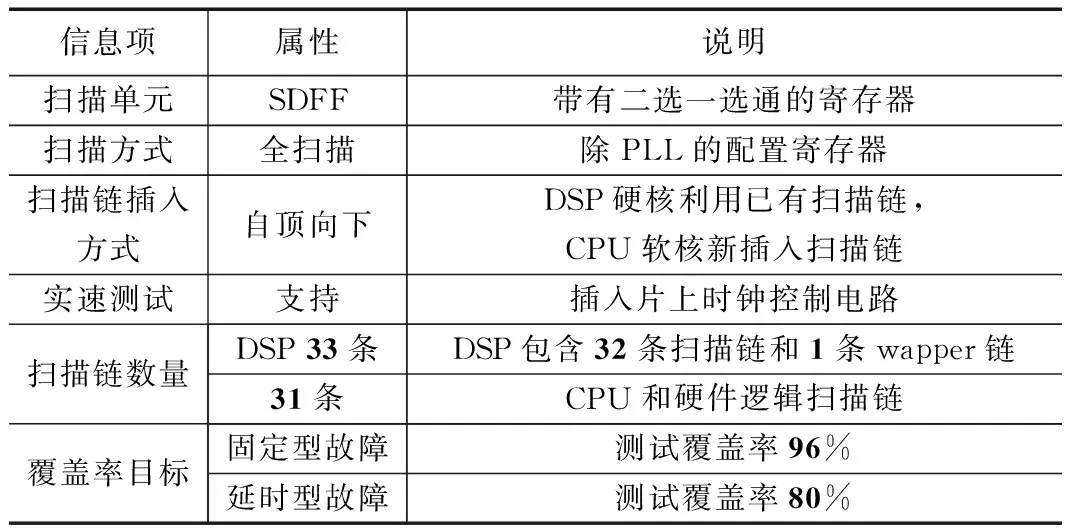

由于实速测试需要使用较高的测试时钟频率,而一般测试机提供的时钟无法达到要求的频率,使用可以提供高频时钟的测试机又往往成本昂贵,故需要设计一种专门的时钟结构电路,使实速测试不必由测试机提供高速时钟,而是使用芯片内部PLL输出的高速时钟。芯片可测性设计中采用一个专用片上时钟控制电路(OCC)解决实速测试的时钟问题。扫描链测试采用全扫描设计,合理划分可测性设计的控制端口和扫描链数目,通过扫描测试模式选择信号控制时钟和复位信号的可控性。同时,通过增加扫描寄存器,将内部不可控和不可观测的阴影逻辑修改为可控和可观测逻辑,增加内部逻辑的可控性和可观测性,可以提高扫描链测试的覆盖率。SoC芯片内部的高速时钟域包括CPU时钟,DSP时钟和AXI总线时钟,在每个时钟源处插入一个OCC控制电路可以实现全芯片的实速测试,SoC芯片扫描链设计信息和控制接口设计分别见表1和表2。

表1 扫描链设计信息表

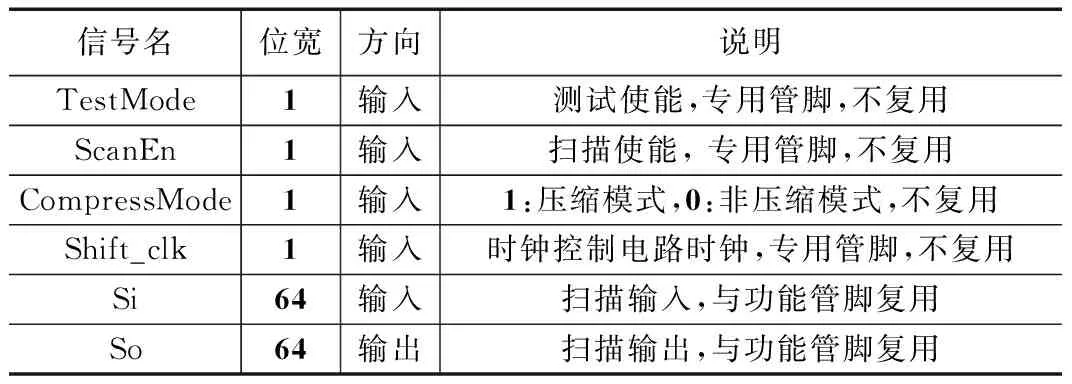

表2 扫描链控制接口表

3 扫描链测试设计实现

3.1 固定型故障测试扫描链设计实现

3.1.1 DSP扫描链测试设计

DSP硬核内部已经包含有扫描链结构,将DSP集成到SoC内部时将DSP的扫描链控制接口复用到芯片顶层的端口实现扫描控制和测试向量输入,测试使能信号、扫描使能信号、压缩模式信号和Shift_clk时钟采用芯片专用管脚,扫描链输入和输出管脚通过复用芯片顶层功能管脚实现。管脚复用完成后将顶层端口的控制端口信息加入到DSP的测试向量中,即可实现用SoC端口和DSP硬核自身的测试向量实现DSP的扫描链测试。

3.1.2 CPU扫描链测试设计

CPU和其余硬件逻辑的扫描链测试设计包括两部分内容:扫描链插入和测试矢量生成[4]。其中,扫描链插入具体的步骤为:

1)读入设计文件:读入的文件可以是DC综合后的Verilog格式或DDC格式的网表文件。

2)创建测试协议:创建测试协议需要定义测试相关的信号,包括定义时钟信号、复位信号、常量、测试模式、测试压缩信号、扫描端口信号(SI,SO,SE等)和扫描单元类型等,采用DFT Compiler工具脚本创建spf格式的测试协议文件。

3)设计规则检查(DRC):扫描链测试要求电路中的每个节点处于可控制和可观测状态,只有这样才可以保证其可替换为相应的扫描单元,并且保证故障覆盖率。为了保证电路中的每个节点都符合设计需求,在扫描链插入前会进行扫描设计规则的检查并根据DRC检查结果修改设计。基本设计规则包括:

(1)使用同种类扫描单元进行替换,选择带多路选择器的扫描触发器;

(2)在原始输入端必须能够对所有触发器的时钟端和异步复位端进行控制;

(3)时钟信号不能作为触发器的输入信号;

(4)三态总线在扫描输入模式处于非活跃状态;

(5)ATPG无法识别的逻辑应加以屏蔽和旁路;

(6)门控时钟或者门控异步输入端设计规则。

除了以上基本规则,其它设计规则还包括:

(7)尽量避免异步时钟设计;

(8)限制不同时钟域的数量;

(9)对于多时钟域的设计,处于同一时钟域的触发器最好连接在同一根扫描链上;

(10)对于扇出比较多的端口,如ScanEn信号,在综合的时候需要注意;

(11)对于存储器,模拟电路等不可综合的逻辑加入适当的隔离旁路结构;

(12)避免过长的扫描链,设置加入扫描压缩电路;

(13)尽量减少额外逻辑带来的面积、功耗的增大;

(14)通过复用引脚,减少扫描测试对引脚的要求。

4)插入扫描链:为了使得扫描链长度更加均衡,设计对扫描链链加入mix_clock功能;

5)插入扫描链后执行DRC检查;

6)生成测试协议文件和网表文件,用于后续的自动测试向量生成。

3.2 实速测试扫描链设计实现

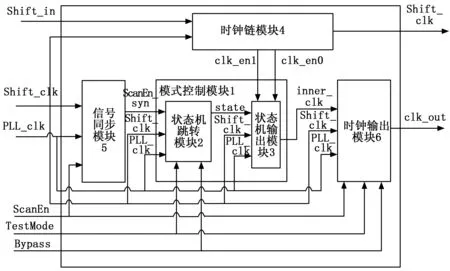

实速测试用于检测时延故障,其扫描链结构和测试流程与普通的扫描链测试一致,不同之处在于在扫描链捕获阶段的时钟不同。SoC芯片内部主要包含CPU时钟、DSP时钟、AXI时钟和APB时钟4个时钟域,其中CPU时钟、DSP时钟和AXI时钟为高速时钟,APB为48MHz低速时钟。为实现实速测试,在异构双核SoC芯片内部高速时钟设计片上时钟控制电路。片上时钟控制电路的作用为在扫描链的捕获阶段输出2个或多个高速的捕获脉冲,寄存器通过高速捕获脉冲寄存组合逻辑的输出值并通过扫描链输出,在扫描输出端口与期望测试结果比较即可判断芯片内部是否存在时延故障。片上时钟电路的结构如图3所示。

图3 片上时钟控制电路的结构图

片上时钟控制电路包括:模式控制模块、时钟链模块、信号同步模块和时钟输出模块。信号同步模块输入移位时钟shift_clk和高速时钟PLL_clk,shift_clk时钟由芯片外部输入,用于实速测试中扫描寄存器的移位,PLL_clk时钟由芯片内部PLL产生,用于芯片功能时钟或实速测试捕获时钟。通过寄存器同步方式对扫描使能信号ScanEn进行同步化,为保证同步后的ScanEn_syn信号可以正确的被shift_clk和PLL_clk时钟的上升沿采样,采用下降沿同步的方式。由于移位时钟Shift_clk的频率较低,故采用Shift_clk时钟对ScanEn信号进行一级寄存器同步,而PLL输出的时钟频率较高,采用PLL_clk时钟对ScanEn信号进行三级寄存器同步。

时钟链模块通过移位寄存器移位的方式将高速时钟使能信号移入由10个触发器组成的移位寄存器组,当触发器输入ATPG工具生成的二进制测试向量‘0’表示不产生高速时钟使能信号,‘1’表示产生高速时钟使能信号。测试向量中1的个数控制时钟链模块输出的高速时钟脉冲使能信号的个数。由于实速测试捕获阶段至少需要一个发射时钟和一个捕获时钟,测试向量中1的个数为2-10个,故时钟链模块可以产生2到10个高速时钟使能信号。

模式控制模块包括状态机跳转模块和状态机输出模块。状态机跳转模块根据3个控制信号决定当前电路的时钟模式,3个控制信号分别为测试模式信号TestMode,旁路信号Bypass和扫描使能信号ScanEn。只要信号TestMode=0时,电路就处于功能模式;当信号TestMode=1并且Bypass=1时,电路处于旁路模式;当信号TestMode=1、Bypass=0、ScanEn=1时,电路处于移位模式;当信号TestMode=1、Bypass=0、ScanEn=0时,电路处于捕获模式。状态机跳转模块控制状态机产生state状态信号,状态机输出模块根据state值输出内部时钟inner_clk信号。

时钟输出模块根据当前的时钟模式,控制选择器输出相应的时钟。当TestMode为0时,输出高速时钟PLL_clk;当TestMode为1,Bypass 为0,ScanEn为1时,输出shift_clk;当TestMode为1,Bypass 为0,ScanEn为0时,输出inner_clk;当TestMode为1,Bypass 为1时,输出移位时钟shift_clk。

通过片上时钟控制电路,可以产生芯片实速测试需要的高速时钟,进而实现芯片的实速测试,检测芯片的时延故障。

3.3 自动测试向量生成设计实现

异构双核SoC扫描链的ATPG设计的目的是产生测试向量并进行覆盖率评估。ATPG使用synopsys公司的tetramax软件,版本为J-2014.09;通过tetramax工具可以查看扫描链是否插入成功,另外,通过对测试覆盖率的评估,可以评判可测试性设计的优劣。ATPG设计实现过程如下:

1)读取测试协议spf文件:其中,对于刚刚从design_compiler中生成的spf而言,需要在test_seup阶段启动时钟信号,通常还会配置复位信号;

2)读取带扫描链的网表设计文件;

3)读入tetramax使用的库文件:读取工艺厂的库文件,变成tetramax可以识别的库文件;

4)构造ATPG模型;

5)DRC检查,如果DRC检查没有通过,通过tetramax可以分析原因,通常的原因是时钟、异步复位和测试控制信号不受控;

6)设置故障类型,覆盖率目标等参数;

7)运行ATPG,生成测试向量和对应的测试激励;

8)通过VCS仿真生成的测试向量。

4 扫描链测试结果

异构双核SoC采用全扫描测试设计,芯片共含有83000多个触发器,另外,异构双核SoC内部共有64条扫描链,平均长度约为1 296。通过ATPG工具生成测试向量,stuck-at测试向量个数为9 352个,固定型故障测试覆盖率为97.6%;实速测试生成测试向量个数10 380个,时延故障测试覆盖率为84.9%,满足芯片的测试故障覆盖率要求。

5 结束语

针对双核SoC的特点,给出了一种有效的扫描链测试方案,并设计了片上时钟控制电路,实现了芯片实速测试。结果表明,芯片的固定故障和时延相关故障测试覆盖率满足要求。

同时,设计的片上时钟控制电路可以方便的移植到不同的芯片扫描链测试设计中。

[1] 周 妮,乔 飞,谭斯斯,等.32位MIPS处理器可测性设计与实现[J].微电子学,2010, 40(6):782-791.

[2] 成 立,王振宇,高 平,等.VLSI电路可测性设计技术及其应用综述[J].半导体技术,2004,29(5):21-23.

[3] IEEE Standard Test Access Port And Boundary-Scan Architecture,IEEE Std 1149.1-1990[S].

[4] 徐勇军,张 伸,张志敏,等.SoC设计中的扫描测试技术[S].计算机辅助设计与图形学学报,2005,17 (12): 2685-2689.

[5] Steininger A. Testing and built-in self-test A survey[J]. Journal of Systems Architecture, 2000,46:721-747.

[6] 徐智伟,张盛兵.SoC的可测性设计策略[J].计算机测量与控制,2008,16(8):1095-1098.

Design and Implementation of Scan Based Test for Dual-core SoC

Liu Guangdong, Shi Guoshuai, Xu Haoran

(Institute of Beijing Computer Technology and Application,Beijing 100854, China)

In order to detect the defect of manufacturing such as short and open circuit, the scan based DFT circuit of dual core SoC is realized. The scan structure has been inserted into the hard-core DSP, so the DSP’s test ports are connected to the SoC chip leads. Scan chains are inserted into the CPU core and other hardware logic. Scan based test supports stuck-at fault and transition fault test. According to the transition fault, an on-chip clock control circuit is designed to use high speed PLL clock for at-speed test. The ATPG tool is used to generate test vectors, the result shows that the stuck-at fault test coverage rate can reach 97.6%, transition fault test coverage rate can reach 84.9%, meet the test coverage requirements of the chip.

design for testability; scan based test; dual-core ; on chip clock

2016-10-24;

2016-11-22。

刘广东(1985-),男,山东省单县人,硕士研究生,工程师,主要从事SoC可测性设计方向的研究。

1671-4598(2017)04-0015-03

10.16526/j.cnki.11-4762/tp.2017.04.005

TN407

A