基于FPGA的S模式并行数据编解码器设计

2017-05-03严玉国杨宾峰张战斌

李 雷, 严玉国, 杨宾峰, 张战斌

(空军工程大学信息与导航学院, 西安 710077)

0 引言

二次雷达S模式是在二次雷达传统的A/C模式上发展起来的,是为了克服在传统的A/C模式中可能同时有多架飞机做出应答,地面接收机将会产生严重串扰的问题[1]。为了避免这种串扰,在S模式询问信号中加入了飞机的地址信息,即可以实现有针对性的询问。

在二次雷达S模式中引入了CRC(cyclic redundancy check)校验,判断信号是否正确接收。文中在分析S模式信号格式以及CRC校验基本原理的基础上,针对传统S模式询问机和应答机的串行编解码器存在效率低的问题,提出一种改进型的并行编解码器的结构。文献[2]中的并行方法虽然可以实现并行CRC校验,但是存在算法设计复杂的问题。文献[3]中的查找表方法是用面积换取速度,消耗了大量硬件资源。文献[4]中使用长除法完成输出与输入关系之间的计算,存在计算过程复杂的问题。文献[5]中的迭代思路,在数据长度较大时,同样会存在设计复杂的问题。文中提出在MATLAB中完成编解码器的输出与输入数据之间的关系的分析,降低了设计的复杂性,通过修改迭代关系,可以直接完成其它结构的数据校验。

1 S模式数据格式

S模式询问信号的格式如图1所示[1]。

其中P1、P2是前导脉冲,长脉冲P6持续时间为16.25 μs或30.25 μs,其中包含了需要发射的数据信息。数据是通过DPSK调制的方式完成发射,相位翻转的时间间隔为0.25 μs,即数据的比特率为4 MHz。数据部分是由两部分组成,前面是32(88) bit的数据信息,后面24 bit是对数据信息的CRC校验结果和飞机地址信息与生成多项式G(x)相乘的结果进行异或运算。S模式应答信号的格式如图2所示[1]。

应答信号中前面的4个脉冲为前导脉冲,前导脉冲的作用是确认接收信息。数据部分包含在前导脉冲后的数据脉冲块中,数据部分是由32(88) bit的数据信息和24 bit数据信息的CRC校验结果和地址信息与生成多项式G(x)相乘的异或结果。数据通过脉冲位置调制(PPM)进行编码,比特率是4 MHz。

2 S模式编解码器

2.1 CRC的校验原理

CRC校验的基本思想是使用线性编码理论,按照一定的规则在发射端对发送的Kbit信息进行处理,得到Rbit校验信息。在接收端对接收到的信号再次进行校验,判断传输是否正确[6]。

2.1.1 发射端CRC校验码的产生

1)根据CRC校验的生成多项式G(x),首先对数据进行拓展。拓展结果为m(x)·xn,其中n为生成多项式的位数。

2)用生成多项式G(x)去除m(x)·x24,结果为:

(1)

3)校验结果为m(x)·x24+R(x)。即将步骤2中产生的余数放在数据的后面进行发射。

2.1.2 接收端对CRC校验进行解码

1)接收到的信息为m(x)·x24+R(x),用接收信息除G(x),结果为:

(2)

2)由于相同的序列异或的结果为0,根据上式,如果余数项为0,那么信号传输过程中没有出现错误,否则,说明传输过程中有错误。

2.2 二次雷达的CRC校验

在S模式的CRC校验中,以短格式为例,以下是其各种信息。

G(x)=x24+x23+…+x12+x10+x3+1

(3)

m(x)=x31m31+x30m30+…+x2m2+xm1+1

(4)

r(x)=x23r23+x22r22+…+x2r2+xr1+1

(5)

a(x)=x23a23+x22a22+…+x2a2+xa1+1

(6)

G(x)是生成多项式,m(x)是数据多项式,r(x)是校验多项式,a(x)是地址多项式。生成多项式是S模式CRC校验的对应的生成多项式,数据多项式是需要发射的数据信息,校验多项式是数据多项式通过生成多项式完成CRC校验的结果,地址多项式是飞机的地址信息。

在S模式中,对应的有询问机和应答机,询问机和应答机分别工作在不同的模式下,询问机完成询问信号的编码和应答信号的解码,应答机完成询问信号的解码和应答信号的编码。图3为S模式中询问机和应答机CRC校验的不同工作模式。

2.2.1 询问机CRC校验

询问机CRC校验包含询问信号的编码和接收信息的解码。

询问机编码器的结构如图4所示。首先将前面的32(88) bit信息直接发射,发射的同时将这些数据在编码器中与生成多项式G(x)相乘,即完成CRC校验。到了最后24 bit时,反馈回路将会被切断,直接将地址信息送入编码器中,就是将前面32(88) bit数据信息与生成多项式G(x)相乘的结果和地址信息与生成多项式G(x)相乘的结果进行异或运算[7-8]。

询问机解码器的结构如图5所示,结构与询问及编码器的结构类似,只是将最后要输入的24 bit地址信息改成0。从询问机解码器输出的结果中减去预期的24 bit地址信息,如果是0,那么说明传输并未出现错误。

2.2.2 应答机CRC校验

应答机CRC校验是完成应答信号的编码以及询问信号的解码。应答机编码器的框图与询问机的解码器的结构相同,如图5所示,与询问机编码器不同的是,24 bit飞机地址信息没有和生成多项式G(x)相乘,而是直接与24 bit数据校验结果进行异或运算。

询问信号的解码是对接收到的信息进行校验,判断是CRC校验是否通过。应答机解码器是对询问机发射的信号进行解码,解码的电路如图6所示,在这个电路中,实现了用G(x)除接收到的数据信息,除的结果是最后24 bit对应的是飞机的地址信息。最后,将解码器的输出地址与飞机自身地址进行比较。判断询问信号是否针对本机并被正确接收。

3 并行算法的设计

从图4、图5、图6的数据校验中可以看到,传统的串行结构是通过数据的不断移位和异或运算完成的,每个时钟周期只能处理一bit数据,对于Nbit数据的编码就需要N个时钟周期,这对于高速的数据处理速度有很大的影响。

文中结合S模式编解码器的结构,分别对询问机编码器,询问机解码器,应答机编码器,应答机解码器中的数据编码进行设计。

图7是文中设计的并行询问机编码结构图,以询问机编码器处理56 bit数据为例,给出具体的编码步骤如下。

1)把56 bit信息分成两部分:32 bit数据信息D31、D30、…、D0和24 bit地址信息A23、A22、…、A0。

2)根据生成多项式G(x),在MATLAB中对32 bit数据信息按照从高位到低位的顺序依次进行CRC校验,得到24 bit的CRC校验结果与输入数据信息D31、D30、…、D0之间的关系式,并将CRC校验结果存放在24 bit CRC寄存器中。

3)地址信息与生成多项式G(x)相乘,相当于卷积运算,其实质上也是一系列的移位和异或运算。对24 bit的地址信息按照卷积的规则,从高位到低位的顺序依次进行移位和与G(x)相乘,将最终的结果进行异或运算。卷积运算完成后的结果中高24 bit对应的是地址信息与G(x)相乘的结果,把结果存放在ADDR23、ADDR22、…、ADDR0这24个寄存器中。

4)对24 bit CRC校验结果和24 bit地址与G(x)相乘结果进行异或运算。

5)把信息的高32 bit信息作为编码结果的高32 bit,把步骤4得到的结果作为编码结果的低24 bit,完成数据的编码。

询问机解码器、应答机解码器、应答机编码器的设计过程与询问机编码器的设计过程类似,都是根据其计算过程中的迭代关系,对多位输入信息进行移位处理,最终将会得到输出与输入之间的关系。

4 并行算法的硬件实现

4.1 编码器结果的计算

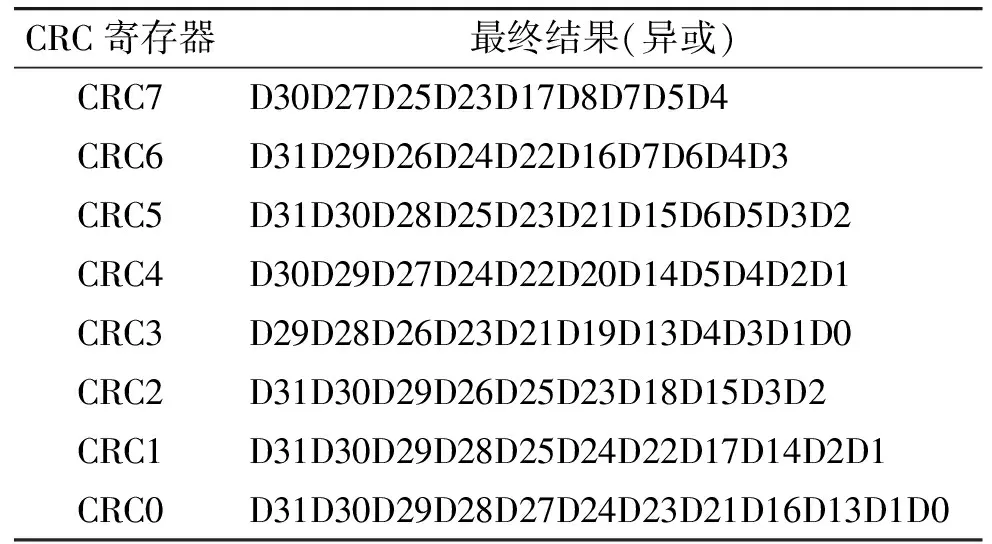

根据文中设计的编码器和解码器的思路,首先在MATLAB中完成数据的迭代处理,得到输出编码信息和输入信息之间的关系。表1中对应的是询问机编码器中地址信息校验的结果与32 bit发射数据信息之间的关系,CRC7到CRC0是CRC寄存器的低8 bit,由于篇幅有限,这里不列出所有的校验结果。

表1 32 bit数据CRC的校验结果

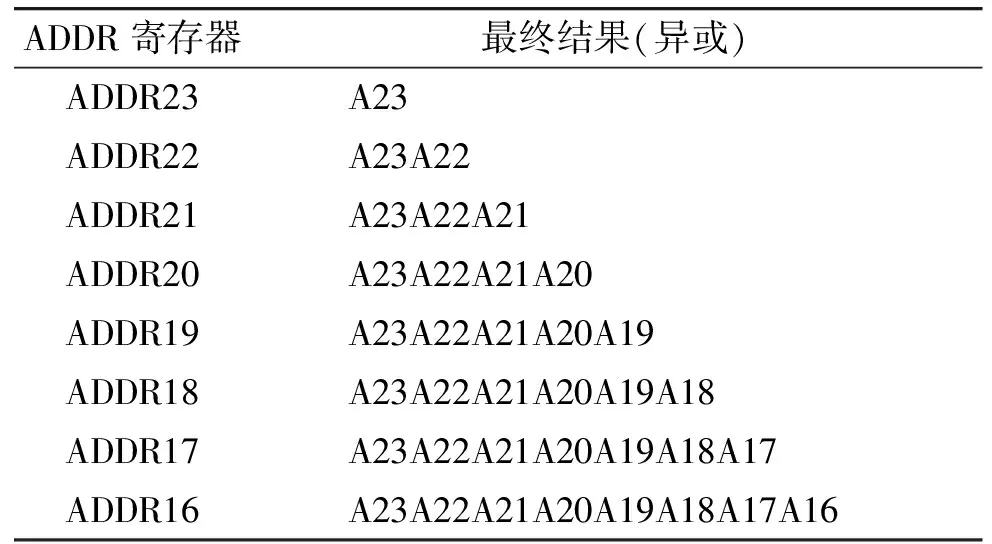

表2中,ADDR23到ADDR16对应的是24 bit地址信息与生成多项式G(x)相乘结果的高8 bit。

表2 地址处理结果

4.2 FPGA实现及仿真

根据4.1中的计算结果,用Verilog HDL语言完成了S模式编解码器的设计,并用Mentor公司的Modelsim软件对询问机编码器和应答机解码器进行功能仿真。将传统的询问机编码器和应答机解码器的仿真结果与改进型的询问机编码器和应答机解码器结构进行对比。

图8、图9分别是传统的串行询问机编码器和改进的并行询问机编码器仿真结果。其中clk是时钟信

号,rst是复位信号,data_in是发送数据信号输入,addr_in是发送的地址信号输入,encode是编码后输出结果。从图中可以看出,传统的串行结构的询问机编码器需要56个时钟周期才能完成数据的编码,而改进的并行询问机编码器只需要一个时钟周期就可以完成发送数据的编码,编码效率提高56倍,达到预期的设计目标。

图10、图11分别是传统的串行应答机解码器和改进的并行应答机解码器的仿真结果。其中clk是时钟信号,rst是复位信号,data是接收信号输入,addr_out是解码后输出的地址信息。从图中可以看出,传统的串行应答机解码器需要56个时钟周期完成接收数据的解码,从中提取地址信息,而改进的并行应答机解码器只需要一个时钟周期就可以完成数据的解码,并提取地址信息。解码效率提高56倍,达到预期的设计目标。

5 结束语

文中提出了一种并行的编解码器结构。可以在一个时钟周期内完成串行结构中多个时钟周期才能完成的数据编解码工作,提高了编解码效率。与其它文献中的并行结构相比,文中使用MATLAB完成输出与输入之间的关系计算,通过修改迭代关系,就可以完成不同结构的设计,降低了设计的复杂性。可以将文中的设计方法推广到其它类似的迭代处理过程中去,将串行结构处理数据转为并行处理,提高数据处理效率。

参考文献:

[1] 张尉. 二次雷达原理 [M]. 北京: 国防工业出版社, 2009: 11-12, 141-146.

[2] 毕占坤, 张羿猛, 黄芝平, 等. 基于逻辑设计的高速CRC并行算法研究及其FPGA实现 [J]. 仪器仪表学报, 2007, 28(12): 2244-2249.

[3] 季鹏辉, 孟丁, 任勇峰. 基于FPGA的16 bit CRC校验查表法设计 [J]. 电子器件, 2013, 36(4): 580-584.

[4] 范红旗, 王胜, 祝依龙. CRC编解码器及其FPGA实现 [J]. 数据采集与处理, 2006, 21(增刊): 97-100.

[5] 张树刚, 张遂南, 黄士坦. CRC校验码并行计算的FPGA实现 [J]. 计算机技术与发展, 2007, 17(2): 56-58.

[6] 西瑞克斯(北京)通信设备有限公司. 无线通信的MATLAB和FPGA实现 [M]. 北京: 人民邮电出版社, 2009: 182-184.

[7] 徐赏, 黄建国, 李力. S模式数据链CRC校验实现方法 [J]. 测控技术, 2012, 31(2): 27-30.

[8] 黄晓卿. 基于FPGA的S模式信号处理 [J]. 电讯技术, 2012, 52(5): 716-720.