基于FPGA的数据记录器关键技术优化

2017-05-03刘佳宁刘东海

文 丰, 刘佳宁, 刘东海

(中北大学电子测试技术国家重点实验室, 太原 030051)

0 引言

现代电子技术的飞速发展对数据存储的容量,读写速度和可靠性都提出了更高的要求,新兴的FLASH闪存具有容量大,密度高,读写速度快,且成本低的特性,在大容量数据存储领域应用前景非常好[1]。

FLASH存储介质有NOR和NAND两大类,NOR型FLASH具有相互独立的数据地址线,支持顺序读取和随机读取,弊端是容量小,因此通常用作代码存储;NAND型FLASH则容量大,读写快,更适用于大容量存储,地址线和数据线分时复用,因此其时序设计相对复杂。

本设计采用NAND型FLASH,改进传统FLASH应用中单线校验的指令识别方式,采用4线指令组合校验机制保证指令的可靠识别;并且优化无效块检测方式,提高FLASH工作效率,同时升级FLASH编程模式和读数机制,有效提高FLASH的读写速度,最后降低整个电路的功耗,进一步增强电路的稳定性。

1 总体方案

1.1 系统硬件设计

记录器的主要功能是完成数据的可靠存储,保证在后期数据处理阶段完成数据回放。系统硬件设计框图如图1所示。

整个设计采用模块化设计。FPGA作为控制核心,接收和识别前级设备的指令,并产生相应的控制信号完成整个电路的逻辑控制;数据收发接口完成存储电路与前级设备之间的数据高速交换,通常选用LVDS总线或HOTLINK接口完成;FLASH控制模块给FLASH芯片提供完整的时序控制,完成数据的写入与读出操作。DC-DC模块给整个电路供电,保证各模块的正常工作。

1.2 控制逻辑设计

FPGA负责整体的逻辑控制,其逻辑设计如图2。

指令解析模块接收和识别前级设备的指令信号,解码后生成相应的使能信号控制整个电路的正常工作;FLASH控制模块接收FPGA主控逻辑的控制信号后对FLASH芯片进行时序控制,完成擦除和读写操作;无效块ROM表实时更新FLASH芯片无效块地址,保证FLASH块的正常操作;数据缓存模块实现与前级设备的高速数据交换;读写缓存的设置实现外部接口速率与FLASH接口速率的匹配,保证数据的高速读写。

2 存储设计的关键技术

NAND型FLASH是一种非易失性存储器件,数据存储的可靠性和读写速率成为FLASH应用中的关键指标。

2.1 指令可靠性优化

记录器设计中首先要避免的是指令的误判,传统的指令识别方式是直接识别单线指令,这种方法可能会导致指令误判,造成FLASH的工作状态不受控,影响数据记录器的稳定性。本设计采用4线指令(State0、State1、State2、req)并行控制的方式,应用移位表决器配合双重计数器消抖的防指令误判技术,最大程度保证指令的可靠识别。指令识别的具体流程见图3。

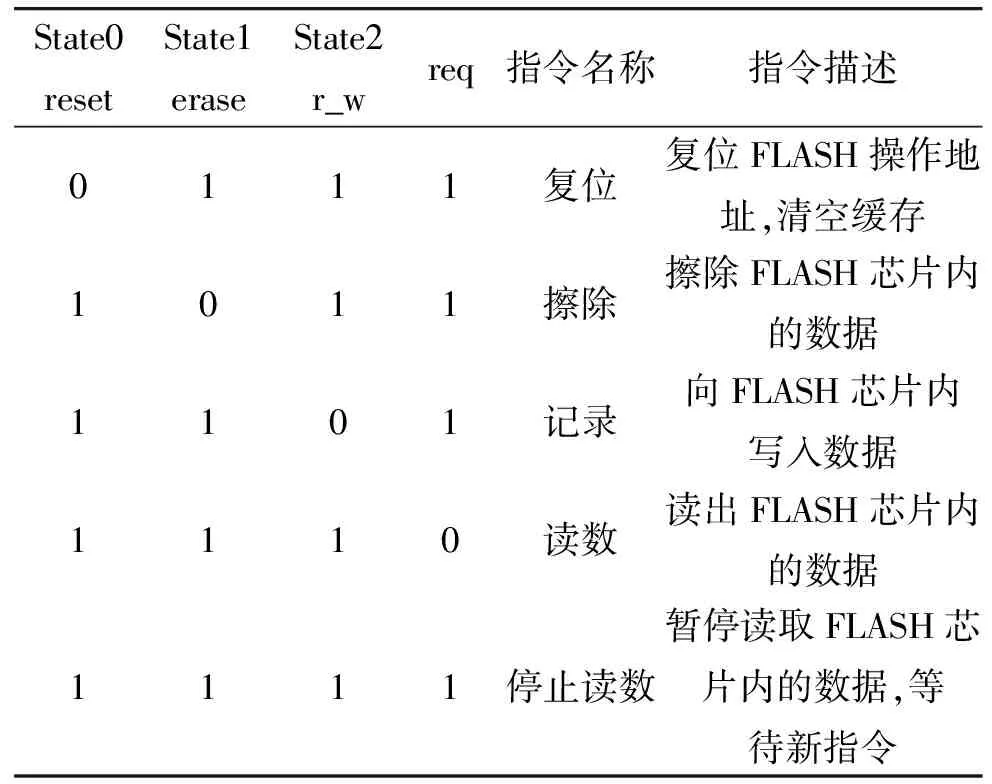

FPGA同时接收4线并行指令,经过单个指令的移位表决和计数器消抖后构成组合指令,组合指令经过第二重计数器消抖后判断是否为预定义的有效组合,然后输出相应的使能信号或重新采样单线指令。这3重措施可以有效过滤错误指令和伪指令,防止指令误判,保证FLASH存储控制的可靠性。预定义的组合指令见表1。

表1 组合指令定义

2.2 写入速度分析

FLASH写入操作是基于块擦除和页编程的,因此高效的无效块检测方式和页编程流程是提高FLASH写入速度的关键[2]。比较市场占有率较高的两款FLASH应用芯片:三星K9WBG08U1M和镁光MT29F64G08A-FABA,虽然三星芯片具有更高的操作频率,但相同容量下,其页容量少,块个数多,导致其无效块校验需要更多的时间,写入操作的时序控制更加复杂。本设计选用镁光芯片,且根据其芯片特性,优化了无效块检测方法和页编程方式,达到了更快的写入速度。

2.2.1 无效块检测优化

由于FLASH制作工艺的限制,FLASH芯片内部存在随机分布的无效块。使用前必须对FLASH进行无效块检测,防止对无效块进行误操作。通用处理办法是在FPGA内部预先开辟一段ROM存储空间,每次FLASH器件上电后,程序依次对FLASH器件进行复位,初始化和无效块检测操作。判断FLASH存储块第一页和第二页的4 096个地址的值是否为“FF”,如果是则认定当前块为有效块,否则将块地址写入ROM存储[3]。

每次对块进行擦除或读写时均需要与ROM中存储的坏块地址进行比较,以确保当前操作的块不是坏块。FLASH器件检测无效块的典型时间为20 μs,如果每块操作都进行检测,随着块个数的增多,势必会影响数据的写入和读出速度。

MT29F64G08AFABA芯片的内部阵列如图4,整个芯片由两组LUN组成,通过片选CE区分操作,每组LUN由两个PLANE组成,且这两组PLANE允许单独的块擦除和读写操作。

基于这个特性,本设计对无效块的检测采用批次检测的方法,每4个Block划为一批。即对CE1和CE2的PLANE0和PLANE1这4个Block分别进行无效块检测,有无效块出现时将CE1的PLANE0的块地址写入ROM,对这4个块均视为无效块。每次需要对块操作时,将CE1的PLANE0中的块地址与ROM列表当前地址进行对比,如果是无效块,PLANE0块地址和ROM表地址均自增1,跳过这批块,重新判别,否则,直接对当前4块进行操作,不需要再对另外3个块做无效块检测。这种机制虽然造成了一定的空间浪费(MT29F64G08AFABA中最多有160个无效块,最大损失容量160×4×1 MB=640 MB),但无效块检测时间缩短为原来的25%,大大提高了检测效率。

2.2.2 页编程方式

页编程操作可以分为两个步骤:1)加载操作,完成命令字、地址字和数据到块寄存器的加载工作;2)编程操作,FLASH芯片内部自动将寄存器中的数据写入到存储阵列,该操作典型用时230 μs,期间FLASH不做任何操作,也不响应任何指令[4]。

为了提高写入速度,FLASH编程操作采用流水线工作模式,应用交替双平面交叉写入的页编程方式,即在当前平面编程操作的同时进行下一平面的加载工作,充分利用了芯片编程时的闲暇时间,实现加载操作和编程操作的分时复用。其时空示意图如图5。

FLASH写入寄存器的峰值速度为30 MB/s,写入寄存器的页容量为8 KB,第一页加载操作用时Δt1。

式中:twc为写入周期,为地址字和命令字的写入时间,芯片编程典型用时Δt2-Δt1为230 μs,4页完成加载操作总时间Δt3为:

式中:tDBSY为双平面切换的等待时间。可知,当后3页完成载入操作时,第一页已完成编程操作,继续进行载入操作。

Δt3时间段内共完成4×8 KB数据的写入,故MT29F64G08AFABA芯片的平均写入速度为:

由于实际操作过程的影响,编程速度略小于写入速度,几乎已经达到FLASH芯片的速度极限。

2.3 FLASH读取方式

FLASH读取速率理论上同写入速度一样可以达到近30 MB/s的峰值速度,然而由于ECC等校验机制的应用,误码的校正会导致读取速度的降低,因此,本设计采用双缓存交替握手读数的思想,保证即使出现误码纠错的情况,数据发送模块暂停发送数据,FLASH芯片也不会因为缓存溢出而暂停读数操作,保证FLASH读取的速率。存储器读数逻辑设计如图6。

write_cnt、read_cnt作为缓存读写的握手信号实现对缓存A、B的高速读写。当write_cnt-read_cnt<2时,FLASH向缓存中交替写入数据,保证缓存中数据未读取前不被新数据覆盖丢失;当write_cnt-read_cnt>0时,允许发送模块发送缓存A或B中数据,确保发送的数据为FLASH读取的有效数据。

2.4 电路功耗优化

针对存储电路设计的小型化要求[5],必须尽可能的降低存储电路的功耗,防止内部集中布局的芯片产生大量热量影响电路的工作性能。

供电模块选用的电源芯片为MAX1818和TPS71825,MAX1818完成FPGA芯片的IO口和高速收发模块的3.3 V供电,TPS71825-12对FPGA芯片内核的1.2 V和1.8 V供电。整个电路中,电源芯片的输出电压固定,通过降低整个电路的工作电压来降低电路功耗,改善电路散热。MAX1818的最小压降为120 mV,考虑线路压降,选择3.6 V作为输入电压,也满足TPS71825的电压输入要求,相比传统的5 V供电,减轻了电源芯片的功耗压力。

这种设计方案本质是通过一种电源转换芯片,将存储电路的部分功耗转移到该电源芯片上,以降低存储电路的功耗压力,保证电路的可靠工作。实际应用中,将转换芯片固定在前级设备上,将存储器上的部分功耗转移到外部,改善整个电路的供电稳定性。

3 结束语

文中针对FLASH存储设计中需要解决的几个关键技术做了详细的分析说明。采用组合校验机制保证了指令的可靠识别;通过优化无效块检测方法和页编程方式,提高了FLASH的操作速率,存储速度几乎达到30 MB/s写入速度峰值,大大提高了FLASH的工作效率;双缓存交替握手的读数机制保证了FLASH读数操作不受纠错机制影响。最后,文中通过设计转移存储单元的部分功耗来降低电路板实际功耗,从而增强了整个电路的可靠性。

参考文献:

[1] 刘东海, 任勇峰, 储成君. 基于FPGA控制的NAND Flash存储设计 [J]. 科学技术与工程, 2013, 13(34): 10349-10353.

[2] 储成群. 基于LVDS接口的高速数据记录器的设计 [D]. 太原: 中北大学, 2011: 41-45.

[3] 舒文丽, 吴云峰, 赵启义, 等. NAND Flash存储的坏块管理方法 [J]. 电子器件, 2011,34(5): 580-583.

[4] Micron Technology. MT29F64G08AFAAAWP NAND FLASH Datasheet. 2009.

[5] 车艳霞. 基于Flash的高速数据记录装置关键技术研究 [D]. 太原: 中北大学, 2012: 12-14.