HS6L高速数据总线设计

2017-05-02李震,张鹏

李 震,张 鹏

(中车青岛四方车辆研究所有限公司,青岛 266031)

HS6L高速数据总线设计

李 震,张 鹏

(中车青岛四方车辆研究所有限公司,青岛 266031)

本文提出了一种高速总线的设计方法。HS6L是一种高速全双工总线,主要应用于短距离高速数据传输领域。在短距离传输场合,相对于普通的并行总线以及串行总线,HS6L总线具有明显的优势。介绍了HS6L总线的帧格式和硬件组成,重点介绍了HS6L总线收发控制器的设计方法。

HS6L总线;高速总线;串行总线

0 引言

工业控制领域经常需要较短距离的高速数据传输,目前可应用于短距离数据传输的总线机制有:普通并行总线传输、PCI和PCI-E总线传输、CAN总线传输、RS232和RS485总线传输等等。本文介绍的HS6L总线是一种全双工高速总线,由4根数据总线、2根时钟线组成。相对于并行总线而言,HS6L总线具有更少的硬件资源消耗;相对于PCI和PCI-E而言,HS6L总线具有较低的成本,并且对系统平台的依赖较小;相对于CAN总线、RS232、RS485总线,HS6L总线具有更高的传输速率。

简要概括HS6L总线的特点如下:

1)点对点传输,采用全双工的总线收发机制,每组由2根数据线、1根时钟线组成,可取代普通的并行总线,可降低硬件设计成本。

2)单向最高传输速度可达240Mbps,双向最高传输速度可达480Mbps。

3)在时钟上升沿和下降沿都进行数据采集。

4)采用固定数据帧长度通讯,且数据帧长度可配置。

5)具有自检和重发功能。

6)带隔离功能的HS6L总线可实现不同电平之间的设备通讯,可满足高可靠性场合的要求。

HS6L总线的主要应用领域为:1)板卡内功能模块之间高速通讯。2)机箱内部板卡之间高速通讯。3)设备间短距离高速通讯。

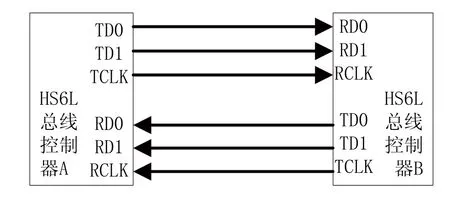

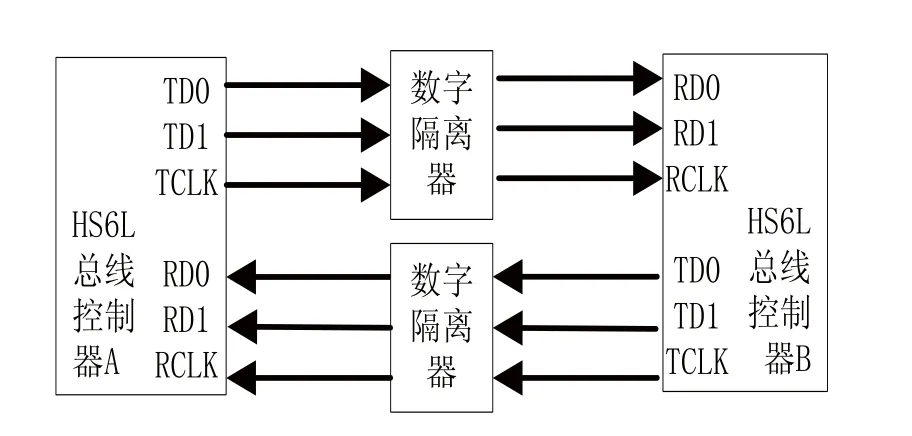

1 HS6L总线的硬件组成

HS6L总线采用4根数据总线和2根时钟线。其硬件构成框图如图1所示。带隔离功能的HS6L总线系统框图如图2所示。带隔离功能的HS6L总线是在2路通讯线中加入数字隔离器,以满足不同电平标准的设备之间的数据通讯,同时这种总线可以应对工业现场对高可靠性的要求。

在数字隔离器输出端口处需要加总线匹配电阻来降低接收端信号的过冲,进一步提高信号的质量。

系统运行在全双工模式,同一时刻既可以发送也可以接收,在总线空闲时,数字隔离器输出高阻态。总线工作时各个节点使用相同的波特率,接收端采用2倍通讯频率进行信号采集。

图1 HS6L总线框图

图2 HS6L隔离总线框图

2 HS6L总线的通讯协议

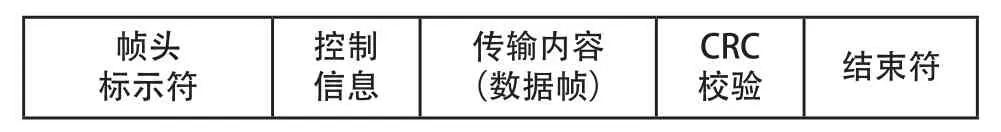

HS6L总线的帧格式如表1所示。

表1 HS6L总线帧格式

帧头标示符有3个作用:1)通知接收端准备接收,2)接收端通过接收帧头标示符来精确确定可靠的采样间隔,3)如果总线上有两个节点同时尝试发送,可通过总线冲突自检机制,在帧头标识符发送阶段进行冲突检测。帧头标示符由7~10个0x7E组成。

帧头标示符结束后紧跟着一个4位的控制位。控制位的第0~1位为控制信息位。控制信息标示有两种,表示的意义如下:

01:主机发出的数据帧标示。数据帧标示后紧跟接收节点的地址(4位)和本帧传输的字长度(4位)。

10:从机发出的响应帧标示。响应帧标示后紧跟接收节点自身的地址(4位)和本次接收的字长度(4位)。

控制位的第2~3位为发送个数计数器,在正常情况下,针对同一个主机(发送节点),每成功发送一帧数据帧,计数器中的计数加1。如果主机在发送一个数据帧后在规定时间内没有收到从机(接收节点)的响应帧(响应超时),主机将在规定时间之后重新发送本次数据帧,此时计数器中的计数值保持不变。

传输内容及通讯发送的数据,只在数据帧中体现,响应帧中没有传输内容。

CRC校验为数据帧中控制信息和传输内容的CRC校验。响应帧中CRC校验为控制信息的CRC校验。

如果从机接收到的数据帧CRC校验正确,将在规定时间内自动发送正常响应帧。如果CRC校验错误,从机也会在规定时间自动发送响应帧,但是响应帧中的CRC校验将为控制信息CRC的校验加1。主机发现接收的校验帧CRC错误,会自动重发上一帧的数据帧。

结束符为本次通讯的结束标志。由一个0x7E组成。主机在发送完结束符以后,必须在发送频率一个周期之内,将发送端口置为高阻态。当总线上的其他节点接收到通讯结束符以后,可以在一个通信时钟周期之后抢占总线。

3 HS6L总线收发控制器设计

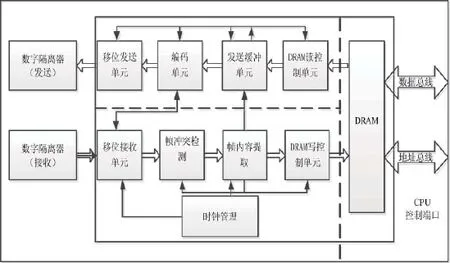

这里使用FPGA进行控制器的设计,HS6L总线控制器的组成框图如图3所示。

从图中可以看出控制器主要由3个部分组成:发送部分、接收部分和双口RAM(DRAM)。DRAM为HS6L总线和控制端口之间提供缓冲;发送部分提供从DRAM中读取发送内容,转换成HS6L总线可发送的编码,并通过数字隔离器发送出去;接收部分实时监测HS6L总线上存在的数据,作为节点接收的情况下,提供接收功能,在节点发送的情况下,提供帧冲突监测功能。下面分别对各个部分展开说明。

3.1 发送部分

发送部分由移位发送单元、编码单元、发送缓冲单元和DRAM读控制单元组成。

DRAM读控制单元通过内部并行总线实时监视发送指令存储器,一旦收到发送指令,则立即将发送数据从DRAM中读取出来,并传递给发送缓冲单元。由于DRAM控制单元采用系统内部的高速并行总线,因此对DRAM的写速度非常快。

图3 HS6L总线控制器框图

发送缓冲单元的核心由一个大小为64个字的内存组成,这个单元的作用为接收到DRAM中的数据以后,根据数据的长度和内容,得到帧头的控制信息、帧内容和帧CRC的校验和,并将这些信息以32位的形式存储到内存中,以提供下一个接口单元使用。发送缓冲单元中的内容会一直保持有效,一直到接收控制器收到本次发送帧对应的响应帧为止。如果CPU控制器控制端口强行复位HS6L总线控制器,发送缓冲单元中的内容也将失效。

发送缓冲单元将发送内容准备好以后会将需要发送的内容传给编码单元,编码单元会将需要发送的数据由32位转换成2位的形式,并且在数据帧的头部添加帧头标示符和帧尾结束符。同时编码单元接收从移位接收单元发送过来的使能信号,这个使能信号在检测到HS6L总线空闲的时候有效。当编码单元内有有效信息时,一旦使能信号有效,编码单元将立即将发送数据发给移位发送单元。

移位发送单元接收由编码单元传递过来处理好的数据,通过2位数据总线发送到数字隔离器的接口,开始发送。当发送结束的时候,移位发送单元会立即将数字隔离器(发送)置为高阻态。

3.2 接收部分

接收部分由移位接收单元、帧冲突检测单元、帧内容提取单元和DRAM写控制单元组成。

接收部分一直处于工作状态。当控制器发送数据的时候,接收部分会不断检测总线上的实际信号,一旦发现总线冲突,则立即通知移位发送单元将总线端口置为高阻态,并在总线空闲的时候重新发送。当控制器不发送数据的时候,接收部分一直接收来自总线的数据。

移位接收单元使用2倍HS6L总线频率进行采样,从采样数据中提取出可靠的采样数据并且传递给下一个环节。移位接收单元通过帧头标示符进行准确的采样定位,并使用定位结果对此帧剩下部分进行接收。一旦移位接收单元检测到帧头标示符有效,就会立即将接收的结果发送给帧冲突检测单元。

帧冲突检测单元只在此控制器发送数据的时候有效,一旦检测到发送的数据和总线上其他节点有冲突,帧冲突检测单元会在一个系统时钟之后发命令给移位发送单元和发送缓冲单元,立刻禁止输出。如果控制器不发送数据,帧冲突检测单元无效,并直接将数据传递给帧内容提取单元。

帧内容提取单元负责将接收到的数据进行ID检验和CRC校验,如果CRC校验失败,帧内容提取单元会通知发送缓冲单元发送CRC错误响应帧。如果ID校验失败(接收到的数据帧不是发给本节点),帧内容提取单元会自动将该帧抛弃掉。如果ID和CRC校验成功,则将接收到的2位带宽数据转换成32位数据,并将转换后的数据传递给DRAM控制单元。

DRAM写控制单元将帧内容提取单元发送过来的数据内容写入DRAM内存单元。CPU控制端口可以通过并行总线高速访问DRAM内接收到的数据。

4 结束语

本文介绍了HS6L总线的设计方案。实践证明在短距离高速数据传输的情况下,HS6L总线具有很大优势。在保证系统可靠性的同时,可以保证较高的通信速率。同时HS6L总线采用4根数据线+2根时钟线的结构,在机箱背板的应用场合可以极大的降低硬件的设计难度。在短距离设备间使用线缆通信的场合,可以使用4芯屏蔽线作为理想的传输线缆,屏蔽层可作为地线,且具有很好的电磁兼容性能。

[1] Dean J. Ghemawat S. MapReduce:Simplified data processing on large clusters[J].ACM Communication,2008,51(1):107-113.

[2] Lubomir F B, Show A C.Operation System Principles[M].New Jersey: Prentice Hall.2003.

[3] Kaashoek F,Morris R,Mao Y.Optimizing MapReduce for multicore architectures[J].MIT Computer Science and Artificial Intelligence Laboratory:Technical Report MIT-CSAILTR-2010-020,2010.

Design of HS6L high speed data bus

LI Zhen, ZHANG Peng

TN92

:A

1009-0134(2017)03-0142-03

2016-12-26

李震(1986 -),男,工程师,硕士,主要从事动车组列车车载设备的研究。