基于CNFET的高速低功耗三值灵敏放大器设计

2017-04-27龚道辉汪鹏君康耀鹏张会红宁波大学电路与系统研究所浙江宁波315211

龚道辉, 汪鹏君, 康耀鹏, 张会红(宁波大学电路与系统研究所,浙江宁波 315211)

基于CNFET的高速低功耗三值灵敏放大器设计

龚道辉, 汪鹏君, 康耀鹏, 张会红

(宁波大学电路与系统研究所,浙江宁波 315211)

通过对碳纳米场效应晶体管(Carbon Nanotube Field Effect Transistor,CNFET)和灵敏放大器原理的研究,提出了一种基于CNFET的高速低功耗三值灵敏放大器设计方案。该方案首先剖析三值反相器电路结构,采用交叉耦合反相器作为三值锁存器;其次结合输入输出信号分离方法,提高放大差分信号速度;然后利用使能信号控制电路状态,降低三值灵敏放大器功耗。采用32 nm CNFET 标准模型库进行HSPICE仿真,结果表明所设计的电路逻辑功能正确;芯片成品率高达96.48%,具有较强的稳定性,且与利用CMOS设计的二值灵敏放大器相比工作速度提高64%,功耗降低83.4%。

碳纳米场效应晶体管;三值灵敏放大器;成品率;高速低功耗

随着集成电路的发展,微处理器中50%以上的晶体管用于存储器的设计[1]。存储器的设计对微处理器的性能有很大的影响,因此高性能存储器的设计显得尤为重要,提升存储器外围电路的性能可提高存储器的性能。灵敏放大器是存储器重要的外围电路之一,灵敏放大器的性能直接影响存储器的速度及其功耗[2]。文献[3]提出了三值SRAM单元的设计,三值SRAM具有存储信息密度高等优点,因此国内外对三值存储器的研究越来越多。由于三值SRAM位线电容通常比较大,充放电时间较长[4],限制了三值SRAM信号的读出速度。三值灵敏放大器可放大位线小摆幅差分信号,输出全摆幅信号,从而提高三值存储器的读出速度和输出信号驱动能力。

工艺尺寸进入纳米量级后MOS管阈值电压失配越来越严重,利用CMOS技术设计的三值灵敏放大器失调电压越来越大,芯片成品率低[5]。MOS管的物理特性决定了其漏电流和极间电容大,所设计的三值灵敏放大器功耗高、延时大。具有准一维结构的碳纳米管(Carbon Nanotube,CNT),其载流子的运输具有弹道传输特性,CNT相比三维体硅和二维绝缘衬底上的硅具有更好的电子控制能力[6]。碳纳米场效应晶体管(Carbon Nanotube Field Effect Transistor,CNFET)的构成是利用CNT作为导电沟道,因此CNFET阈值电压失配小,利用CNFET设计的三值灵敏放大器失调电压低,芯片成品率高。因CNT的优越特性,CNFET的极间电容远小于MOSFET的极间电容,故利用CNFET设计的三值灵敏放大器具有高速、低功耗特性。本文通过对CNFET结构特性进行分析,结合三值逻辑理论,利用CNFET设计高速、低功耗三值灵敏放大器。

1 碳纳米场效应晶体管

单壁碳纳米管(Single Walled Carbon Nanotube,SWCNT)是由一层石墨稀片沿某一轴向卷曲的直径在纳米量级的中空圆柱[7]。根据卷曲的轴向不同,卷曲轴向由手性矢量(n,m)表示,可以将碳纳米管分为金属型和半导体型。当n=m或n-m=3i时,碳纳米管为金属型,其他情况为半导体型,其中i为整数。单壁碳纳米管圆柱直径DCNT可由如下公式计算[6]:

(1)

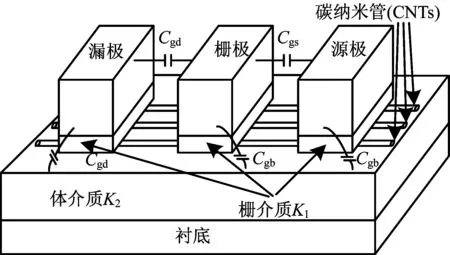

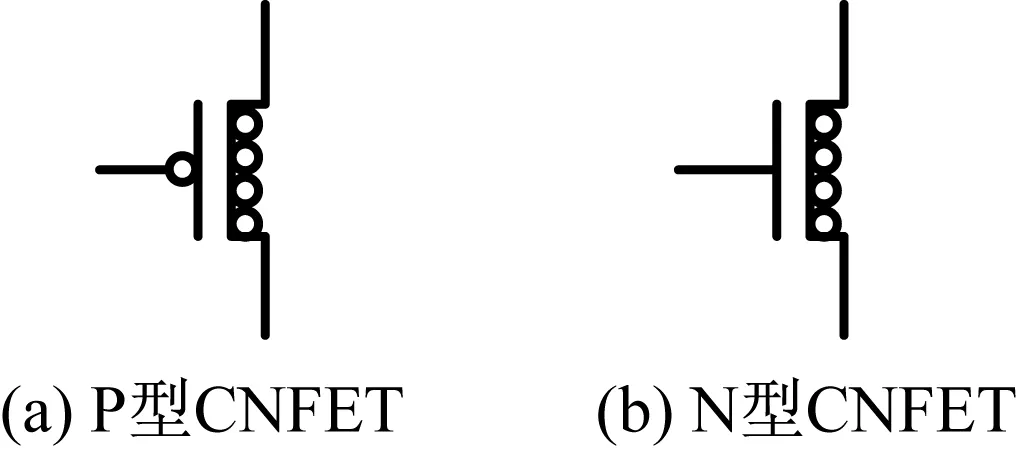

其中,a0为石墨烯片中碳-碳键长,通常a0=0.142 nm。碳纳米场效应晶体管(CNFET)可由碳纳米管组成,在Si衬底生长薄层SiO2,然后将碳纳米管作为导电沟道放置在薄层SiO2上,并加上电极,便制得CNFET,其结构如图1所示。CNFET与MOSFET结构类似,有栅极、源极、漏极和基极4个端口。CNFET栅极下方沟道区域的碳纳米管不掺杂,栅和源/漏极之间的碳纳米管重掺杂;根据掺杂物质的不同,可以将CNFET分为P型和N型两类,其电路符号如图2所示。在CNFET的制造过程中,通过控制CNT的直径DCNT可得到不同阈值电压的CNFET。CNFET的阈值电压和直径DCNT的关系可由式(2)给出[6]:

(2)

其中:a为石墨烯片中碳原子与碳原子之间的距离,通常a= 2.49×10-10m;Vπ= 3.033 eV为碳-碳键π键的键能;e为元电荷;DCNT为碳纳米管的直径。

图1 CNFET结构

图2 电路符号

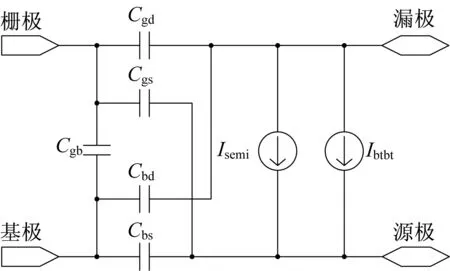

由CNFET结构图(图1)可知,栅极、源极、漏极和衬底之间存在电容。图3给出了半导体型N型CNFET的等效电路,由传输电容网络和电流源网络组成。传输电容网络包括栅源间电容Cgs、栅漏间电容Cgd、栅极与衬底间电容Cgb、源极与衬底间电容Csb和漏极与衬底间电容Cdb等极间电容,而且CNFET的极间电容只有传统MOSFET的4%[7]。

图3 碳纳米场效应晶体管等效电路

电流源网络由半导体次能带电流Isemi和漏电流Ibtbt组成。在N型CNFET中,半导体次能带电流主要由电子定向移动产生,Isemi可表示为[6]

(3)

其中:e为元电荷;h为普朗克常数;k为玻尔兹曼常数;T为开尔文温度;Vch,DS为沟道内漏极到源极的费米电势;Tm为载流子传输概率;Em,0为第m级次能带的半帯隙;km为圆周方向第m次能带载波数;M为次能带总数;ΔΦB为沟道表面势的变化,它随栅极和源/漏极之间偏置电压的变化而变化。当N型CNFET处于亚阈值导通时,以漏电流Ibtbt为主,Ibtbt可表示为[6]

(4)

其中:Ef为碳纳米管源/漏极掺杂区域的费米电势;Tbtbt为带间隧穿概率。

2 基于CNFET的三值灵敏放大器设计

2.1 三值反相器

在三值逻辑系统中,“0”、“1”和“2”分别表示假、未定义和真。三值逻辑的基本运算定义如下[7]:

(5)

其中:Xi,Xj∈{0,1,2};运算符“-”、“+”、“·”、“—”分别表示“减法”、“与”、“或”、“非”运算。由式(5)可得三值反相器的真值表,如表1所示。

表1 三值反相器真值表

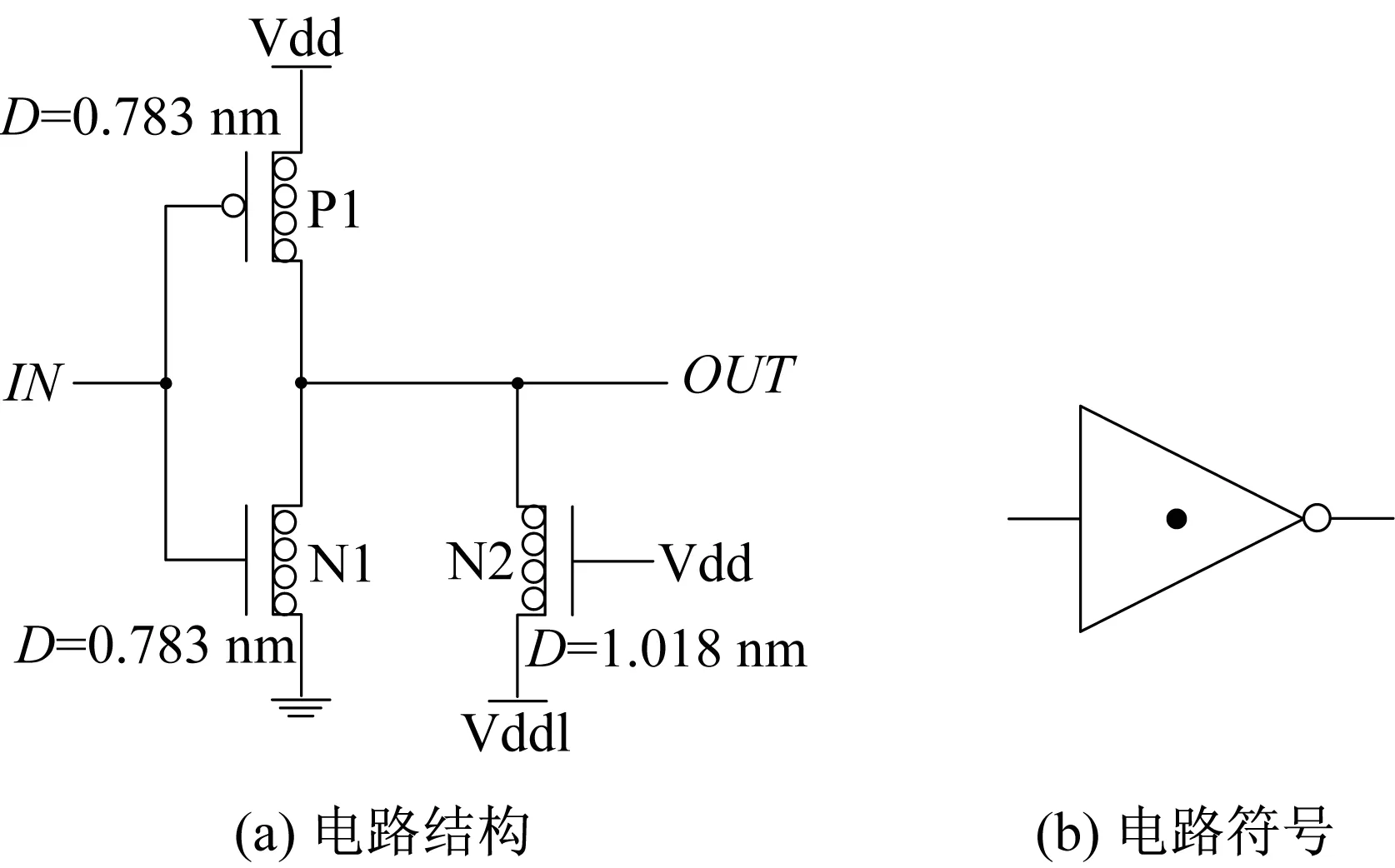

二值SRAM中最常用的是电压锁存型灵敏放大器,而交叉耦合反相器是常见的锁存器。因此,在三值灵敏放大器中,采用交叉耦合三值反相器作为锁存器。图4示出了文献[3]中的三值反相器,该反相器需两个电源(Vdd和Vddl),取Vdd=0.9 V、Vddl=0.45 V。由式(1)和式(2)可知P1、N1、N2管阈值电压分别为-0.557、0.557 、0.428 V。N2管栅极接电源Vdd,源极接电源Vddl,因此N2管处于常导通状态。为使输出OUT能输出逻辑值“0”、“1”、“2”,N2处于弱导通状态。当输入IN为逻辑“0”时,P1管导通、N1管截止,Vdd将输出OUT充电到Vdd,输出逻辑值“2”。当输入IN为逻辑“1”时,P1和N1管截止,而N2管常导通,输出逻辑值“1”。当输入IN为逻辑“2”时,P1管截止、N1管导通,输出OUT放电到0,输出逻辑值“0”。

图4 基于CNFET的三值反相器

2.2 三值灵敏放大器设计

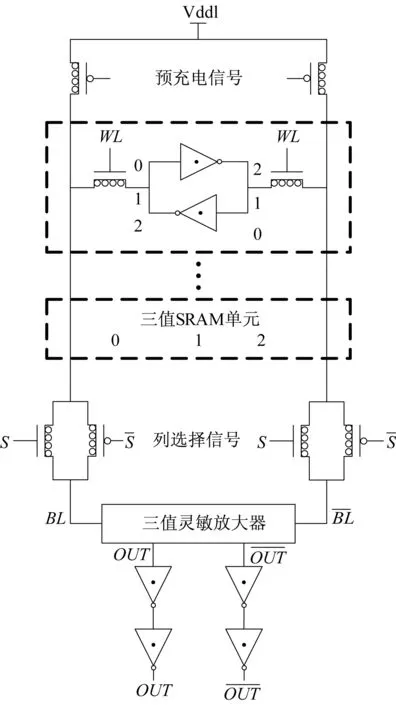

利用交叉耦合的三值反相器作为锁存器来设计三值灵敏放大器,三值灵敏放大器结构如图5所示。

图5 三值灵敏放大器

图6 基于三值灵敏放大器的三值SRAM阵列

3 实验结果与分析

3.1 概述

实验采用斯坦福大学的32 nm CNFET标准模型库[8],利用HSPICE对三值灵敏放大器进行仿真,并从芯片成品率、速度和功耗等方面来评估三值灵敏放大器性能。标准模型库采用的主要参数有:电源电压Vdd=0.9 V,Vddl=0.45 V,CNFET的物理沟道长度Lch=32 nm,扩散到源、漏区碳纳米管掺杂长度分别为Lss=32 nm和Ldd=32 nm,本征碳纳米管区弹道散射自由程长度Lgeff=100 nm,沟道与衬底间单位间距电容Csub=20 pF/m。

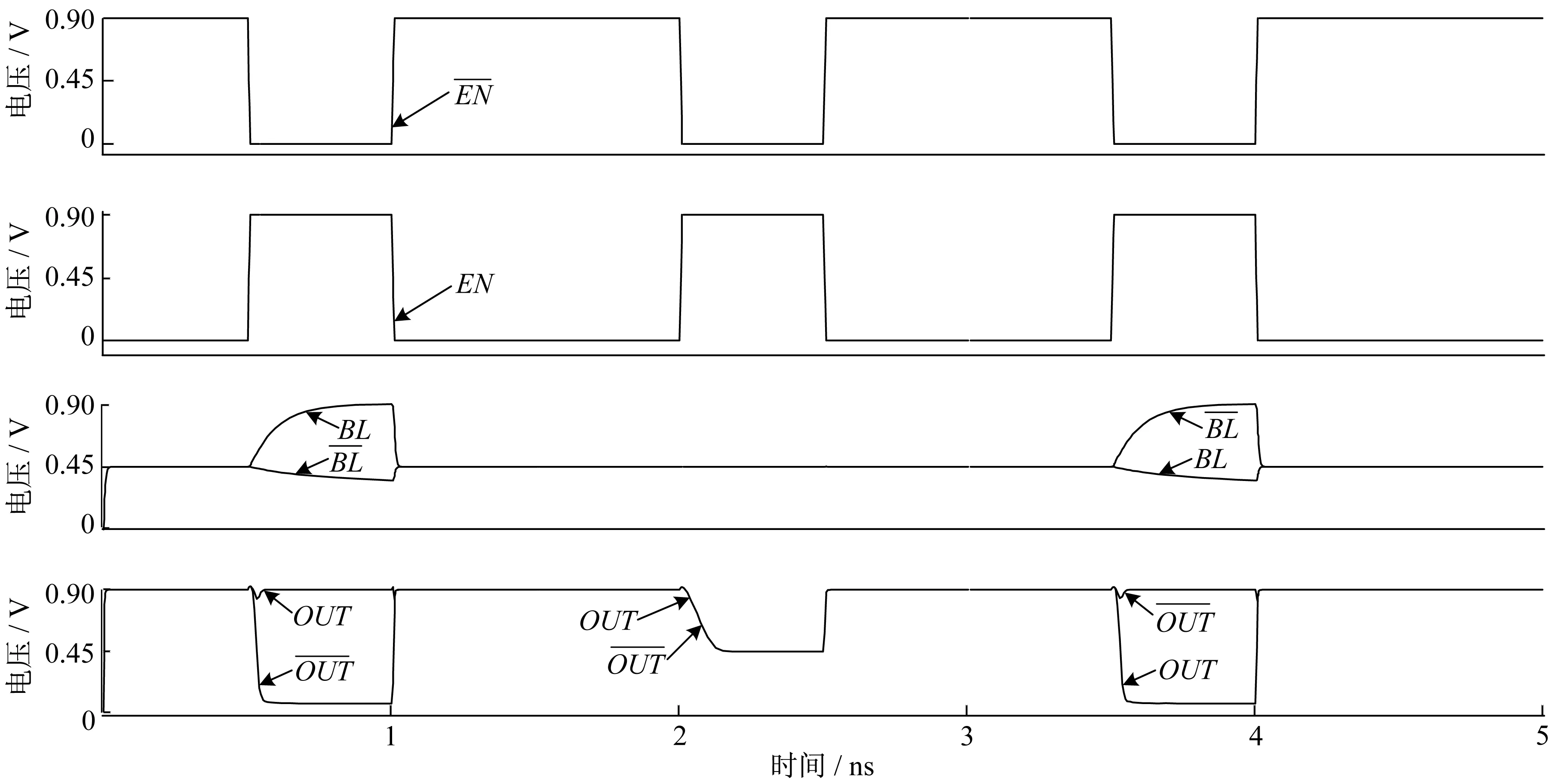

3.2 工作波形、速度及功耗

图7 三值灵敏放大器工作波形

灵敏放大器工艺延时/ps文献[9]150nmCMOS84文献[10]130nmCMOS75文献[11]90nmCMOS90本文32nmCNFET27

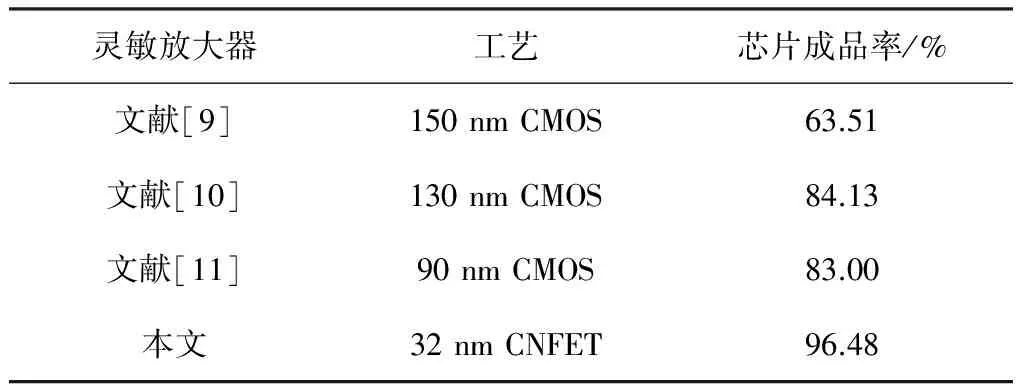

3.3 芯片成品率及稳定性

灵敏放大器芯片成品率是指在一定差分输入电压条件下,大量芯片中能输出正确逻辑值的芯片所占的比例。由于工艺偏差,各CNFET的参数不可能完全相同,因此灵敏放大器芯片成品率受工艺偏差影响。为正确读出存储器中的数据,灵敏放大器芯片成品率的提高显得尤为重要。给定差分输入电压为100 mV,经过10 000次Monte Carlo仿真测得三值灵敏放大器成品率。由表3灵敏放大器芯片成品率的对比可知,相比CMOS工艺的二值灵敏放大器,三值灵敏放大器芯片成品率有明显的提高,高达96.48%。

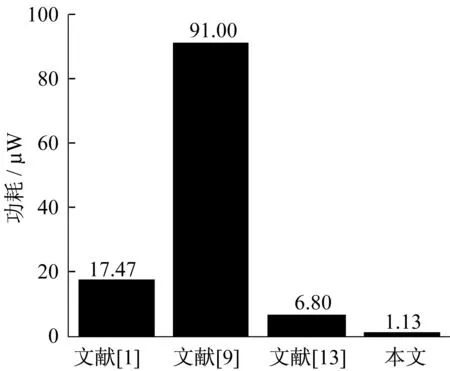

图8 灵敏放大器功耗对比图

在不同温度条件下,芯片成品率也会受到影响,芯片成品率的高低反映灵敏放大器的稳定性。为验证所设计灵敏放大器的稳定性,给定差分输入电压为100 mV,经过10 000次Monte Carlo仿真测量不同温度下(-55 ℃~140 ℃)芯片成品率。从图9可以看出,当温度低于50 ℃时,芯片成品率均高达90%。当温度高于50 ℃时,芯片成品率有所下降,但均高于71%;而文献[10]的成品率变化不大,但成品率较低;可知本文设计的三值灵敏放大器有较好的稳定性。

表3 灵敏放大器芯片成品率对比

图9 不同温度下芯片成品率

4 结 论

本文设计了一种基于CNFET的三值灵敏放大器电路。将交叉耦合的三值反相器作为三值灵敏放大器的锁存器,并将输入输出信号分离,提高了灵敏放大器的工作速度。结合CNFET的优越特性和控制电路技术,降低了灵敏放大器的功耗。通过HSPICE对所设计的三值灵敏放大器在不同温度下进行Monte Carlo仿真,结果表明三值灵敏放大器在-55~140 ℃温度下,其成品率均高于71%,具有较强的稳定性。三值灵敏放大器是三值SRAM电路的补充,对提高三值SRAM电路的性能起到了很大的作用。

[1]TAO Y P,HU W P.Design of sense amplifier in the high speed SRAM[C]//IEEE International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery.USA:IEEE,2015:384-387.

[2]WEI Z K,PENG X H,WANG J H,etal.Novel CMOS SRAM voltage latched sense amplifiers design based on 65 nm technology[C]//IEEE International Conference on Solid-State and Integrated Circuit Technology.USA:IEEE,2015:1-3.

[3]LIN S,KIM Y B,LOMBARDI F.Design of aternary memory cell using CNTFETs[J].IEEE Transactions on Nanotechnology,2012,11(5):1019-1025.

[4]ZHOU Keji,WANG Pengjun,WEN Liang.Design of power balance SRAM for DPA-resistance[J].Journal of Semiconductors,2016,37(4):045002-1-045002-7.

[5]余群龄.基于65纳米SRAM的高速灵敏放大器的设计与实现[D].合肥:安徽大学,2012.

[6]DENG J,WONG H S P.A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application:Part I.Model of the intrinsic channel region[J].IEEE Transactions on Electron Devices,2007,54(12):3186-3194.

[7]唐伟童,汪鹏君,郑雪松.基于CNFET的低功耗三值门电路设计[J].宁波大学学报(理工版),2014,27(3):43-49.

[8]Stanford Nanoelectronics Lab.Stanford CNFET model and schottky barrier CNFET model[EB/OL].[2015-12-18].http://nano.stanford.edu/model.php?id=23.

[9]王艺燃,于宗光,贾泽.一种高速高可靠电压型灵敏放大器设计[J].电子技术应用,2010,36(5):143-147.

[10]WICHT B,NIRSCHL T,SCHMITT-LANDSIEDEL D.Yield andspeed optimization of a latch-type voltage sense amplifier[J].IEEE Journal of Solid-State Circuits,2004,39(7):1148-1158.

[11]ARSLAN U,MCCARTNEY M P,BHARGAVA M,etal.Variation-tolerant SRAM sense-amplifier timing using configurable Replica Bitlines[C]//IEEE Custom Integrated Circuits Conference.USA:IEEE, 2008:415-418.

[12]LI Z,PENG C,LU W,etal.Variation-resilient pipelined timing tracking circuit for SRAM sense amplifier[J].Ieice Electronics Express,2016,13(7):1-6.

[13]CHANDANKHEDE R D,ACHARYA D P,PATRA P K.Design ofhigh speed sense amplifier for SRAM[C]//IEEE International Conference on Advanced Communication Control and Computing Technologies.USA:IEEE,2014:340-343.

Design of High-Speed and Low-Power Ternary Sense Amplifier Based on CNFET

GONG Dao-hui, WANG Peng-jun, KANG Yao-peng, ZHANG Hui-hong

(Institute of Circuits and Systems,Ningbo University,Ningbo 315211,Zhejiang,China)

By researching the structure of Carbon Nanotube Field Effect Transistor (CNFET) and the principle of sense amplifier,a scheme of high-speed and low-power ternary sense amplifier circuit is proposed.In this scheme,the circuit structure of a ternary inverter is analyzed.And then,we use cross-coupled inverters method to implant a ternary latch.To improve the speed of differential signal amplification,the input and output signal separation technique is selected.And also,the working states are controlled by enable signal to reduce the power consumption of ternary sense amplifier circuit.Under Stanford University 32 nm CNFET standard model,HSPICE simulation results show that the designed circuit has correct logic functionality.The chip yield of the circuit is up to 96.48% with strong stability.Comparing with conventional binary CMOS sense amplifier,the proposed circuit increases the speed by 64%,and decreases the power consumption by 83.4%.

carbon nanotube field effect transistor; ternary sense amplifier; chip yield; high-speed and low-power

1006-3080(2017)02-0248-06

10.14135/j.cnki.1006-3080.2017.02.015

2016-09-05

国家自然科学基金(61234002,61474068);浙江省公益性技术应用研究计划项目(2016C31078);宁波市自然科学基金(2015A610107)

龚道辉(1991-),男,硕士生,主要从事多值逻辑电路理论及设计方面的研究。

汪鹏君,wangpengjun@nbu.edu.cn

TN334.3

A