EDA技术在数字电路设计中的应用

2017-04-24武汉工程职业技术学院湖北武汉430080

罗 敏(武汉工程职业技术学院 湖北 武汉:430080)

EDA技术在数字电路设计中的应用

罗 敏

(武汉工程职业技术学院 湖北 武汉:430080)

在数字电路的设计中,竞争-冒险现象都是影响电路稳定性和准确性的重要因素。利用EDA技术的波形仿真,通过理论分析,探讨消除竞争-冒险现象的方法,使学生深入理解数字电路中的竞争-冒险现象,提高教学效果。

数字电路;EDA技术;QuartusⅡ软件;竞争-冒险现象

0 引言

《数字电子技术》课程是高校应用电子、电子信息专业的专业基础课程,其课程的实践性强。当学生在进行复杂的数字电路设计时,经常会出现设计的理论结果和实际电路结果不符合的现象,而引起这种现象的原因往往是数字电路的竞争-冒险现象。在数字电路中,无论是组合逻辑电路还是时序逻辑电路都可能出现竞争-冒险,这种现象将直接影响电路工作的稳定性和准确性,甚至会引起整个数字电子系统的误操作和逻辑紊乱。由于教材一般不会将这个教学内容为重点,学生往往对此认识不够,一旦出现这种情况,学生需要反复的进行试验、修改方案,增加了设计难度。本文通过EDA技术的工具软件QuartusⅡ,对数字电路的输出仿真波形进行分析,来阐述竞争-冒险现象的形成原因并探讨其解决方案。

1 EDA技术简介

EDA技术即电子设计自动化(Electronic Design Automation),在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。EDA技术是在PLD(可编程逻辑器件)的电子设计载体下,通过HDL语言(硬件描述语言)和相关的工具软件(EWB、QuartusⅡ、Matlab等),依托功能强大的计算机系统对电子系统进行的一种逻辑描述及表达,并由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,对特定PLD芯片进行适配编译、逻辑映射和编程下载等工作,以实现电子系统自动化设计。

EDA技术的典型特征是电子设计流程不是自下而上设计,而是自上而下设计。在设计上,EDA技术从电子系统设计的整体思路出发,设计前规划好系统各个部分的结构及相互联系,随后通过EDA技术对系统内的任意硬件功能实现描述,并在可编程的逻辑器件上进行调试,最终对电子系统设计结构得以实现。因此,EDA技术能有效的解决传统电子设计技术的弊端,减少出现故障的几率,使设计效率大幅提高。

2 数字电路中的竞争-冒险现象

2.1 数字电路中的竞争-冒险现象形成的原因

在数字逻辑电路的理论设计时,信号高、低电平的变化都是理想化的。但在实际电路设计中,信号通过数字电路内部的连线和逻辑单元时都有一定的延时,延时的大小与连线的长短和逻辑单元的数目有关,同时与逻辑器件的工作温度、制造工艺、工作电压等条件有关,且信号的高、低电平转换也需要一定的过渡时间。这些因素导致信号的状态改变的时刻不一致称为竞争。由于竞争而引起电路输出信号中出现了非预期信号而产生瞬间错误操作的现象称为冒险。输出端出现的不正确的尖峰脉冲称为毛刺。因此,产生竞争-冒险现象的主要原因就是数字电路内部的延时,导致到达会合点的时间有先有后,从而产生瞬间的错误输出。

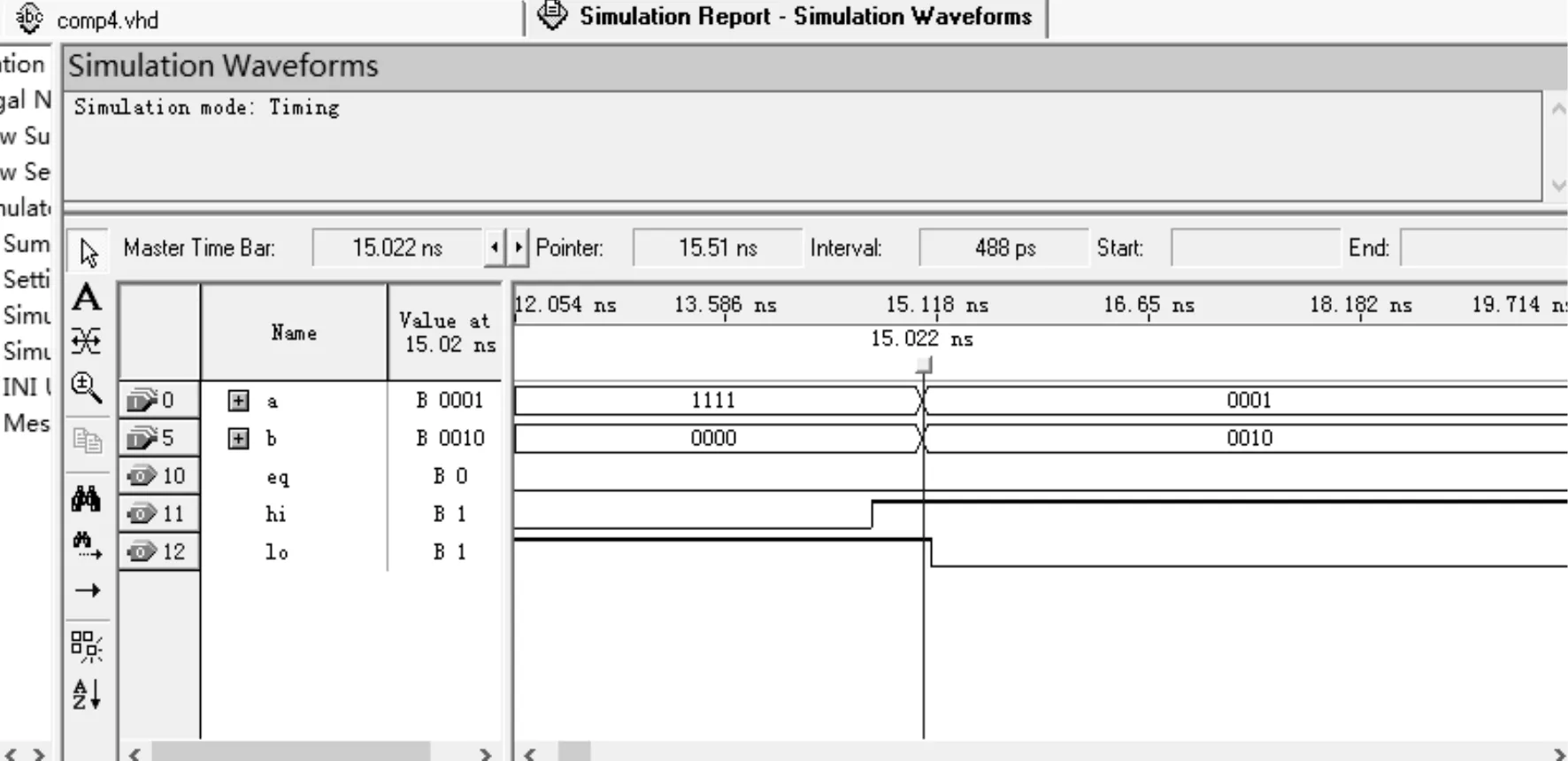

2.2 EDA仿真

本文以数值比较电路为例来说明竞争-冒险现象,其中a和b进行数值比较,如果a>b,则hi 输出为高电平,a library ieee; use ieee.std_logic_1164.all; entity comp4 is port(a,b:in std_logic_vector(3 downto 0); eq,hi,lo:out std_logic); end comp4; architecture comp of comp4 is begin process(a,b) begin if (a>b) then eq<='0'; hi<='1';lo<='0'; elsif (a eq<='0';hi<='0';lo<='1'; elsif (a=b) then eq<='1';hi<='0';lo<='0'; else eq<='0';hi<='0';lo<='0'; end if; end process; end comp; 通过仿真之后得到的仿真波形图如图1所示。从光标处可以看出,当a和b数值发生变化时,输出并没有立即发生变化,即毛刺的存在。 图1 数值比较器仿真波形图 2.3 竞争-冒险的解决方案 2.3.1 采用修改逻辑设计 当电路的输出出现A+A相“或”和A·A相“与”时会产生毛刺,这种毛刺一般通过在输出端加D触发器加以消除。但使用D触发器消除竞争-冒险现象时也会影响到电路的时序状态,所以在设计时要仔细地分析毛刺产生的原因、性质,采用修改电路的逻辑设计来彻底消除。这种方法虽然从根本上消除了毛刺产生的根源,但由于此法必须全面分析和掌握设计电路的工作状态及其转变过程,因此带来了设计的复杂性。 2.3.2 采用时钟同步设计 设计数字电路时,采用时钟同步电路可以大大减少毛刺。由于大多数毛刺一般为几个纳秒,所以只要毛刺不出现在时钟跳变处,毛刺信号就不会对系统造成危害。因此,只要在整个系统中使用同一个时钟,就可以使系统同步达到消除毛刺影响的目的。这种方法操作简单,也常有较好的效果,但要求电路必须工作在统一的时钟脉冲信号下,电路在设计上有一定的局限性。 2.3.3 采用延时同步设计 因为时钟信号在可编程逻辑器件中传递是有延时的,且无法预知时钟跳变沿的精确位置,所以可以考虑采用信号延时同步设计。采用信号延时同步设计必须有2个或2个以上的子模块电路的设计,其原理是在2级信号传递的过程中加1个延时电路,从而保证在下一个模块中读取到的数据是稳定后的数据,即不包含毛刺信号。这里所指的信号延时可以是数据信号的延时,也可以是时钟信号的延时。这种方法输出的结果较为准确,但需要在设计时反复地实验,是最费时的方法。 在数字电路的设计中,竞争-冒险现象都是影响电路稳定性和准确性的重要因素。因此,在数字电路的教学中引入EDA技术可以有效的协助教师对这种现象的讲解,也有利于学生直观深入的理解电路设计过程中理论和实践结果不同的问题,并通过工具软件QuartusⅡ的仿真,采用合理的方法来解决数字电路的竞争-冒险现象。 [1] 阎石.数字电子技术基础[M].北京:高等教育出版社,2006. [2] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2006. [3] 韩芳,张亚.EDA技术在竞争-冒险现象教学中的应用[J].福建电脑,2008,(12):198-199. [4] 陈贞.QuartusⅡ软件中两种仿真结果的分析研究[J].电子技术与软件工程,2016,(14):98-99. (责任编辑:游 涛) Application of EDA to Digital Circuit Design Luo Min (Wuhan engineering Institute,Wuhan 430080,Hub) In designing digital circuit,the race and hazard phenomenon affects its stability and accuracy.The application of Waveform simulation enables students to further understand race and hazard phenomenonthrough theory teaching and discussion.Thus,better teaching effect is achieved. digital circuit;EDA technology;QuartusⅡsoftware;race and hazard 2017-02-16 罗 敏(1983~),女,硕士,讲师.E-mail:45296745@qq.com TN79-4 A 1671-3524(2017)01-0027-02

3 结语