基于二极管技术优化射频集成电路的ESD

2017-04-24廖春连

廖春连,王 健,翟 越

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

基于二极管技术优化射频集成电路的ESD

廖春连,王 健,翟 越

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

在CMOS集成电路设计中,工艺尺寸不断减小、栅氧厚度不断变薄,对ESD提出更高的要求。尤其在射频集成电路中,ESD的寄生电容对射频性能将产生不可忽略的影响。基于二极管正向偏置对ESD电流的泄放能力,通过引入电感和电容对ESD脉冲的精确模拟,通过设计有效的有源RC电源钳位电路,考虑到版图电阻电容寄生对ESD的射频性能的影响,提出3种版图设计,对各种版图进行了仿真,分析ESD和射频性能,提出了最优的版图,满足射频集成电路应用的ESD保护电路。

静电泄放;射频集成电路;二极管;电源钳位

0 引言

随着CMOS集成电路工艺发展,器件尺寸越来越小,结深越来越浅,在先进的工艺制程中,栅氧厚度可能只有几纳米甚至零点几纳米,静电击穿变得越来越容易。

据文献[1]数据统计表明,集成电路失效产品中的37%是由ESD或者EOS(Electrostatic Discharge/Electrical Over Stress)所引起的。静电泄放现象已成为影响CMOS集成电路可靠性的主要原因之一,因此ESD设计在行业内引起普遍关注。所谓的静电泄放(ESD)现象是指当2个带有不同电荷量的物体相互接触时,电荷在2个物体之间发生的电荷转移。集成电路产品通过I/O(输入/输出)引脚与外部相连,当I/O引脚与其接触的物体电势存在差别时,它们之间产生电荷转移,形成较大的电流,可能对芯片造成严重的损伤,所以芯片的I/O需要进行ESD保护。

在低速应用场合中,由ESD引起的寄生对I/O的速率影响并不大,当I/O工作在射频频段,ESD寄生对射频I/O的影响不可忽略,需要对射频I/O进行优化设计。

1 ESD模型

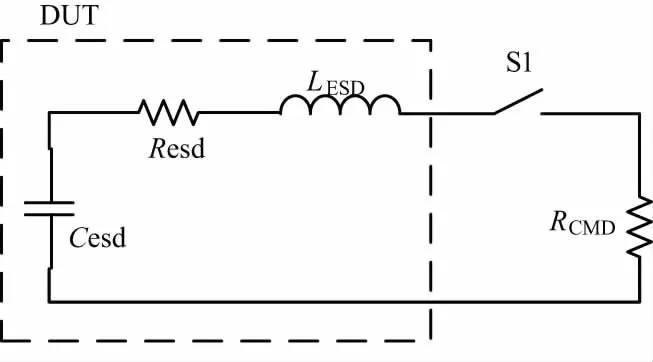

ESD可分为3类模型:① 人体模型(Human Body Model,HBM);② 机器模型(Machine Model,MM);③ 器件充电模型(Charged Device Model,CDM)。这3类模型对集成电路的放电方式不一致,其等效电路也不一样,如图1(a)所示。图中人体的等效电容Cesd为100 pF,人体的等效放电电阻Resd为1 500 Ω,除此之外,CHBM和LESD为人体寄生的串联电容和电感,电容值约为1.5 pF,寄生电感约为75 μH,CB为封装等因素引入的寄生并联电容,约为几个皮法。

机器模型与人体模型比较类似,等效模型电路如图1(b)所示,但等效电阻(Resd)比人体等效电阻小得多,只有数十欧姆,等效电容调整到200 pF,其放电过程短,由于机器上寄生电感和电容耦合,其放电波形出现振荡。当前一般不使用机器模型,只有在早期器件的手册中才会看到。器件充电模型指带电被测器件,当它接地瞬间,电荷会从器件泄放到地,其等效电路图如图1(c)所示。把器件等效成RCL串联网络,根据不同的器件封装类型和CMD标准,瞬间电流峰值从5~15 Amp/kV,上升时间从200~500 ps。

(a) ESD人体模型

(b) ESD机器模型

(c) ESD器件充电模型图1 ESD等效电路模型

表1对比了HBM、MM和CDM 3种模型的ESD脉冲波形特性和寄生参数。其中MM和CDM模型寄生电阻小,放电时间短,会产生很大的电流脉冲。因此,各模型的ESD等级定义不一致,从Okey、Safe到Super,HBM电压等级为2 000 V、4 000 V和10 000 V;MM电压等级为200 V、400 V和1 000 V;CDM电压等级为1 000 V、1 500 V和2 000 V。

表1 ESD模型比较

其中HBM是目前半导体业界最常用的模型,也是集成电路在使用过程中经常遇到的静电放电事件。人体通过摩擦会积累静电荷,当未实施任何保护措施时,人体积累的静电荷就会通过手持设备进入半导体器件,对器件进行放电。在人体上积累的电荷相当于100 pF电容上电荷,一个2 kV的电压相当于电量为2×10-7C,这些电量通过一个1 500 Ω的电阻对集成电路进行放电,瞬间电量峰值将达到1.33 Amp(每1 000 V电压对应电路未0.66 Amp),放电上升时间为2~10 ns,维持时间约为150 ns。这个瞬时电流脉冲经半导体器件时很容易在内部累积热量,从而导致其失效。

为了衡量器件在HBM模式下的ESD的能力等级,行业内制定了相应的HBM测试标准,国际上主要有JEDEC STANDARD (EIA/JESD22-A114)[3]标为GJB 548B-2005《微电子器件试验方法和程序Test methods and procedures for microelectronic device》[4],本文主要基于GJB研究射频集成电路ESD设计优化技术。在该标准中规定了ESD分级试验电流波形,如图2所示。

图2 HMB模型ESD电流脉冲波形

图2中,tr和td分别为上升时间和延迟时间。根据GJB规定ESD等级共分7级,对应的失效电压如表2所示,本文设计目标是在S波段设计ESD等级为2级的射频集成电路。

表2 器件HMB模型ESD失效阈值分级

2 ESD方案设计

ESD脉冲打击方式分别有以下6种:

① PS:VSS接地,正ESD脉冲加入I/O引脚,对VSS放电,VDD与其他引脚浮空;

② NS:VSS接地,负ESD脉冲加入I/O引脚,对VSS放电,VDD与其他引脚浮空;

③ PD:VDD接地,正ESD脉冲加入I/O引脚,对VDD放电,VSS与其他引脚浮空;

④ ND:VDD接地,负ESD脉冲加入I/O引脚,对VDD放电,VSS与其他引脚浮空;

⑤ Pin-to-Pin Positive-mode:被测引脚接正ESD脉冲,其他I/O引脚接地,VDD和VSS浮空;

⑥ Pin-to-Pin Negative-mode:被测引脚接负ESD脉冲,其他I/O引脚接地,VDD和VSS浮空。

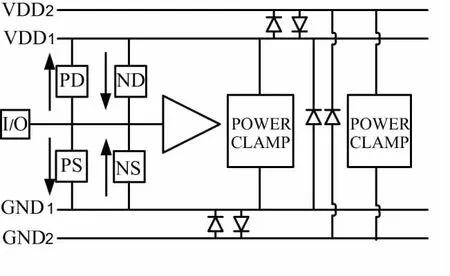

满足6种ESD打击方式保护结构如图3所示。

图3 多电源域整体ESD方案

因此芯片中的每一个I/O引脚都需要提供4个方向上的ESD保护。通常射频集成电路包含多种功能,为使各功能模块之间相互隔离噪声,一般采用多电源域方案[5]。在电源不同电源域之间加入隔离二极管,既能保证隔离噪声,又能形成良好的ESD电路通路。每组电源地之间需要提供POWER CLAMP和反向连接二极管,分别提供电源到地和地到电源的ESD通路。图中VDD2和VDD1为相同的电源电压,如果电压相差较大,可以多使用几个二极管串联,但这会在ESD事件发生时2个电源域之间压降升高,影响ESD性能。

射频集成电路设计ESD时[6],需要考虑保护电路寄生电容对电路性能的影响。当频率低于1 GHz时,传统的数字集成电路ESD方案就可以直接使用;当频率从1~5 GHz时,需要在对射频性能影响可接受的范围内进行优化ESD寄生电容;当频率从5~10 GHz时[7],需要对射频电路和ESD保护电路进行协同设计,利用电感使它与寄生电容在合适频段产生谐振;当频率超过10 GHz时,需要在片外进行ESD保护设计[8]。

I/O引脚的ESD保护有多种方案,低阈值可控硅技术(LVTSCR),栅极接地NMOS(GGNMOS)技术和二极管技术(diode)。3种技术各有特点,就电流能力而论,LVTSCR技术电流泄放能力为50 mA/μm,GGNMOS为8~10 mA/μm,二极管为50 mA/μm。因此,在射频集成电路中[9],一般采取LVTSCR和二极管技术,以降低过大的ESD寄生电容对射频性能的影响。但LVTSCR技术难以控制开启电压,需要准确的工艺参数进行工艺仿真,求解电磁场,才能有效设计ESD保护电路。基于以上的研究,本文基于二极管加有源POWER CLAMP方案优化ESD电容方法实现射频ESD防护的设计。

本文基于SMIC 0.13 μmRF CMOS工艺,研究L波段射频集成电路ESD保护设计。包含2组电源分别为1.2 V和3.3 V。I/O引脚ESD电路如图4所示。该结构为二极管加POWER CLAMP结构。M1到M6组成POWER CLAMP。M1到M3为PMOS管电阻,C1为NMOS管电容,M4和M5组成反相器,M6管为ESD电流泄放管,pdio33和ndio33为ESD二极管。

图4 ESD结构

当PAD出现NS或者PD脉冲时,ESD电流直接通过正偏到地或电源;当PAD上出现PS脉冲时,ESD电流通过pdio33、M6到地,形成回路保护内部器件;当PAD上或者ND脉冲时,ESD电流通过M6、ndio33形成电流回路。

由于POWER CLAMP是通过RC时间常数来判断是否是ESD事件还是正常芯片上电,所以RC时间常数大于ESD脉冲上升时间,小于正常上电时间[10]。在HBM模型中ESD上升时间约几ns,正常上电时间约几ms,所以RC时间常数通常设置在μs级[11]。本设计中采用MOS管的沟道电阻和栅源电容作为电阻和电容,能有效的节省版图面积。对RC时间常数进行仿真,结果如图5所示,带宽为670 kHz,对应的时间常数为1.49 μs。

图5 Power clamp 时间常数仿真

3 POWER CLAMP ESD仿真

电源地之间的POWER CLAMP采用RC触发NMOS管实现ESD保护结构的二极管包括多Pdio和Ndio二极管。对二极管和POWER CLAMP仿真前,需要模拟HBM脉冲,脉冲模拟的是否准确,决定设计的成败。本文在ESD等效电路的基础上加入寄生电容C2和寄生电感L1,如图6所示。C2和L1值的大小影响ESD脉冲的上升时间、最高电流值和下降时间等参数。

图6 ESD脉冲模拟电路

采用该模拟脉冲发生电路产生的ESD仿真波形如图7所示。电流峰值1.33A mp,上升时间6.28 ns,下降时间145 ns,与相关标准一致。但ESD上升时间太快时,会导致能量迅速释放,导致器件击穿。

按照图7模拟的ESD脉冲,对图4的ESD电路进行ESD打击仿真,图8为PD、PS打击方式,图9为ND、NS打击方式,图10为IO到IO的打击方式。图8和图9打击方式比较类似,所以仿真结果基本一致。直接对电源地放到的PD模式和NS模式,由于ESD电流回路经过二极管,所以压降比较小,约1.8 V,比起6 V的击穿电压,这2种打击方式设计余量较大。而PS和ND模式,ESD电流回路经过二极管和大尺寸的NMOS管,所以压降较大,约4.8 V,只有1.2 V的设计余量,但仍满足设计要求。

图7 人体模型2 000V ESD脉冲

图8 人体模型PD和PS仿真波形

图9 人体模型ND和NS仿真波形

图10为IO到IO的打击方式,由于这种打击方式ESD电流需要经过2个二极管和1个大尺寸的NMOS管,所以这种方式ESD压降最大,对设计的要求较高。通过优化二极管面积,调整POWER CLAMP的时间参数,在传统的IO FILLER之间加入ESD泄放路径,最终使得设计仍然有0.5 V的设计余量,满足要求。

图10 人体模型IO到IO仿真波形

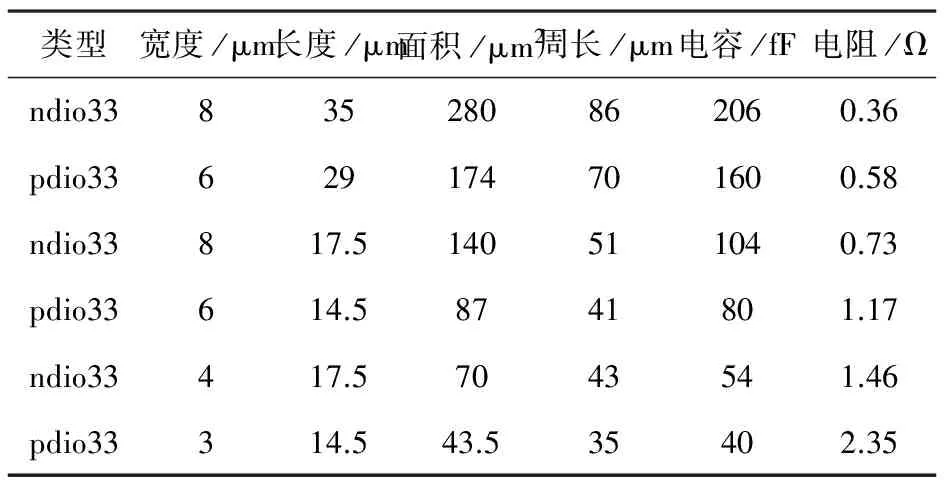

二极管的设计需要触发电压小,正常工作漏电流小,ESD承受能力强,导通电阻小,面积小的特点。由于采用的防护方案都是双二极管加POWER CLAMP的设计,需要二极管正向导通电阻小才能达到ESD防护失效电流高的情况,对二极管的优化主要是版图设计,包括参数尺寸、金属布线以及二极管的形状。

4 ESD寄生参数优化

基于射频电路设计ESD,不仅需要考虑ESD电流泄放能力,而且需要对版图进行优化,减少寄生电容[12]。对于0.13 μm CMOS工艺,其栅氧层厚度约2.6 nm,栅氧击穿电压(BVox)约6 V。为实现2 000 V(对应电流为1.3 A)的ESD保护电路,整个ESD保护电路的电阻应该小于Rmax,Rmax计算公式如下:

Rmax=BVox/IESD,

(1)

式中,BVox为6 V,IESD为1.33A,Rmax为4.5 Ω。

表3 各种尺寸二极管寄生参数比较

pdio33反偏电容从180 fF(反偏电压0.5 V),到135 fF(反偏电压2.0 V),反偏电压增大,pn结变宽,结电容变小。ndio33反偏电容从227 fF(反偏电压0.5 V),到182 fF(反偏电压2.0 V),反偏电压增大,pn结变宽,结电容变小。

版图结构如图11所示,寄生电容:C(到衬底)为254 fF,集中在图中标注为A的区域;PAD的寄生电容特别大,占主要部分;CC电容包括CC到地71 fF,CC到电源91 fF。总的寄生电容为416 fF。

图11 二极管寄生

版图优化方法一,如图12所示,去掉PAD下M2、M3、M4等3层金属,M1通过CT与衬底连接,寄生电容:C(到衬底)为162 fF,集中在图中钝化开口方块中;PAD的寄生电容特别大,占主要部分;CC电容包括CC到地71 fF,CC到电源91 fF。总的寄生电容为324 fF。

图12 焊盘结构

版图优化方法二,去掉PAD下M2、M3、M4等3层金属,M1通过CT与衬底连接。PAD至内部的连线包括金属2/3/43层,优化方法2中去掉第2层的连接线,以优化寄生电容。寄生电容:C(到衬底)为134 fF,CC电容包括CC到地53 fF,CC到电源62 fF。总的寄生电容为249 fF。

版图优化方法三,去掉PAD下M2、M3、M4等3层金属,M1通过CT与衬底连接。PAD至内部的连线包括金属2/3/4共3层,优化方法2中去掉第2层的连接线,同事减小PAD的大小,从80×80减小到59×57,以优化寄生电容。寄生电容:C(到衬底)为104 fF,CC电容包括CC到地53 fF,CC到电源62 fF。总的寄生电容为219 fF。

5 结束语

在对基于二极管的射频集成电路ESD方案设计中,比较GGMOS、SCR和二极管的静电泄放能力,在没有代工厂工艺参数的条件下采用二极管和有源POWER CLAMP设计了满足HBM2000V的ESD保护电路,通过模拟ESD脉冲波形对各种ESD模式进行了SPICE仿真,并分析版图寄生来源,提出了版图优化方法,使总的寄生电容优化到219 fF,有效地降低了ESD电路对射频性能的影响。

[1] Amerasekera A,Duwury C.ESD in Silicon Integrated Circuits-secod Edition[M].New York:John Wiley&Sons,Ltd,2002.

[2] Wang A Z H.On Chip ESD Protection Design for Integrated Circuits:An IC Design Perspective[M].US:Springer,2002.

[3] JEDEC STANDARD,JESD22-A114D (revision of JESD22-A114-C.01) [S],2006.

[4] GJB 548B-2005,微电子器件试验方法和程序[S],2005.

[5] 杜晓阳.CMOS射频集成电路片上ESD防护研究 [D].杭州:浙江大学,2009.

[6] 尚晓辉,宋晓辉,张 玉.阵列抗干扰射频接收机设计[J].无线电工程,2015,45(5):43-45.

[7] 邹 敏,纪学军.射频自适应干扰抵消系统的分析与设计[J].无线电工程,2011,41(4):39-41.

[8] Voldman S H.Inter Science,ESD:RF Technology and Circuits[M].New York:John Wiley&Sons,Ltd,2006.

[9] 殷素杰,杜 浩.射频功率放大器的宽带匹配设计[J].无线电工程2013,43(2):48-51.

[10] 邱相晗,宋 鹏,齐建中.无线数据链系统地面射频收发技术的研究[J].无线电工程,2015,45(9):49-52.

[11] 刘长龙,陈 燕,程理丽.一种射频标签芯片的数模混合信号仿真方法[J].无线电通信技术,2015,41(4):80-83.

[12] 徐 谦,刘太君,叶 焱,等.可重构多波段射频功率放大器设计[J].无线电通信技术,2014,40(3):61-64.

Optimization of ESD in RF IC Based on Diode Technology

LIAO Chun-lian ,WANG Jian,ZHAI Yue

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

In CMOS integrated circuits design,the process geometries continue to decrease,and the thickness of gate oxide gets thinner,which puts forward higher requirements for ESD.Especially in RF integrated circuits,parasitic capacitance of ESD on the RF performance will have a negligible impact.Based on the current discharge capacity of the forward bias diode,inductance and capacitance are introduced to get accurate simulation of ESD pulses.Effective active RC power clamp circuit is designed,in consideration of the influence of layout resistance capacitance parasitic on the RF performance of ESD. Three layout designs are proposed,and their simulations are performed.Analysis of the ESD and RF performance is provided and an optimal layout is presented.The ESD protection circuit can meet the application for the RF integrated circuit.

Electrostatic discharge;radio frequency integrated circuit;diode;power clamp

10.3969/j.issn.1003-3114.2017.03.21

廖春连,王 健,翟 越. 基于二极管技术优化射频集成电路的ESD [J].无线电通信技术,2017,43(3):85-90.

[LIAO Chunlian,WANG Jian, ZHAI Yue .Optimization of ESD in RF IC Based on Diode Technology [J].Radio Communications Technology, 2017,43(3):85-90.]

2016-12-15

国家重大专项(2013ZX03006006)

廖春连(1982—),男,工程师,主要研究方向:射频集成电路设计。王 健(1988—),男,助理工程师,主要研究方向:集成电路版图设计。

TN4

A

1003-3114(2017)03-85-6