一种FPGA智能加载和远程更新的实现方法

2017-04-24贾钢

贾 钢

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

一种FPGA智能加载和远程更新的实现方法

贾 钢

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

由于FPGA具有掉电易失性,系统每次启动都需要对其进行配置;此外,某些系统在出厂后需要进行升级维护,这就需要对FPGA的配置镜像进行更新。针对这种需求,提出了一种新的FPGA智能加载和远程更新的实现方案。系统在Quartus II的SOPC环境下开发,将Nios II处理器、Mac核、高速收发器及Remote-Update模块集成在FPGA片内,不需要片外的CPU或CPLD配合,FPGA独立、智能地完成镜像的更新和加载。实验证明该方案可行,且系统稳定、可靠。

智能加载;远程更新;SOPC;Nios II

0 引言

现在越来越多的系统尤其是小型嵌入式系统需要远程升级功能,对FPGA也要求具备远程更新和配置的能力。以往一些常用的方法是用CPU+FLASH、CPLD+FLASH[1]或CPU+CPLD+FLASH[2]等方式来实现,用这些方法来控制远程更新的实现基本上都需要使用FPGA之外的芯片,其缺点就是增加了成本和设计的复杂度,耗费印制板空间,增加功耗。

本系统采用了FPGA内嵌的Nios II处理器[3]和可参数化的千兆以太网IPcore解决方案[4],在Altera公司的Arria V GX芯片上实现[5]。处理器和以太网网卡功能都在FPGA内部实现,省去了外部CPU和网卡芯片等器件,减小了板卡的布局空间和成本。

1 系统构成

实现FPGA的远程更新要求系统具备以太网的功能,系统不使用除FPGA片外任何的CPU,利用Quartus II的SOPC环境[6]搭建Nios II处理器电路,向其移植Lwip网络协议栈[7]并开发网口驱动程序。

系统的硬件电路主要由FPGA、DDR3和EPCQ组成。通过Quartus II的SOPC开发环境,生成Nios II处理器[8]、以太网模块、高速收发器模块、EPCQ控制器和Remote-Update模块,并通过Avalon总线进行连接[9]。高速收发器使用SGMII接口,通过PHY芯片与网络连接[10]。同时EPCQ控制器与Remote-Update模块连接,用户逻辑介于Nios II和Remote-Update模块之间,用于两者接口的适配。Nios II下发指令控制EPCQ控制器读取EPCQ不同地址段上的镜像,并通过Remote-Update模块获取EPCQ内镜像的状态信息,完成对FPGA的智能加载[11]。系统硬件组成框图如图1所示。

图1 系统结构示意图

2 软件设计

2.1 加载程序设计流程

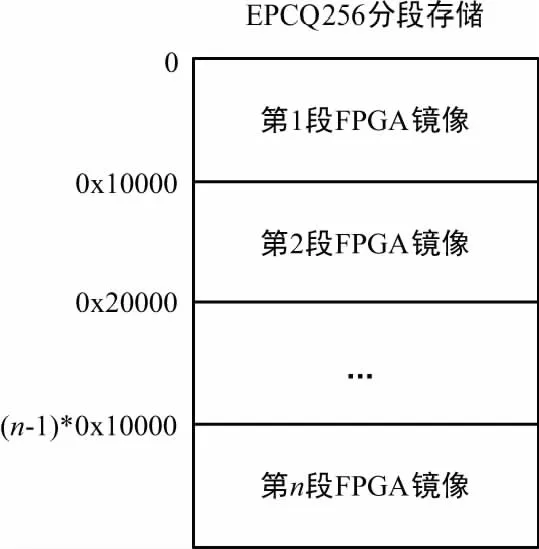

FPGA启动模式采用AS模式[12]。将EPCQ平均分成多个空间,即分段存放,分别存储不同的FPGA镜像,第一段镜像默认从0地址开始,称为原始镜像,启动地址非0的镜像统称为用户镜像。如图2所示,将EPCQ器件分割成了若干段。但由于越是高端型号的FPGA镜像越大,所以要选择合适的存储芯片。EPCQ256器件针对Arria V GX型号通常只能分成2段或者3段[13]。如果想要存储更多的镜像就要使用容量更大的并行总线接口Flash芯片[14]。

图2 EPCQ分段存储示意图

FPGA启动后,默认加载EPCQ内的原始镜像,随后原始镜像会读取启动原因寄存器(该寄存器为Remote-Update模块状态寄存器的一段)来获取此次启动的原因,当原因为上电启动时,便开始向用户镜像跳转。如果加载用户镜像成功,说明用户镜像完整正确,FPGA驻留于用户镜像;如果用户镜像缺失,FPGA重新加载原始镜像,随后读取启动原因寄存器,获取上一次加载用户镜像失败的原因,然后尝试加载另一段用户镜像。如果无可用的用户镜像,FPGA便驻留在原始镜像[15]。

为了保证系统的稳定性和可靠性,原始镜像在向用户镜像跳转时打开看门狗定时器,用户镜像加载完成后来定时清理看门狗。如果看门狗定时器超时,则FPGA立即返回原始镜像。

由此可以看出,EPCQ内必须要有一个可用的原始镜像,这样便能保证FPGA不瘫痪,并随时可以通过远程更新功能更新用户镜像。因为在远程更新的过程中可能会出现写入EPCQ的镜像不完整或者镜像不匹配的问题,远程更新时尽可能不要更新原始镜像,以保证FPGA免于因为没有可用的镜像而导致无法启动。加载流程如图3所示。

图3 加载程序设计流程图

2.2 更新程序设计流程

当FPGA驻留在原始镜像时,可以触发FPGA的远程更新。使用Eclipse的命令行工具,通过sof2flash命令将FPGA的sof文件转换成flash格式。

在上位机打开tftp服务器工具,并设置好超时时间和重传次数。当得到系统的更新请求后,上位机把该文件通过tftp协议传输给Nios II。Nios II的应用程序在接收文件过程中会依据flash文件的格式进行校验,接收到完整的flash文件后,再把该文件写入到EPCQ中。如果传输过程中出现错误导致校验失败或者文件传输超时,系统将自动放弃此次更新。更新程序设计流程如图4所示。

镜像更新成功后,NiosII的应用程序会向用户发送更新成功的消息,何时加载该用户镜像则由用户根据需要来决定。

图4 更新程序设计流程图

3 系统的实现验证

为了能够观察不同镜像之间的转换,把EPCQ256分成2段,分别存储原始镜像和一个用户镜像。原始镜像点亮实验板前面板蓝色LED,用户镜像则点亮实验板前面板黄色LED。

通过Quartus II的JTAG工具将FPGA的原始镜像和用户镜像依次烧录到EPCQ256中。目标系统重启上电,板卡前面板蓝色LED常亮一段时间后灭掉,同时黄色LED开始点亮,说明原始镜像在运行不久后便向用户镜像跳转;当擦除用户镜像后,目标系统重启上电,板卡前面板的蓝色LED常亮一断时间后灭掉,然后再次常亮,而黄色LED始终未亮。说明原始镜像向用户镜像跳转失败,再次返回并驻留在原始镜像。智能加载功能已经实现。

上位机打开tftp服务器工具和网络调试助手并正确设置,发送ICMP请求给目标系统,得到目标系统的ICMP响应,说明此时的网络是连通的。通过网络调试助手向目标系统发送更新FPGA用户镜像命令,目标系统接收后发送tftp文件下载请求,文件进入传输过程,tftp服务器弹出下载进度条。文件传输完毕后网络调试助手会收到来自目标系统的下载完成消息,而且tftp服务器也会提示文件下载完成。此时重启目标系统发现前面板蓝色LED常亮一段时间灭掉后,黄色LED开始常亮,现象与用JTAG工具下载用户镜像一致。说明远程更新FPGA镜像成功。

4 结束语

实验表明,整个系统结构简单,工作可靠。系统利用Nios II内嵌处理器配合Remote-Update模块实现对存储在EPCQ内多个镜像的选择性加载,并通过FPGA内部实现的SGMII接口连通网络,从远端计算机下载新的FPGA镜像。系统最大的优点是结构简单、可移植性强,便于后期设备的调试、维护和升级,使用Nios II软核来控制的FPGA智能加载和远程更新具有广阔的应用前景。

[1] 杨金孝,郭德春,张永波,等.基于串口通信的FPGA配置控制方法及实现[J].计算机测量与控制,2011,19(4):848-850.

[2] 徐新民,洪 波.改进的FPP方式FPGA配置电路及其应用[J] .电子技术,2004,31(11):27-29.

[3] 田青峰,卢泳兵,刘志鹏.NIOS在网络通信系统中的应用[J].无线电工程,2013,43(5):10-12,41.

[4] Triple Speed Ethernet Megacore Function User guide[EB/OL].http:∥ www.altera.com,2008.

[5] Arria V Device Handbook[EB/OL].http:∥www.altera.com,2012.

[6] 李兰英.Nios II嵌入式软核-SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[7] 杨 晔.实时操作系统μC/OS-II下TCP/IP 协议栈的实现[J].单片机与嵌入式系统应用,2003(7):80-83.

[8] Nios II Processor Reference Handbook[EB/OL].http:∥www.altera.com,2009.

[9] Avalon Interface Specifications[EB/OL].http:∥www.altera.com,2011.

[10]Sgmii Interface Implementatin Using soft-CDR Mode of Stratix iii Devices[EB/OL] .http:∥www.altera.com,2011.

[11]ALTREMOTE-UPDATE Megafunction[EB/OL].http:∥www.altera.com,2013.

[12]Serial Configuration Devices Data Sheet[EB/OL].http:∥www.altera.com,2009.

[13]Quad-Serial Configuration (EPCQ) Devices Datasheet[EB/OL].http:∥www.altera.com,2012.

[14]Cyclone III Active Parallel Remote System Upgrade Reference Design[EB/OL].http:∥www.altera.com,2009.

[15]Remote System Upgrade with Cyclone III Device[EB/OL].http:∥www.altera.com,2009.

An Implementation of FPGA Intelligent Load and Remote Update

JIA Gang

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

Due to the volatile nature of FPGA,every time system starts up,it’s required to configure FPGA.In addition,some systems needs to be upgraded to improve the system performance usually after leaving the factory,this requires FPGA’image can be updated at any time.In view of this demand,the article puts forward a new method that FPGA has the function of intelligent load and remote update.The system is developed in SOPC environment,and integrates Nios II,mac,transceiver and Remote-Update ipcore in FPGA chip.No processor or CPLD is required outside FPGA,the FPGA loads and updates the image intelligently and independently.Experimental results show that the method is feasible and the system is stable and reliable.

intelligent load;remote update;SOPC;Nios II

10.3969/j.issn.1003-3114.2017.03.06

贾 钢.一种FPGA智能加载和远程更新的实现方法[J].无线电通信技术,2017,43(3):27-29.[JIA Gang.An Implementation of FPGA Intelligent Load and Remote Update [J].Radio Communications Technology,2017,43(3):27-29.]

2016-12-14

国家部委基金资助项目

贾 钢(1984—), 男,工程师,硕士,主要研究方向:卫星移动通信。

TN911

A

1003-3114(2017)03-27-3