FPGA在惯导脉冲输出信号测量系统中的实现

2017-04-21周航

周 航

(西安建筑科技大学 信息与控制工程学院,陕西 西安 710055)

FPGA在惯导脉冲输出信号测量系统中的实现

周 航

(西安建筑科技大学 信息与控制工程学院,陕西 西安 710055)

针对惯导脉冲数据测量存在测试流程自动化程度低、脉冲计数准确性差等问题,文中基于FPGA平台,采用有限状态机技术实现了阈值滤波的功能,利用直接脉冲计数法和FIFO存储等技术,解决了脉冲计数以及测量系统内部数据传输速率不一致的问题。同时采用虚拟仪器技术,通过LabVIEW平台实现了数据自动处理的功能。经过实验验证,该测量系统能够实现准确脉冲计数,将相对脉冲计数误差控制在 以内,并且能够对数据自动采集处理,提高了测量系统的自动化程度。

惯导脉冲;FPGA; LabVIEW ;准确性

惯性导航系统具有不受外界干扰、不对外发射信号、能够独立自主的特点,可以根据用户的具体要求实现导航方式[1]。随着惯性导航在军事、商业等领域的不断发展,其应用范围也在不断的扩展。惯性导航的应用范围从原来的火箭、导弹、船舶、舰艇等,现已扩展到导航制导、航天探测、航天卫星等方面[2-5]。惯导系统中的陀螺仪和加速度计决定了惯导的方位和速度两个重要的导航参数[6-7]。加速度计和陀螺仪的输出是电压和电流,容易受到干扰,因此需要经过V/F、I/F将电压和电流信号转换为脉冲信号再进行测量[8]。

目前,国内惯导脉冲测量系统存在以下不足:(1)测量过程靠手工操作记录,自动化程度不高,不能满足当前形势自动化测量的需求[9-10];(2)由于测量系统复杂、系统性设计和数据采集与处理准确性低[11-12],容易造成较大的误差,难以实现测量系统准确度高的要求。惯导脉冲输出的测量是影响惯性导航系统准确定位的最主要因素之一,如果惯导脉冲输出的测量不准确,有可能对惯性导航系统造成严重后果,形成一定损失[13-15]。所以在惯性导航系统中,设计出一套能够对惯导脉冲输出进行准确测量,并且自动化程度高的系统。

1 系统整体设计

本测量系统主要包括两大部分,分别为脉冲信号处理以及上位机。其中阈值滤波、脉冲计数以及FIFO存储是在FPGA内部实现。RS232是上位机与下位机通信交互的枢纽。惯导脉冲输出的状态信息数据首先经过脉冲信号处理电路,然后在FPGA内部对接受的脉冲数据进行数据处理,并通过RS232上传到上位机,在上位机中对脉冲数据进行解帧、显示与存储。系统框架如图1所示。

图1 系统框架图

2 FPGA内部逻辑电路设计

2.1 脉冲计数模块

脉冲计数模块的设计流程如图2所示。

图2 脉冲计数模块设计流程图

对该脉冲计数模块进行仿真测试,编写好模块,再对其进行仿真。在仿真中,只在第1路模拟了脉冲的方波信号,得到仿真结果波形如图3所示。

图3 脉冲计数仿真波形图

2.2 阈值滤波模块

基于有限状态机,本文在FPGA内部提出了一种阈值滤波的设计方案。在每个通道设置一个滤波器,这样每个通道都可以对干扰信号进行滤除。有限状态机可以稳定控制系统的状态,测量精确,保证系统的准确性,对高频干扰信号能够起到很好的滤除作用。阈值滤波器的状态机由3个状态组成。如图3所示为阈值滤波状态机图。

图4 阈值滤波有限状态机

State0当输入信号为0时,输出信号也为0,State0中不改变输入信号的状态。当系统上电复位时,系统就进入了State0。如果在State0中,系统的输入信号突然发生跳变,从0跳到1,那么系统就进入State1。

State1该状态中有一个计数器,是20位的,系统时钟为20 MHz,那么该计数器的计数周期为50 ns,也就是每隔50 ns加1。系统从State0中检测到输入由低电平跳变到高电平,计数器从零开始计数,计数的个数和计数的周期相乘,可以得到高电平状态经历的时间,直到这个时间和滤波设置时间相等。此时系统再次对输入信号的电平进行检测。如果这时候输入为低电平,那么系统跳转进入State0;如果输入为高电平,那么系统跳转进入State2。

State2当状态机的输入信号是高电平时,那么状态机的输出信号也为高电平。State2中不改变输入信号的状态。如果在State2中,输入信号从高电平突变到低电平,那么系统进入State1。输入信号从高电平突变到低电平,计数器从零开始计数,直到低电平时间和滤波设置时间相等,则再次对输入信号的电平进行检测。

在Quartus Ⅱ开发环境中描述阈值滤波模块的有限状态机,本文使用的是Veirlog HDL语言。然后对该模块进行RTL级仿真,仿真图如图5所示。

图5 阈值滤波滤除干扰仿真图

2.3 数据存储模块

该测量系统采用的是RS232通信作为上位机与下位机的数据传输枢纽,由于RS232通信方式的传输速率和FPGA内部脉冲信号数据采集速率不一致,有可能导致脉冲信号数据的丢帧、重复、错位等问题。这种情况会造成脉冲数据的准确性、有效性及可靠性。在Quartus Ⅱ环境中,设计一个深度为16的FIFO存储,其FIFO配置如图6所示。

图6 FIFO配置

设计一个计数器,用来计算存储FIFO中还没有读取的数据个数,计算FIFO存储中未读取数据个数是通过求读写指针之差来实现的。如果未读取的数据个数为0,表示FIFO存储中没有数据,FIFO已空。如果未读取的数据个数为16,即FIFO存储的深度值,表示FIFO存储中数据已满。根据上述的读写操作方式可以得到FIFO存储输出的空状态和满状态值,然后使用空状态和满状态值分别控制上一级模块和下一级模块的输入和输出。

2.4 串口模块

串口设计分为3个模块实现,分别为数据接收模块、数据发送模块以及选择波特率模块,数据发送模块在数据接收模块接收完一个完整的数据帧后启动,然后将接收到的数据发送回给对方,其中的传输速率由选择波特率模块产生。其中,选择波特率模块的代码如下:

module select_speed(clk,rst_n,start,send_sig);

input clk; ∥系统时钟信号,20 MHz

input rst_n; ∥复位信号,低电平有效

input start; ∥波特率计数器启动信号,高电平有效

output send_sig; ∥发送数据标志位,高电平有效

reg[12:0] cnt; ∥计数器分频

reg bps_sig; ∥波特率数据改变标志位

reg[2:0] uart_chos; ∥ uart波特率选择寄存器

always @ (posedge clk or negedge rst_n)

if(!rst_n) cnt <= 13'd0;

else if(cnt == 2604) cnt <= 13'd0;∥波特率计数溢出后清零.2604波特率为9600时的分频计数值

else if(start) cnt <= cnt+1'b1; ∥波特率时钟计数启动

else cnt <= 13'd0; ∥波特率计数停止

always @ (posedge clk or negedge rst_n)

if(!rst_n) clk_bps_r <= 1'b0;

else if(cnt == 1302) bps_sig <= 1'b1; ∥ bps_sig高电平作为发送数据的数据改变点. 1302-波特率为9600时的分频计数值的1/2,用于数据采样

else bps_sig <= 1'b0;

assign send_sig = bps_sig;

endmodule

RS232通信模块仿真波形如图7所示。

图7 RS232通信模块仿真波形

3 上位机软件设计

本设计中的上位机软件包括参数配置、数据解帧以及数据存储的功能。如图8所示为上位机软件的框架图。

图8 上位机软件框架图

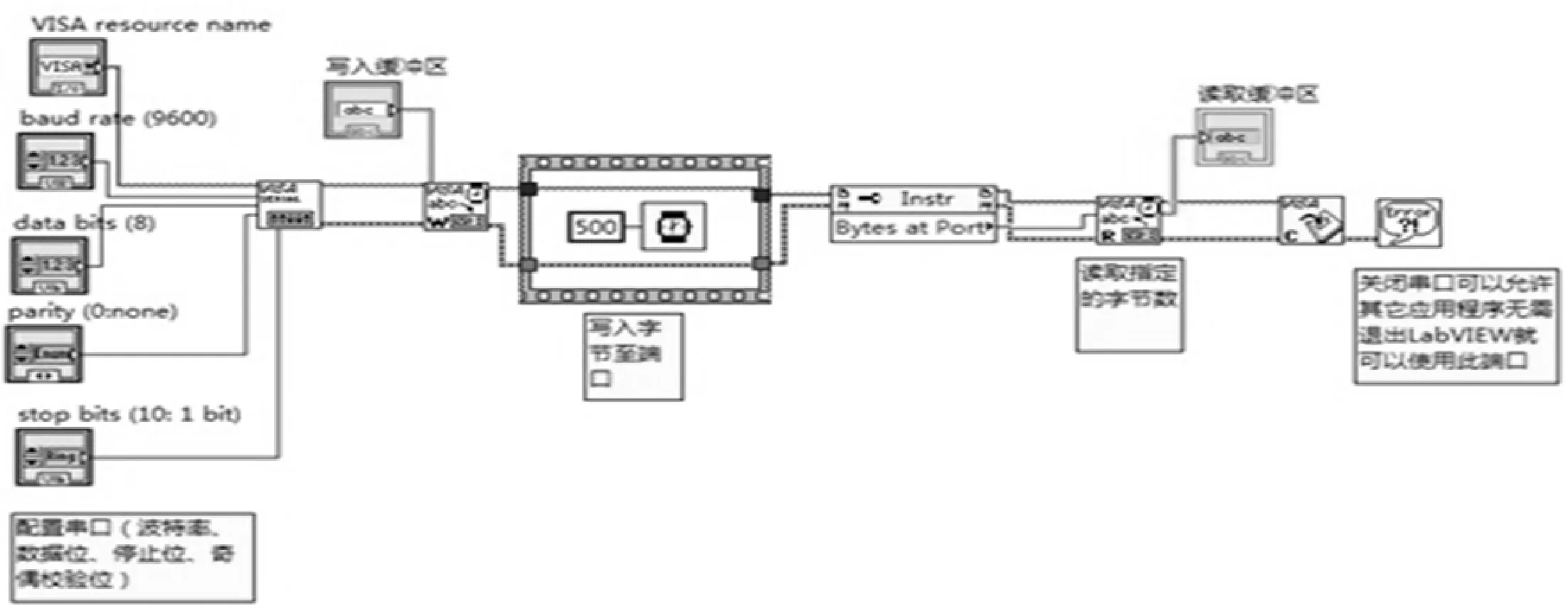

串口配置部分是上位机与下位机数据传输的核心枢纽,在LabVIEW中使用VISA设置串口通信,需要对VISA串口进行配置,该模块分为几个步骤,依次为VISA配置串口、数据的写操作、数据的读操作和关闭串口。其中,LabVIEW中有专用的VISA配置串口函数,使用简单方便快捷。在VISA串口配置时,调用LabVIEW中的VISA配置串口函数,对VISA资源名称、波特率、数据比特位、奇偶校验位以及停止位设定。然后调用VISA写操作,将写入缓冲区中的数据写入串口中,等待500 ms后调用串口字节数属性节点,从VISA读操作中读取指定字节数至读取缓冲区中,最后执行关闭VISA的操作。图9是一个完整的串口通信模块设计图。

图9 完整的串口通信模块设计图

4 系统测试

测量开始后,第一步要对串口进行配置,设置波特率等参数,然后对阈值滤波时间参数和数据存储的自定义路径进行设置。第二步,点击开始按钮,系统正常启动,测量系统开始采集处理接收数据,并且将采集到的数据和波形显示在前面板上。最后,测量系统接收完数据之后,点击停止按钮,将实验数据存储于之前定义好的存储路径中。其中数据采集成功界面如图10所示。

图10 惯导脉冲数据采集成功界面

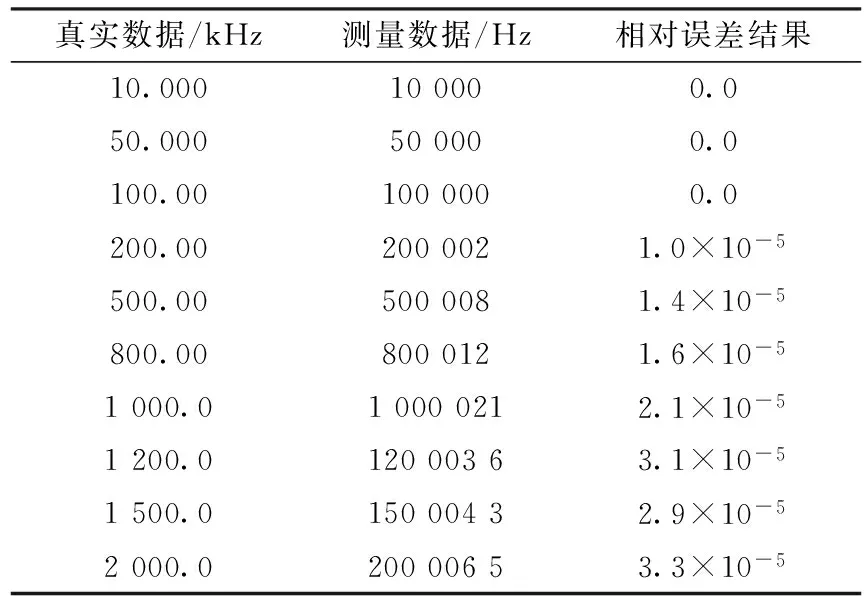

真实数据/kHz测量数据/Hz相对误差结果10.000100000.050.000500000.0100.001000000.0200.002000021.0×10-5500.005000081.4×10-5800.008000121.6×10-51000.010000212.1×10-51200.012000363.1×10-51500.015000432.9×10-52000.020000653.3×10-5

如表1所示,脉冲信号的采集误差<10-4。

5 结束语

本文基于有限状态机、直接脉冲计数以及FIFO存储等技术,对惯导脉冲输出测试系统进行了设计与研究。该测试系统无需人工干预,可自动测试惯导脉冲数据;基于有限状态机技术的阈值滤波模块可滤除干扰信号;FIFO存储改变了以往的数据传输模式,解决了传输速率不一致的问题。经过实验验证,该惯导脉冲输出测量设计方案的可行性得到了认可,其准确性高、自动化程度高,达到了本文的设计目的。

[1] Kuritsky M M,Goldstein M S,Greenwood I A,et al.Inertial

navigation[J].Proceeding of IEEE,1983,71(10):1156-1176.

[2] Kayton M. Navigation ships to space[J].IEEE Transactions on Aero Space and Electronic System,1988,24(5):474-519.

[3] Strachan V F. Inertial measurement technology in the satellite navigation environment[J].Journal of Navigation,2000,53(2):247-260.

[4] Weston J L, Titterton D H. Modem inertial navigation technology and its application[J].Electronics & Communication Engineering Journal, 2000,12(2):49-64.

[5] 陈西斌,赵东发.惯性导航技术发展与应用[J].科技向导,2011(17):21,77.

[6] 秦永元.惯性导航[M].北京:科学出版社,2006.

[7] 张炎华,王立瑞,战兴群.惯性导航技术的新进展及发展趋势[J].中国造船,2008,49(183):134-144.

[8] 田园.多通道脉冲信号高精度计数方法研究[D].西安:西安工业大学,2012.

[9] 周雷.针对XX型号平台惯导测试系统的研究与实现[D].南京:南京理工大学,2013.

[10] 刘宗玉,陈明,王玮,等.基于虚拟仪器的惯导测试与故障诊断系统的设计[J].测控技术,2003,22(3):51-56.

[11] 赵亮亮,肖明清,王志红,等.惯导飞控综合测试系统设计与实现[J].控制技术,2011,(19):575-578.

[12] 陈勇,吴晓男,戴红德.惯导自动测试系统的设计[J].仪表技术,2013(5):39-41.

[13] 董扬.相控阵雷达天线近场多任务测试系统设计[D].南京:南京理工大学,2014.

[14] 袁保伦.四频激光陀螺旋转式惯导系统研究[D].长沙:国防科学技术大学,2007.

[15] MSINS/GPS组合导航系统及其数据融合技术研究[D].南京:东南大学,2006.

The Realization and Research of Inertial Pulse Output Signal Measurement in the FPGA

ZHOU Hang

(School of Information and Control Engineering, Xi’an University of Architecture and Technology,Xi’an 710055,China)

Aiming at the problem of test procedure’s low degree of automation and pulse counting’s bad accuracy, this paper adopts the technology of finite state machine and realizes the function of threshold filter on FPGA platform, and uses direct pulse counting method and FIFO storage technology, solving the problem of pulse counting and inconformity of transmission rate inside measuring system. Adopting the technology of virtual instrument, the paper realizes the function of automatic data processing on the LabVIEW platform. Going through the experimental verification, the measuring system can make true that pulse counting, controlling the error of pulse counting within . And achieving automatic data processing, the design can improve the degree of automation of measuring system.

INS pulse; FPGA; LabVIEW ; accuracy

2016- 05- 07

周航(1990-), 男,硕士研究生。研究方向:智能控制理论研究与应用。

10.16180/j.cnki.issn1007-7820.2017.04.004

TN79

A

1007-7820(2017)04-015-04