基于数字光处理的微型投影设备设计

2017-04-10罗隆恒林祖伦

罗隆恒 +林祖伦

摘要: 随着投影技术的发展,投影系统已被广泛应用于工业和消费电子领域,为了适应市场对其微型化、高清画面和低功耗的要求,设计以德州仪器的DLP2010芯片组为核心,以FPGA为前端控制器,通过I2C和并行视频图像信号对0.2 in(1 in=25.4 mm)DLP芯片组进行控制及图像的投影显示。该设计可使整个设备体积微型化、能耗低、投影图像清晰,适合穿戴式微投影场景的使用。

关键词:

DLP; FPGA; 微型投影; 穿戴式

中图分类号: TN 27文献标志码: Adoi: 10.3969/j.issn.10055630.2017.01.009

Design of micro projection equipment based on digital light processing

LUO Longheng1, LIN Zulun2

(1.School of Microelectronics and SolidState Electronic, University of Electronic Science

and Technology of China, Chengdu 610054, China;

2.School of Optoelectronic Information, University of Electronic Science and Technology of China, Chengdu 610054, China)

Symbol`@@

Abstract:

With the development of projection technology,projection system is widely used in industrial and consumer electronics fields.In order to meet market requirements for its miniaturization,high definition and low power consumption of the device,the design is based on TI's DLP 2010 chipset,and FPGA is the frontend controller.With the I2C and parallel image signal,the 0.2 inch DLP chipset is controlled and projects the image.The design of entire system makes the device miniature and energy efficiency and could project clear image.Thus,it is suitable for the use of wearable microprojection scenarios.

Keywords:

DLP; FPGA; microprojection; wearable

引言

數字光处理(digital light procession,DLP)是一项以微电子机械系统(MEMS)为基础的技术,它使用一个数字微型反射镜器件(digital micromirror device,DMD)进行光线数字调制成像。较之于其他投影技术,DLP技术有清晰度高、光效高、对比度高、灰阶高、寿命长等优势。

当前市场上的许多小型投影产品均采用了DLP技术来实现,但随着虚拟现实和增强现实等技术的发展,它们与投影结合的近眼投影等微型投影技术需要更微小的设备来实现。所以本系统以德州仪器(TI)最小尺寸的DLP2010芯片组为核心,用适合处理图像数据的FPGA作为前端控制器,模拟I2C协议传输指令对DLP芯片组进行控制,并对外部输入图像信号进行处理和传输图像数据,从而更高效、可靠地实现投影功能,并同时能尽量缩小整系统体积[12]。

1系统原理

典型的DLP投影设备的DMD安装在光学模块中,与光学器件和LED光源构成投影显示核心。显示控制器安装在电路板中的光学模块附近,用于控制 DMD 并执行必要的数据格式化和图像处理命令[34]。

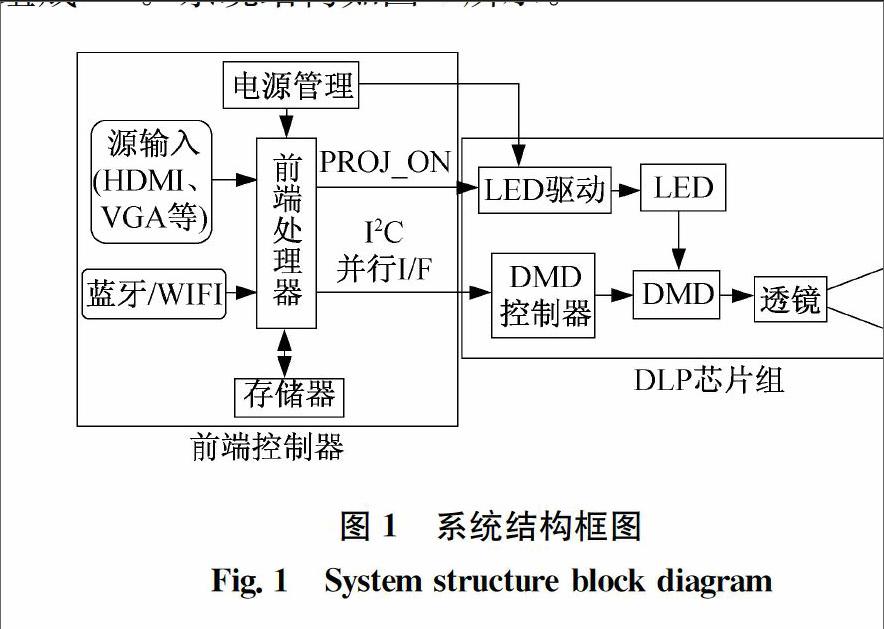

本系统由DLP芯片组和前端控制器两个大模块组成,其中DLP芯片组模块又分为电路与光路两部分。系统电路部分主要由处理器、电源管理、LED驱动、DMD驱动、存储器等部件组成,光路部分由LED、DMD、透镜等器件组成[56]。系统结构如图1所示。

由于DMD驱动的特殊性,TI对每款DMD都推出了相配套的ASICs,DMD驱动芯片和电源管理芯片一起构成了DLP芯片组,从而让我们对DMD的直接控制转换为对ASICs的控制。本系统设计着重于前端控制器的设计,其中前端处理器FPGA为Xilinx的Spartan3系列中的XC3S200,而存储器为与之配套的PROM系列中的XCF02SVOG20C。蓝牙/WIFI和图像源输入接口可视具体应用选择配置。

2DLP芯片组的控制信号

如图1所示,前端控制器需要对DLP芯片组输入PROJ_ON、I2C、并行I/F信号。以下对这些信号的具体需求进行解释。

2.1PROJ_ON信号

当PROJ_ON置高,进入投影状态,图像从DMD投射出去;当PROJ_ON置低,进入低功耗状态,投影自动关闭。

2.2I2C信号

DLPC343X用I2C执行指令,支持最高100 kHz波特率,且支持2个I2C端口。其中Port0优先用于指令和控制接口,当使用这个端口时,其表现为I2C的从机。具体指令功能详见对应芯片组的数据手册。

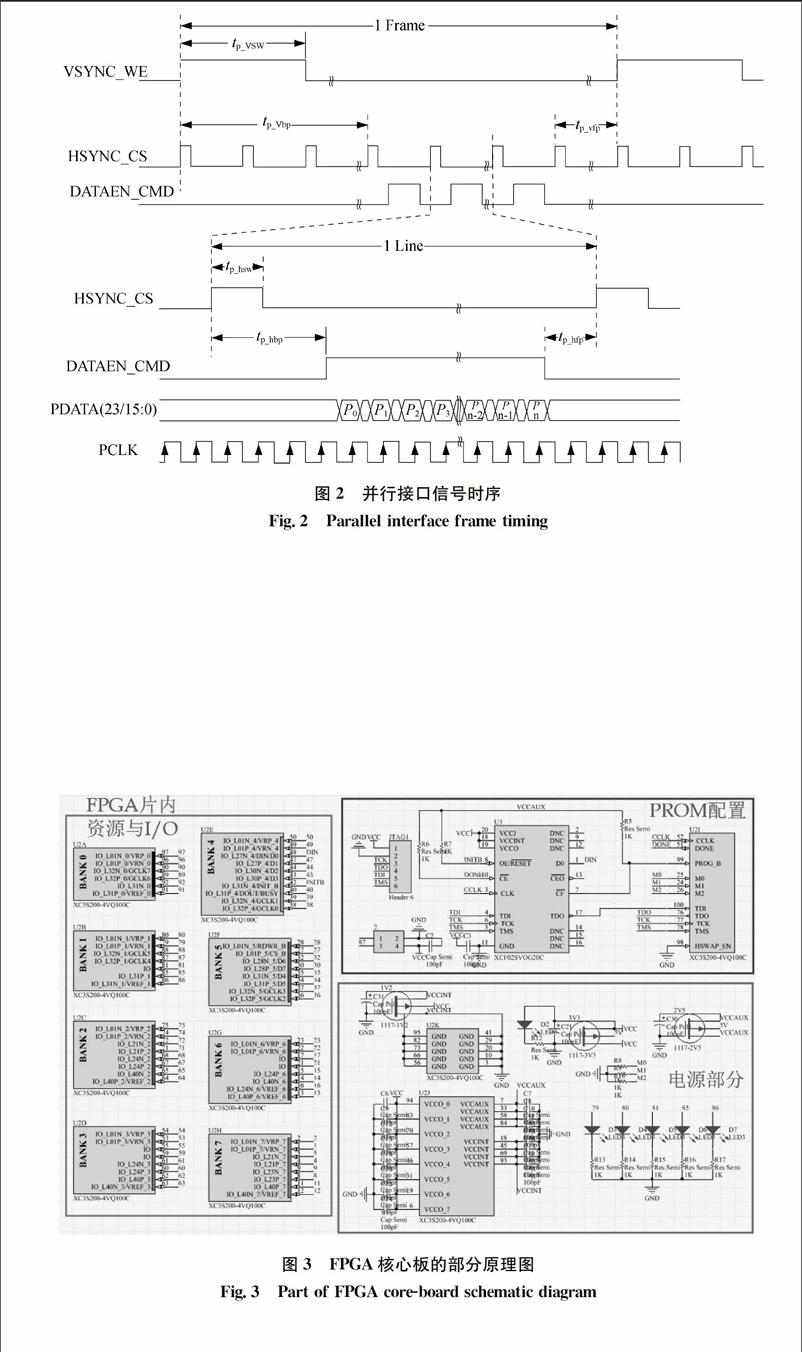

2.3并行I/F信號

并行 I/F信号总共28位,用于传输图像信息。包括VSYNC_WE,HSYNC_CS,DATAEN_CMD,24bit data bus (PDATA),PCLK,具体控制时序如图2所示[7]。

3前端控制器设计

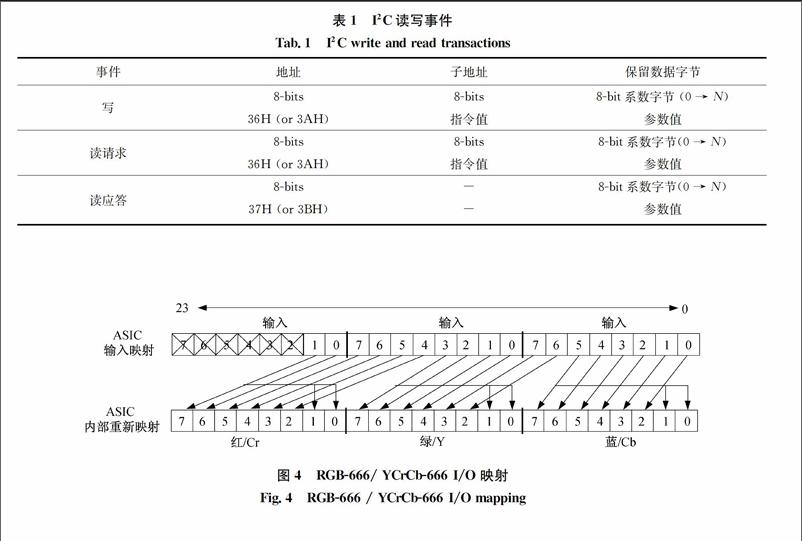

本系统的前端控制器为一块FPGA核心板,由Xilinx的Spartan3系列中的XC3S200,与之配套的

PROM系列中的XCF02SVOG20C等组成,部分原理图如图3所示。图中:FPGA的片内资源与I/O可

引出管脚来控制外设以及进行通信和数据传输;PROM配置用于FPGA的掉电逻辑存储和内部预设图像数据,可通过JTAG模式进行烧录;电源部分提供了FPGA所需的1.2 V、2.5 V、3.3 V供电,包括了电容退耦阵列、LED阵列和LDO部分。

3.1I2C通信

I2C总线要求有两条总线线路:一条串行数据线SDA,一条串行时钟线SCL。I2C总线在数据传输过程中有四种类型的信号:起始命令,结束命令,应答信号,数据信号。在开始传输数据时主控应该首先发送开始命令,之后每发送8 bit数据,接收方将发出一个低电平作为应答信号。若发送方没有收到应答信号,应判断为出现故障,并立即停止工作,返回初始状态准备重新发送。完成所有传输后,主控应发送一个结束命令结束数据传输,在具体事件中应该按要求字节对其发送地址值和数据值。I2C事件类型如表1所示,其中地址对应于控制器的片地址,子地址将对应一个具体指令,保留数据(如果存在)将对应于任何所需的指令参数。由此我们可以根据不同的事件要求进行相应字节的编写来与驱动芯片通信。

我们利用了状态机的原理通过FPGA模拟了I2C事件来与驱动芯片进行通信,对驱动芯片标志各种指令,从而实现了各种不同的功能,如系统复位、输入信号源选择、外部视频源格式选择、图像修剪、图像旋转、设置LED电流等功能。

3.2并行I/F传输

并行I/F信号时序如图2所示,其中:PCLK为系统时钟,频率为1~150 MHz;PDATA每一时钟周期送入一位图像数据;HSYNC_CS为行同步信号,其高电平脉宽为4~128个时钟周期;DATAEN_CMD置高时为一个行同步周期中的数据有效时间,到HSYNC_CS上升沿的最小时间为4个时钟周期,到HSYNC_CS下降沿的最小时间为8个时钟周期;VSYNC_WE为帧同步信号,一个帧同步周期包含了若干个行同步周期,其高电平脉宽最小为1个行同步周期,其建立时间需要至少1个行同步周期,保持时间至少需要2个行同步周期。一个帧同步周期的完成即是相应分辨率的图像刷完了一帧,从而实现了视频图像信号的传输。

数据信号PDATA支持最高24位的数据格式,包括24位的RGB888和YCrCb888,18位的RGB666和YCrCb666,16位的RGB565、YCrCb565和YCrCb4∶2∶2,8位的RGB888、YCrCb888和YCrCb4∶2∶2各种图像格式。这里以18位的RGB666格式为例,由于驱动芯片内部的像素存放为固定的24位,而输入信号为18位,所以驱动芯片会对I/O进行重新映射,如图4所示[7]。

4系统外部接口

为增加系统的功能,可对系统添加外部HDMI接口,使系统可以连接HDMI视频源,进行直接投影[8]。为此我们可以使用一款专用HDMI解码芯片进行功能拓展。

TI官方设计使用了一款ITE6801的HDMI解码芯片,ITE6801FN是一个单端口的HDMI接收器,兼容HDMI 1.4和MHL2.1两种操作模式,ITE6801FN的色深(最多36位)能确保可靠接收高质量无压缩视频内容。使用此款专用解码芯片可以绕过FPGA主控,直接生成PDATA信号,这样可以大大减少FPGA的资源消耗,降低整系统的功耗。

而HDMI视频源的产生也可以用FPGA来模拟实现,其中TMDS编码器模块的Verilog代码如下:

module TMDS_encoder(

input clk,

input [7:0] VD,∥ video data (red,green or blue)

input [1:0] CD,∥ control data

input VDE,∥ video data enable,to choose between CD (when VDE=0) and VD (when VDE=1)

output reg [9:0] TMDS = 0

);

wire [3:0] Nb1s = VD[0] + VD[1] + VD[2] + VD[3] + VD[4] + VD[5] + VD[6] + VD[7];

wire XNOR = (Nb1s>4'd4) || (Nb1s==4'd4 && VD[0]==1'b0);

wire [8:0] q_m = {~XNOR,q_m[6:0] ^ VD[7:1] ^ {7{XNOR}},VD[0]};

reg [3:0] balance_acc = 0;

wire [3:0] balance = q_m[0] + q_m[1] + q_m[2] + q_m[3] + q_m[4] + q_m[5] + q_m[6] + q_m[7] 4'd4;

wire balance_sign_eq = (balance[3] ==

balance_acc[3]);

wire invert_q_m = (balance==0 || balance_acc==0) ? ~q_m[8] :balance_sign_eq;

wire [3:0] balance_acc_inc = balance ({q_m[8] ^ ~balance_sign_eq} & ~(balance==0 || balance_acc==0));

wire [3:0] balance_acc_new = invert_q_m ? balance_accbalance_acc_inc :balance_acc+balance_acc_inc;

wire [9:0] TMDS_data = {invert_q_m,q_m[8],q_m[7:0] ^ {8{invert_q_m}}};

wire [9:0] TMDS_code = CD[1] ? (CD[0] ? 10'b1010101011 :10'b0101010100) :(CD[0] ? 10'b0010101011 :10'b1101010100);

always @(posedge clk)

TMDS <= VDE ? TMDS_data :TMDS_code;

always @(posedge clk)

balance_acc <= VDE ? balance_acc_new :4'h0;

endmodule

5系统测试结果

借助搭载DLP2010芯片组的DLPDLCR2010EVM评估平台和一块FPGA核心板组成了此次系统功能测试的装置,如图5所示。下边的PCB板为FPGA核心板,中间的PCB板为DLP芯片组电路部分,上边为用于投影的光学引擎。

该测试分为I2C标志指令来投影出DLP芯片组内部存储的测试图像和由FPGA模拟HDMI视频源信号来投影外部测试视频图像,如图6所示。由于评估平台带有HDMI接口,所以我们可以直接用HDMI线将FPGA核心板与DLPDLCR2010EVM进行连接,将刷屏图像信息传输到DMD驱动芯片中,再通过DMD与透镜进行投影来显示色块刷屏图像。系统可以投影出清晰度高,光效高,对比度高,灰度等级高的最高25 lm的854×480(WVGA)视频图像。

6结论

本系统的前端控制器设计结构简单,配合最小尺寸的DLP芯片组,可以将整个系统的尺寸大大缩小。由于测试中使用的是工程样板,只为实现功能,并未压缩面积,若将整个系统电路重新布局并重新设计光学引擎,可以使整个系统的尺寸缩小至3 cm×3 cm以内。这样整个系统便可以很容易地做进穿戴式智能设备(VR、AR眼镜,智能手环等)中,使得投影取代屏幕从而得到全新的视觉效果和交互体验。

参考文献:

[1]刘杰.数字光处理DLP芯片及其应用[J].集成电路应用,2015(2):2830.

[2]田文超,贾建援.DMD及DLP显示技术[J].仪器仪表学报,2005,26(S2):358359.

[3]张慧博.基于嵌入式系统下DLP技术的研究与实现[D].北京:北京邮电大学,2014.

[4]曹健,焦海,王源,等.基于FPGA与DLP的体三维显示系统设计方法与研究[J].北京大学学报(自然科学版),2014,50(4):605610.

[5]肖勇.基于DLP的微型投影儀驱动电路设计与实现[D].成都:电子科技大学,2014.

[6]莫志君,张慧莉,余松煜.基于TI DLP技术的投影机驱动电路设计和实现[J].光学仪器,2009,31(6):4851.

[7]Texas Instruments. DLPC3430 and DLPC3435 display controller[DB/OL].http:∥www.ti.com/lit/ds/dlps038c/dlps038c.pdf,201407.

[8]李煌. 基于FPGA的HDMI显示系统的设计与实现[D].上海:华东师范大学,2008.

(编辑:刘铁英)