基于FPGA的RAW图像饱和校正的实现*

2017-03-31李慧林武云钢

李慧林 武云钢

(1.西安工程大学电子信息学院 西安 710048)(2.西安交通大学电子信息工程学院 西安 710048)

基于FPGA的RAW图像饱和校正的实现*

李慧林1武云钢2

(1.西安工程大学电子信息学院 西安 710048)(2.西安交通大学电子信息工程学院 西安 710048)

图像饱和会造成图像的颜色和亮度失真。为了改善图像的质量,论文在现有的算法基础上用FPGA实现了RAW图像饱和校正算法。图像单通道饱和校正时使用了现有贝叶斯算法进行估计,而对图像多通道饱和校正时论文设计了一种环形的硬件结构来实现颜色通道按照顺序处理机制的整个流程,不论哪种校正顺序均能在该环形结构上正确运行。论文算法用VHDL语言编写工程并在Altera Cyclone系列芯片EP4GX150DF31C8上用软件仿真实现,时钟频率最大可以达到110MHz。通过协仿真发现,论文硬件算法可以快速实现对图像饱和像素的校正。论文硬件算法可作为单独的硬件模块植入相机内部进行实时的饱和像素校正。

图像饱和校正; FPGA; 彩色图像处理; RAW图像

Class Number TB861

1 引言

在日常生活中经常可以看到图像过曝光的现象,由于人眼视觉所能感受到的动态范围和自然界本身的动态范围都远远高于图像传感器的动态范围,因此过曝光不可避免的产生。当RAW图像内插后可得到三通道RGB图像,然后需要对三通道图像进行白平衡操作,一般做法是对图像进行白平衡时处理,使RGB三通道获得不同的增益,例如当设置G通道增益系数为1,而R和B通道的增益系数一般都大于1,那么在RGB三通道都饱和的区域,导致那些本来应该为白色的像素偏紫。传统相机厂商消除这种偏色的方法是对图像进行白平衡时,将超过饱和阈值的值都嵌于饱和阈值处。这样将不会使图像偏色,但是这种算法将使得图像的细节信息丢失。

2 贝叶斯算法

Xuemei Zhang等于2004年在惠普实验室工作时提出了一种基于贝叶斯估计的饱和像素校正算法[1]。该算法作用于RAW图像,首先对饱和RAW图像使用简单的双线性内插算法得到三通道RGB图像,然后假设RGB颜色三通道服从三元正态联合分布模型。算法基于该模型计算图像的先验均值和先验方差,将饱和通道和不饱和通道联合起来分析,计算饱和通道在已知未饱和通道的条件分布。由于图像饱和像素校正后的值一定大于或等于饱和值,由此条件可以利用贝叶斯算法来进一步估测饱和像素的值[2]。本文在该算法基础上用FPGA的Cyclone系列芯片实现了图像饱和校正算法。

3 硬件算法设计与实现

3.1 硬件算法结构

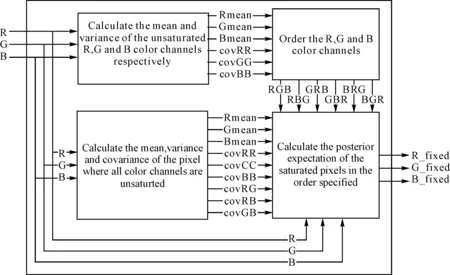

本算法硬件流程如图1所示,主要分为四个模块,从左往右,从上往下,第一个对应为计算每个通道未饱和像素的均值和方差模块,第二个对应为决定饱和颜色通道校正顺序模块,第三个对应为计算每个颜色通道的先验参数模块(包括先验均值和先验方差),第四个为饱和像素校正模块。当RAW图像经过双线性内插算法后得到线性RGB数据后,经过图1所示的硬件模块校正后最终可以得到饱和校正后的三通道值R_fixed,G_fixed,B_fixed。

图1 硬件算法流程

3.2 硬件算法实现

在硬件实现时,第一步获得图像的先验参数。先验参数包括每个颜色通道的先验均值及先验方差以及颜色通道间的协方差。

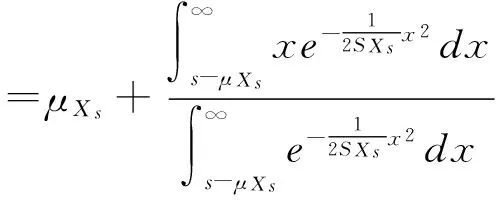

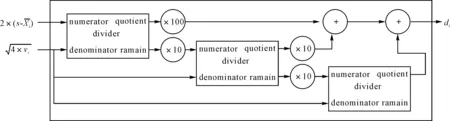

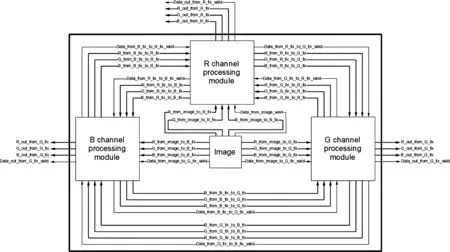

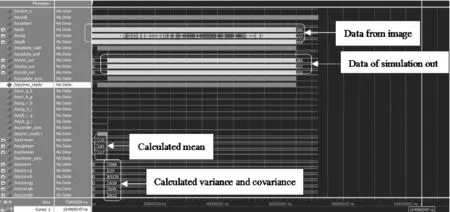

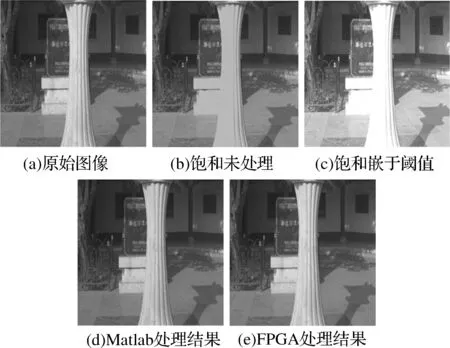

当图像单通道饱和时,在计算每个图像颜色通道先验均值时用该通道未饱和像素来统计该通道的均值可能比较准确,但是先验协方差的计算却要用到那些三通道全部未饱和的像素,这样会造成RGB三个通道均值和方差计算不一致性而导致图像三通道之间的关系发生变化[3]。因此在计算该连通域的先验参数时,一定要选择那些三通道全部未饱和的像素进行计算,即选择的因子sel=R (1) (2) 硬件实现时,由于对于当使用根号运算IP核没有使用到小数位,使得di的计算不够准确。为了更加准确地计算距离di值,扩大了vi的值,在运算时,将vi乘以4。这种操作在硬件实现时只是简单的将数据左移2位,因此计算距离di时,公式可以转换为 (3) 为了更加准确地计算出不同颜色通道距离di的值,本文将di的值精确到小数点后两位,即类似将数学运算后的浮点值乘以100然后对其取整比较三通道间距离的大小。距离的比较模块如图2所示,模块中用到了三个除法器,每个除法器可以获得距离di的一位值,第一个除法器输出的结果乘以100,第二个除法器输出的结果乘以10,第三个除法器输出的结果不作处理,然后将三者相加得到精确到小数点后两位的颜色通道距离di的值[6]。 图2 计算距离di模块 三个颜色通道处理顺序可以分为六种情况,如图1所示,本文用六个信号来表示可能的情况RGB,RBG,GRB,GBR,BRG,和BGR。例如,当比较后的结果为dR≤dG≤dB,信号值RGB将会被置1,校正顺序则按照RGB进行。当校正顺序一定时,图像饱和校正过程中将按照此顺序依次对RGB三个通道值进行校正。本文设计了一个环形硬件结构对三通道值进行校正,如图3所示,主要由三个模块构成,R通道饱和校正模块,G通道饱和校正模块,B通道饱和校正模块。当校正顺序为RGB时,则算法流程按照逆时针方向依次对三通道进行校正,第一个模块用来接收待校正的RGB图像数据,最后一个模块将输出校正后的RGB三通道值。 图3 环形硬件校正模块 本文首先在Microsoft Windows 7 32bit系统上分别编写软件代码和硬件代码,在Matlab R2014a上编写软件代码仿真通过后用Quartus II 13.0 SP1(32 bit)工具编写VHDL代码实现基于硬件的饱和校正的整个流程。截取的RAW图像分辨率为500×328。整个硬件工程是基于Altera Cyclone系列的低端消费类的芯片EP4CGX150DF31C8来完成。该芯片内部有149760个逻辑单元,720个M9K块,6个PLL,30个全局时钟,最大用户IO为508。最后用Matlab R2014a和 Modelsim SE 10.1c 协同仿真,用link for ModelSim接口进行验证本算法的结果[7]。 图4所示是在Modelsim中波形仿真后的结果,可以看出硬件处理过程中首先计算出图像的先验均值和方差以及协方差,然后对图像进行饱和像素的校正,最后输出饱和校正后的图像数据。 图4 Modelsim仿真结果 图5(a)所示是用索尼RX100II相机在公园处拍摄的一个柱子图像,图像未饱和,因此人为给图像一个饱和阈值。当图像像素大于饱和阈值时,重新赋值为饱和阈值,如图5(b)所示,由于绿色通道饱和较为严重,白平衡后的图像饱和区域偏紫。图像中32.3% 的区域发生了绿色通道饱和,0.03%区域发生了红色通道饱和,0.07%的区域发生了蓝色通道饱和。传统的相机处理算法是在白平衡后直接将超过饱和阈值像素点的值嵌于饱和阈值处,这样会导致图像丢失一些细节信息,如图5(c)所示柱子丢失了纹理细节。图5(d)为Matlab处理后的结果,图5(e)是本文提出的FPGA处理后的结果,可以看出用FPGA实现的饱和校正算法的结果使柱子纹理信息得到了很好的还原[8],而且与Matlab处理的结果相比较几乎看不出差异。 图5 饱和图像以及处理结果 本文基于FPGA提出了一种环形的硬件模块结构实现了图像饱和像素的校正算法,并且在低端消费类芯片Cyclone中编译通过,协仿真正确。由于FPGA实现的高效,并行性,价格低廉等优点[9],因此可以将该算法的硬件模块置于数码相机中实时地进行图像饱和像素的处理,以此来改善大部分拍摄图像的质量从而避免了将饱和图像转到计算中上再进行色彩的恢复与还原[10]。 [1] X. Zhang, D. H. Brainard. 数字图像的饱和校正算法[J]. J Opt Soc Am A Opt Image Sci Vis, December 2004,21(12):2301-2310. X. Zhang, D. H. Brainard. Estimation of saturated pixel values in digital color imaging[J]. J Opt Soc Am A Opt Image Sci Vis, December 2004,21(12):2301-2310. [2] Di Xu, Colin Doutre, Panos Nasiopoulos. An improved bayesian algorithm for color image desaturation[C]//Image Processing (ICIP), 2010 17th IEEE International Conference on. IEEE,2010:1325-1328. [3] Di Xu, Colin Doutre, Panos Nasiopoulos. Correction of clipped pixels in color images[J]. IEEE Transactions on Visualization and Computer Graphics,2011,17(3):333-344. [4] Assefa M, Poulie T, Kervec J, et al. Correction of over-exposure using color channel correlations[C]//Signal and Information Processing (GlobalSIP),2014 IEEE Global Conference on. IEEE,2014:1078-1082. [5] Fu J, Peng H, Chen X, et al. Correcting saturated pixels in images based on human visual characteristics[C]//IS&T/SPIE Electronic Imaging. International Society for Optics and Photonics, 2013:1078-1082. [6] Zhang X, Brainard D H. Bayesian color correction method for non-colorimetric digital image sensors[C]//Color and Imaging Conference. Society for Imaging Science and Technology,2004,2004(1):308-314. [7] Foi A, Trimeche M, Katkovnik V, et al. Practical Poissonian-Gaussian noise modeling and fitting for single-image raw-data[J]. Image Processing, IEEE Transactions on, 2008,17(10):1737-1754. [8] Hongshi Sang, Yong Fu, Tianxu Zhang , et al. Connected Components Labeling Algorithm for Multi-value Image that Suitable for Realization in VLSI[J]. Huazhong Ligong Daxue Xuebao,2005,33(9):5-8. [9] Masood S Z, Zhu J, Tappen M F. Automatic Correction of Saturated Regions in Photographs using Cross‐Channel Correlation[C]//Computer Graphics Forum. Blackwell Publishing Ltd, 2009,28(7):1861-1869. [10] D. H. Brainard, W. T. Freeman. Bayesian color constancy[J]. Opt. Soc. Am. 1997,14(7):1393-1411. Implementation of Estimating Saturated Pixel Values Based on FPGA LI Huilin1WU Yungang2 (1. School of Electronics and Information, Xi’an Polytechnic University, Xi’an 710048) (2. School of Electronics and Information Engineering, Xi’an Jiaotong University, Xi’an 710048) Pixel saturation is very common in digital color imaging, which will result in the artifact of color splash. In order to improve image quality, this paper presents a hardware implementation in a FPGA circuit of an algorithm to estimate saturated pixels in RAW image. For the 1-channel saturation, the Bayesian estimation is realized using simple digital circuits and memory. For the 2-channel and 3-channel saturation, a ring structure is designed to handle the saturated color channels in the order obtained previously. Whatever the order of the color channels is, the image data can be processed properly by the ring structure. The design has been specified in VHDL targeted on an Altera Cyclone EP4CGX150DF31C8 based FPGA and verified for functional correctness by software simulation, and the fmax can reach 100MHz. Co-simulation shows that the proposed method in hardware implementation has estimated the saturated pixels fast. The hardware algorithm can be embedded inside the camera to realize correcting saturated pixels in real time. estimate saturated pixels, FPGA, color image processing, RAW image 2016年9月11日, 2016年10月30日 李慧林,女,硕士研究生,研究方向:信号与信息处理。武云钢,男,硕士研究生,研究方向:数字图像处理。 TB861 10.3969/j.issn.1672-9722.2017.03.026

4 仿真结果分析

5 结语