光伏并网电流与电网电压同频同相的技术实现

2017-03-30杨思俊

杨思俊

(西安航空职业技术学院,西安710089)

光伏并网电流与电网电压同频同相的技术实现

杨思俊

(西安航空职业技术学院,西安710089)

通过性能稳定的DSP控制器程序设计及外围硬件检测电路、采样电路的配合来实现在光伏并网发电中对并网电流与电网电压的频率和相位控制,达到两者同频同相。阐述了锁相环技术原理及软件实现锁相的基本模型;分别介绍了软件实现锁相所需的三部分硬件电路即电网电压采样电路、电网电压过零检测电路、DSP内部功能单元;采用DSP作为控制芯片,进行内部功能设置;完成锁相环的软件设计,通过连续调整可实现并网电流与电网电压周期趋近相同来实现输出电流与电网电压同频同相控制,从而实现了逆变器输出电流是单位功率因数。

数字锁相环;光伏并网;DSP控制;电压过零检测;PWM脉冲;软件锁相;电网电压采样

1 引言

为了保证光伏并网发电系统中逆变器输出的交流信号与正常状态下的电网电压保持同频、同相,即系统并网输出功率因数cos Φ=1,引入锁相技术实现这个功能。本文采用软件锁相技术,即利用DSP程序设计,并且搭建外部信号处理电路,实现高阶、高稳定性、设计方便的并网锁相,以保证馈入电网的电能质量。

在锁相环技术中,关键要解决如何在不受电网电压扰动影响的情况下,正确检测出电网电压的零相位时刻;如何产生N倍于电网频率的等间隔相位的离散信号。

2 锁相环原理

锁相环(PLL)是一个闭环反馈控制系统,它能够自动追踪输入信号的频率与相位。由于传统的硬件锁相环难以克服区间饱和、零点漂移等问题,它逐步被高速处理器为核心的软件锁相环所代替。本设计中首先采用模拟器件搭建检测电路,将相位差信号通过检测电网电压过零点求得,送入DSP处理器,然后锁相控制环节通过算法程序实现软件锁相环技术[1]。

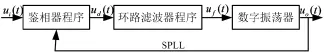

软件锁相环(SPLL)是由整个程序中的鉴相器程序、环路滤波器程序、数字振荡器三个软件部分构成,基本模型如图1所示。

图1 软件锁相环的基本模型框图

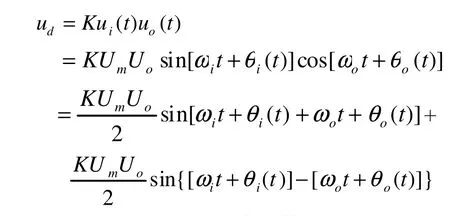

由瞬时频率和瞬时相位的关系可知:

3 锁相环的硬件电路实现

软件锁相是由输入信号的硬件整形电路、DSP内部功能单元和锁相软件配合完成的。

利用DSP的CAP模块捕捉电网电压过零点信号并计算当前的电网周期,通过带死区控制的PWM发生模块,编写程序,调节SPWM调制载波的频率,实现并网电流准确跟踪电网电压的频率,并使并网电流与电网电压同相。

通过电网电压采样检测到与电网电压同频同相的电压信号,经过滞回比较器及滤波电路后产生与电网电压同步的方波信号,方波信号输入CAP对应的管脚并捕捉电网电压的上升沿跳变。将CAP设置为上升沿有效,软件捕捉到方波信号的上升沿并记录此时定时器计数的值,相邻两次计数的差值即为一个电网周期。在上升沿发生时刻,根据正选表格指针所处的位置来求取并网电流和电网电压之间的相位差,根据相位差来相应的调整指针,从而实现对电网电压频率和相位的检测[4]。

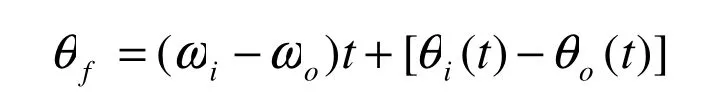

(1)电网电压采样电路

如图2所示,采用霍尔传感器LV25-P采样电网电压,采样的交流电压信号为-1.5V-1.5V,由U1A进行隔离,通过U1B将采样的交流信号和1.5V的直流电压信号相叠加,生成0-3V的交流电压信号。由于LV25-P的偏差线性度小于0.2%,故信号通过由TL084组成的电压跟随器及滤波后送给DSP的AD转换口[5]。

图2 电网电压采样电路

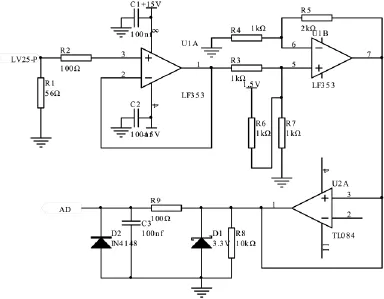

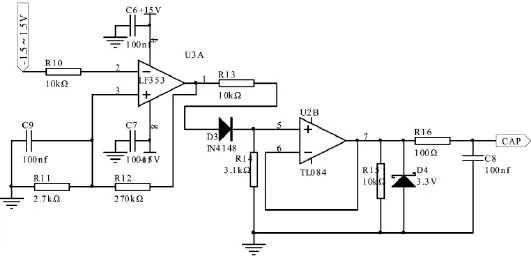

(2)电网电压过零检测电路

如图3所示,在进行电网电压采样时,LM353作为滞回比较电路,对采样的交流电网电压进行过零点检测。将正弦交流信号转化为50Hz的方波信号并送至DSP的CAP口[6],当上升沿跳变时(电网电压从负变为正跨越零轴时),CAP检测到电网电压脉冲,就会产生一个捕获中断信号。

(3)DSP的内部功能单元

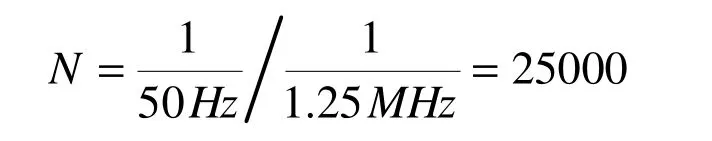

在本系统的软件锁相过程中,主要涉及定时(PWM)中断和捕捉(CAP)中断。DSP内部为CAP分配一个计数时基T2,设定为递增计数模式,计数频率设定为1.25MHz,数字锁相环的频率范围为50± 0.5Hz,这样,可求得两次中断计数器的差值。

当数字锁相环的频率在49.5-50.5Hz范围变化时,两次中断计数器的差值变化范围是24752-25252。当软件捕捉到相邻的两个上升沿跳变时,会记录下两个时刻计数器T2中寄存器的值,则相邻两次计数器的差值即为所测电网电压的周期。

图3 电网电压过零检测电路

由于相位检测比较复杂,而周期检测相对方便,根据周期与相位之间的积分关系,在实际应用中将频率或周期作为输入变量,采用过零比较法进行频率和相位锁定。在定时(PWM)中断中,计算并输出逆变器的参考正弦波信号,通过电网电压的上升沿(电网电压从负变为正跨越零轴时)产生中断,并将此刻电网电压的周期T1与设定的T0进行比较,如果电网电压的周期大于设定周期表示此时的频率小于正常的50Hz,并根据已求取的相位差△θ渐近移动正弦表格指针,来“靠近”正常电网电压的周期和频率,以实现并网电流和电网电压的相位渐近跟踪[7]。

在程序设计中,使PWM中断优先级高于捕捉中断,PWM中断时间间隔设置为100us,将正弦表格分为200个点,则每个点对应的电角度为1.8度,载波频率为10KHz,CPU时钟频率为40MHz,理论上的最小相差仅为0.18度,功率因数cosΦ=0.999。

4 锁相环软件设计

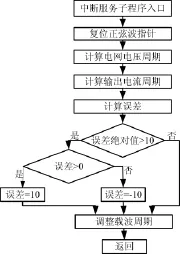

程序流程如图4所示,当DSP的CAP模块检测到电网电压同步信号的上升沿跳变时,便产生捕获中断,使正弦波离散表的指针复位到零,该表存储在比较寄存器中。而PI外环控制得到的下一周期瞬时电流的预测值乘以正弦波离散表指针所指地址中的数据,形成瞬时电流使得瞬时电流相位与电网电压的相位保持一致即为实现同相控制。在中断程序中,算出电网电压的周期(约20ms,两次上升沿跳变的间隔),由于电网周期约为20ms,PWM载波周期设置为约50μs,20ms/50μs=400,故一个电网周期对应400个载波周期。将400个PWM载波周期的和与电网电压的周期相比较,根据(比较后的误差)不断调整PWM的载波周期[8]。若输出电流的周期大于电网电压的周期,则应使发生SPWM三角载波信号的周期寄存器中的值减小。通过连续调整可实现并网电流与电网电压周期趋近相同来实现输出电流与电网电压同频同相控制。

图4 锁相环子程序

[1]张文.数字化光伏并网系统的逆变技术研究[D].广州:华南理工大学,2013. Zhang Wen.Inverting Technology Research on Digital Grid Connected Photovoltaic System[D].GuangZhou:South China University of Technology.2013

[2]邢丽娟.孔祥新.基于DSP技术的软件锁相环设计[J].电子技术设计与应用,2014(12):018-020. XING Li-juan,KONG Xiang-xin.Software Phase-Locked Loop Design Based on DSP Technology[J].Electronic Technology,2014(12):018-020.

[3]郑诗程.光伏发电系统及其控制的研究[D].合肥:合肥工业大学,2014. ZHENG Shi-cheng.Research on Photovoltic Generation System and Its Control[D].HeFei:Hefei University of Technology,2014. [4]马俊婷.户用型可并网单相光伏逆变器的研究[D].北京:华北电力大学,2012. MA Jun-ting.Research on Single-Phase Grid-Connected Photovotaic Inverter for Household[D].BeiJing:North China Electric Power University,2012.

[5]杨国韬.基于光伏并网逆变器的软件锁相环技术的研究[D].太原:太原理工大学,2013. YANG Guo-tao.Based on the Photovoltaic(pv)Grid Inverter Software Phase-Locked Loop Technology Research.Taiyuan: Taiyuan University of Science&Technology,2013.

[6]孙秀芬.孟娜.基于软件锁相环的电网电压实时检测的研究[J].华北电力技术,2014(3):002-005. SUN Xiu-fen,MENG Na.Based on the Software Phase-Locked Loop Power Grid Voltage Real-Time Detection Research[J].North China Electric Power.2014(3):002-005.

[7]胡永红.数字锁相环的优化设计与应用[J].计算机测量与控制,2006(8):085-086. HU Yong-hong.The Optimal Design and Application of Digital Phase-Locked Loop[J].Computer Measurement& Control.2006(8):085-086.

[8]刘阳.基于数字锁相环的低功耗时钟发生器设计 [D].北京:北京交通大学,2014. LIU Yang.Based on Digital Phase Locked Loop of Low-Power Clock Generator Design[D].BeiJing:Beijing jiaotong university,2014.

Technology of Photovoltaic Grid Current and Grid Voltage with Same Frequency and Phase

Yang Sijun

(Xi'an Aeronautical Polytechnic Institute,Xi'an 710089,China)

Through programming of the stable DSP controller and combination of the peripheral devices such as hardware detection circuit and sampling circuit,the frequency and phase control of the photovoltaic(pv)grid current and grid voltage are implemented to make the same frequency and phase.This paper introduces the principle of PLL and the basic model of software phase lock;It respectively introduces the software implementation phase locking the three parts of hardware circuit, i.e.power grid voltage sampling circuit,grid voltage zero crossing detection circuit and DSP internal functional units;It uses DSP as control chip to set the internal function,and uses the software of SPLL design,through the continuous adjustment of grid current for approaching the grid voltage cycle to the same output current frequency,to control the current and the voltage in the same frequency and phase and make the inverter output current with the unit power factor.

Digital PLL;Grid-connected photovoltaic power;DSP control;Voltage zero crossing detection;PWM pulse;SPLL;Grid voltage sampling

10.3969/j.issn.1002-2279.2017.01.021

TN73

A

1002-2279-(2017)01-0083-03

杨思俊(1981-),女,陕西省渭南市潼关县人,讲师,硕士研究生,主研方向:嵌入式控制、开关电源。

2016-05-24