基于DE1-SoC的磁性介质显示系统设计与实现

2017-03-27周艳玲张子佳曾张帆

张 雄,周艳玲,张子佳,曾张帆

(湖北大学 计算机与信息工程学院,武汉 430062)

基于DE1-SoC的磁性介质显示系统设计与实现

张 雄,周艳玲,张子佳,曾张帆

(湖北大学 计算机与信息工程学院,武汉 430062)

针对常规平面成像技术表现形式单一,容易视觉疲劳等问题,提出一种新型的基于FPGA/ARM异构双核控制的磁性介质显示系统,实现磁性介质的立体动态成像;本系统通过在Altera DE1-SoC的Linux平台上构建Lighttpd轻量级Web服务器和设计开发功能程序、底层驱动程序、自定义IP核和Verilog逻辑译码程序来实现该显示系统的软硬件开发;本系统具有网络设备跨平台控制能力、磁流体精确控制能力以及多种样式的汉字和图案显示能力;大量实验表明该系统能够通过控制磁流体完美的表现出立体书法、绘画图案,且系统运行稳定可靠。

DE1-SoC;磁流体;Lighttpd;IP核;显示原型机

0 引言

近年来,随着人们生活水平的进步,对视觉的需求也逐步提高,主要表现在内容上追求丰富多彩和表现形式上希望生动灵活。传统的显示技术如液晶屏、LCD、投影等已广泛应用于商场、教室、会议等社会活动的各个领域与场所,在表现内容上非常丰富,为人们的生活提供了诸多便利。然而,上述技术在表现形式上主要以图像或者动画为主,表现风格比较传统,特别在某些应用场景如国画,书法方面的表现上不够生动,难以达到预期的效果。

基于此,本文提出一种新的基于网络控制的磁性介质显示系统。通过在Altera DE1-SoC的Linux平台上构建Lighttpd轻量级Web服务器和设计开发功能程序、底层驱动程序、自定义IP核和Verilog逻辑译码程序,实现了跨平台的适合网络操作的磁场控制系统。进一步,结合一种经过改良配方的类油墨性磁介质纳米[1]材料,成功研制了一种带显存的磁性控制显示平台。

1 系统总体架构

磁性介质显示系统总体架构如图1所示,主要包括3个部分:

(1)磁性介质显示模块;

(2)显示屏驱动模块;

(3)主控板DE1-SoC。

图1 磁性介质显示系统架构图

磁性介质显示模块用来展示最终图像。在该模块中,黑色的磁性纳米材料作为显示“墨水”,白色的悬载液作为背景。单元像素点由单点电磁极构成,磁极按照固定的磁场结构紧密排放形成多像素显示屏。单个电磁极通过其输入电流的方向和大小来控制磁场,以达到控制单点的磁性材料成像,输入多位并行显示数据来控制模块多像素成像。散热结构是用来解决多磁极密集工作的功耗热量问题。

显示屏驱动模块是整个系统的硬件中间结构,目的是优化多点像素的控制模式,简化控制接口,缓存高速显示数据。其输出为磁性介质显示模块的多位并行显示数据,输入为主控板DE1-SoC模块的串行输出信号,包括控制信号和显示数据。该模块是用硬件实现串行信号中显示数据的解析,当解析完全部像素的显示数据后,再输出至磁性介质显示模块。

主控板DE1-SoC模块为整套系统的软件提供基础运行平台。该模块硬件部分采用DE1-SOC开发板,其核心模块为Altera公司研制的CycloneV-SoC-FPGA芯片。该芯片内集成了FPGA逻辑和一套硬核系统(Hard Processor System:HPS)。其中,HPS包括ARM Cortex-A9双核处理器[10]、固定外设和存储系统。采用这类HPS+FPGA[3]的系统结构,硬件可以根据需求定制基于AXI总线的用户外设,包括可扩展IO口、多CPU、定制指令集、硬件加速器等。基于DE1-SOC硬件开发板,设计了一系列软件基础平台与服务,从顶向下包括web服务器平台、基于DE1-SoC移植的Linux操作系统、Linux应用程序、驱动程序和Verilog逻辑译码程序。该模块的核心是设计控制信号流和各层软件,从web端输入的汉字信息、显示效果、时钟信息、调时控制等数据,经过中间软件逐层分析,最后至FPGA的自定义GPIO口,使显示数据串行输出到显示屏驱动模块。

2 系统硬件部分

硬件部分包括磁性介质显示模块和显示屏驱动模块。

显示屏驱动模块实现数据串并转换,分时加载并行显示数据、驱动锁存器、控制外部磁极矩阵,最终实现显存机制,其内部各子模块相互之间的信号流如图2所示。

图2 硬件模块信号流图

如图2所示,该模块的拥有4路输入信号,包括数据信号、帧截止、同步时钟、数据有效时钟辅助信号。输入信号通过译码器、锁存器等子模块最终转换为64位磁极矩阵显示图案的驱动电平信号。接下来就硬件部分的若干关键子模块:译码解析子模块和磁极矩阵子模块进行详细介绍。

2.1 译码解析子模块

译码解析模块用于按3位地址分帧对8位显示数据进行解析锁存。该模块由74HC138与74HC07芯片组成,其输入为ADDR[2:0]与bigclk_line[7:0]。模块工作原理如下:

(1)[ADDR]数据进入74HC138芯片进行3-8译码转换,译码结果根据采样脉冲[bigclk_line]触发输出。

(2)输出数据由两块74HC04芯片进行电平反向转换,最终译码模块输出为高电平有效的脉冲。

64位并行锁存器的功能是存储64bit的显示图像并将其经过功率驱动模块并行输出。该模块由8个8位74HC573组建的显存模块,输入信号为8位数据(光耦隔离后的Data)与8位地址选通(地址译码模块输出),输出信号为64位并行数据。其工作原理原理是Data同时输入8个74HC573输入端,每个74HC573根据地址译码模块输出的脉冲依次顺序选通,按次序将Data锁存到每个74HC573芯片中,完成了图像的像素点还原并引出全部像素点对应的控制管脚共64个。

功率放大模块用于放大像素控制管脚的控制功率。该模块的输入端包含64个5 V端口、输出端包含64个30 V端口,其内部结构主要包含8片复合管NLU2804A组成的并行64通道放大电路。

2.2 磁极矩阵子模块

磁极矩阵模块主要功能为产生8×8点阵的特定磁场,以驱动磁流体流动成像,其实物如图3所示。

图3 8×8点阵磁极

该模块使用64个定制磁极,按照固定磁场结构紧密排列,通过控制从单个磁极输入电流的方向和大小来控制磁场。

3 系统软件部分

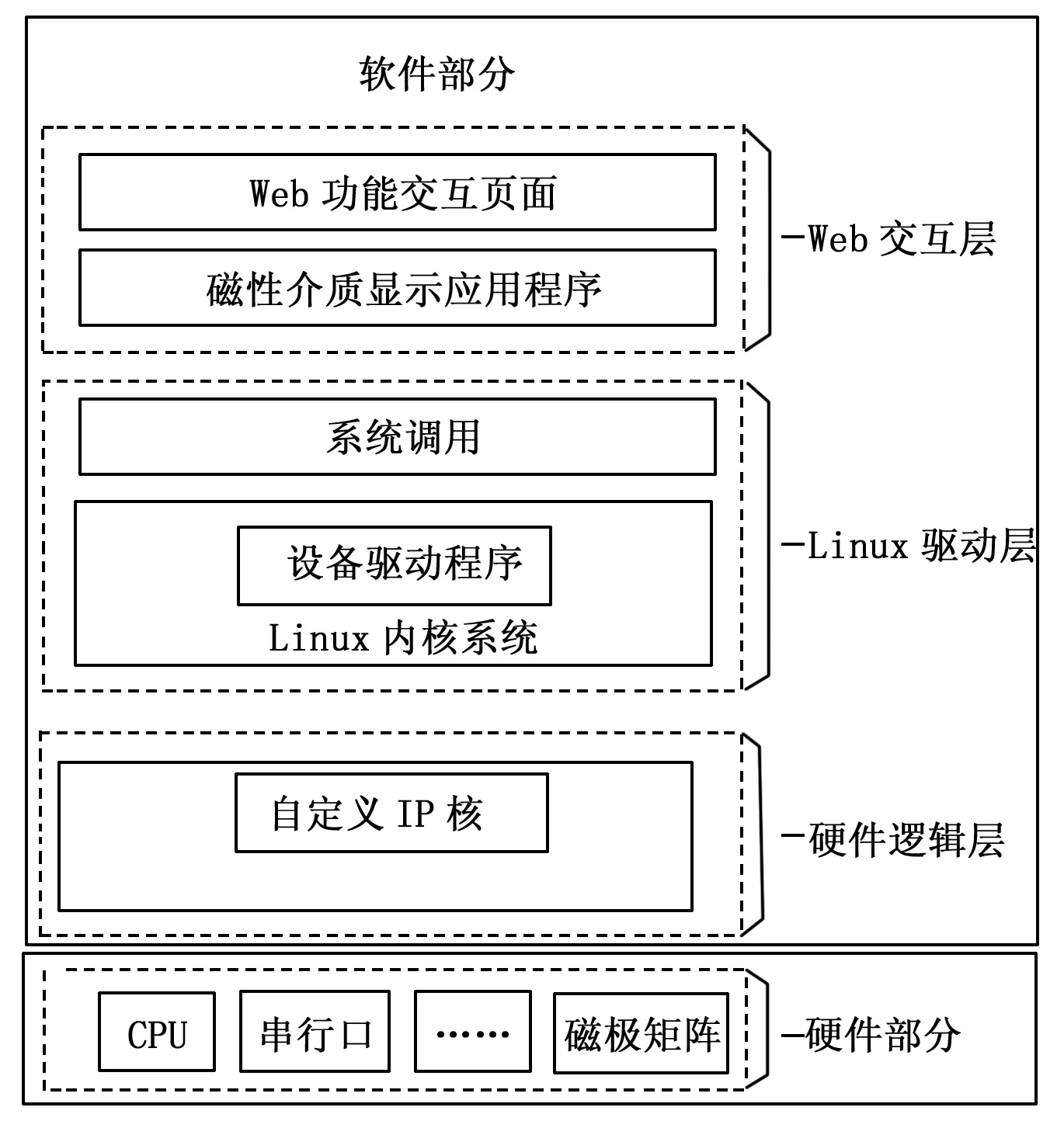

3.1 整体软件架构

系统在软件架构设计方面引入了全可编程(All Programmable)的概念,即软件可编程和硬件可编程。该架构不仅充分实现了软件编程开发速度快与硬件实现响应迅速的优点,同时增加了硬、软件资源配置的灵活性。此外,整体的软件架构采用分层的设计,模块化程度高,易于维护和后续的功能扩展。该系统的软件架构如图4所示。

图4 系统软件架构

软件架构自顶向下包括Web交互层、Linux驱动层和硬件逻辑层。Web交互层为用户提供控制界面,同时转换控制数据给Linux驱动层;Linux驱动层负责将数据传输给硬件逻辑层,该层主要为适配操作系统的架构,就不详细描述;硬件逻辑层主要对接收到的数据进行缓存处理,再串行输出到底层硬件。接下来就Web交互层和硬件逻辑层详细描述。

3.2 Web交互层

Web交互层的底层硬件为DE1-SoC开发板,其核心芯片为FPGA和双核ARMCortex-A9。移植的Linux操作系统为底层软件基础,构成系统的基本运行环境。

在Linux操作系统上移植lighttpd轻量级的Web服务器,将Linux脚本语言与CGI程式网页结合,使得Linux应用C程序能够接收来自Web端提交的数据,然后解析输出相应的显示编码给硬件逻辑层,最终实现Web远程的跨平台控制功能。

Web交互页面开发主要包含3个模块:Lighttpd网页服务器模块移植、Web页面模块开发以及数据交互协议自定义。

Lighttpd服务器是一套开源的网页服务器,相比同类开源网页服务器,它仅需要少量的内存及CPU资源即可达到类似的性能。同时该服务器在支持静态对象(例如,图片文件)时,Lighttpd响应速度更快,为后续实现更加复杂的web端控制提供可扩展性。

基于DE1-SOC的Lighttpd服务器移植流程包括源码下载、编译、修改配置文件等。数据交互通过Linux中的Bash Script来捕捉输入参数值,然后输入给Linux C应用程序。此外,为了加强数据交互的可靠性及规范性,该系统同采用了自定义数据交互协议,增加奇偶校验、隔离码等安全技术。

Linux应用C程序针对三类不同应用风格设计了3种功能:8×8汉字动态实时显示、贪吃蛇游戏和5×16时钟控制。

3.3 硬件逻辑层

磁流体显示系统的硬件逻辑层部分包括6个模块,分别为IP核输入、数据效验解析、分析存储、协议解析、串行转换和GPIO输出。输入[0-11]位的IP核挂载在ARM端的内部总线上,可供上层Linux驱动程序写入数据,使Linux能够通过地址映射跟Qsys上的硬件逻辑进行交互。数据校验解析模块接收Linux应用程序下发的数据,对该数据按照自定义协议进行校验并解析,保证数据传输的可靠性。分析存储模块将效验解析后的数据储存到一个双口8×8RAM中,为协议串行转换模块提供数据输入。协议解析模块和协议串行转换模块是将双口8×8RAM中的数据将8×8的RAM数据按照给定频率串行输出至GPIO口,并提供帧数据完结信号和辅助时序信号。

4 实物效果、系统测试与分析

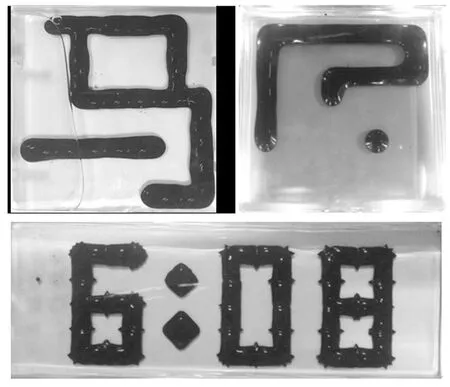

依据上述整体架构与软硬件技术,已经实现了磁性介质显示系统。根据系统的功能设计对其进行测试,对8×8和5×16两种不同尺寸的磁性介质显示模块进行整体效果测试,显示效果如图5所示,依次为中国字“马”、“贪食蛇游戏界面”以及“时钟”。

图5 磁性介质显示系统输出图案

该系统的测试包括磁性显示介质测试、硬件电路测试、FPGA编码逻辑测试以及Web页面功能控制模块测试等。

对磁性显示介质长达5个月的观察,该材料在常温下依然具有较好的流动性、聚合性和稳定性且不粘附于器皿壁。

硬件电路测试包括模块单元测试和整体集成测试。对隔离、解码、锁存和驱动等各个模块分别进行单元测试,其输入输出满足功能需求。在整体集成测试时,模块间级联有干扰,后采取在级联处增添上下拉电阻或滤波电容等方法来消除干扰,最终硬件的整体集成测试达到目标需求。

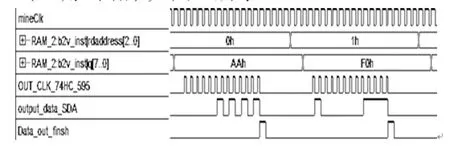

FPGA编码逻辑测试是通过对RAM预置数据再用逻辑分析仪对输出时序进行测试,测试结果如图6所示。

图6 FPGA显存逻辑典型工作时序

第一行mineCLK为数据传输心跳时钟;第二三行为RAM的测试使能时钟;第四行OUT_CLK_74HC_595为12位数据总线的采样时钟,下跳沿时数据有效;第五行output_data_SDA输出为12位,其中低四位位为地址数据,高八位为显示数据;第六行Data_out_finsh为单帧数据发送完结标志。取图12中第二帧数据为例,地址为1h,显示数据为F0h,输出数据对应的12位二进制数为1000_0000_1111;对RAM的预置数据和output_data_SDA输出的时序数据对比分析后,相应地址位对应的数据时序与RAM的预置数据相对应,时序验证均正确。

Web页面的功能控制页面如图7所示,可以看到,该磁流体显示系统支持多种输出风格的网页控制,例如时间、计时倍率、文字以及图案等。此外,通过对该页面反复的输入实验,验证了该网页控制模块的功能性和稳定性。

图7 Web功能控制图

5 结论

本文介绍了一种基于Altera DE1-SOC的磁流体显示系统。该系统突破了传统基于光学的显示技术,能够对各类字形、字体以及图画进行黑白动态的展示,显示内容丰富,展示效果生动。本系统通过web页面将控制数据准确的传递到Linux应用程序,使之调用底层硬件驱动程序将数据传输到HPS与FPGA的AXI总线桥,再通过FPGA逻辑数据地址解析传到硬件显存,最后通过功率驱动将显示图像实时反应到点阵磁极的磁场上,该磁流体显示系统实现了磁性介质显示的远程web页面控制。这不仅丰富视觉显示途径,而且还较好的结合传统国学的水墨文化,促进传统文化的发展。

[1] 姜少义, 李伟力, 李 琳,等. 控制器控制方式对永磁电机电磁场影响的研究[J]. 微特电机, 2015, 43(6):20-23.

[2] 周林富. 模拟信号光耦隔离方法及应用分析[J]. 工业仪表与自动化装置, 1995(3):14-15.

[3] 徐 波. Altera Cyclone V的Linux系统的搭建[J]. 科技资讯, 2014(34):15-15.

[4] 蒋玉萍. 降压型功率变换器LM2596的原理及应用[A]. 全国电源技术年会[C]. 2001.

[5] 童乔凌, 邹雪城, 郑朝霞,等. 电源管理芯片中热关断电路的设计[J]. 微电子学与计算机, 2006, 23(11):152-154.

[6] 徐 严, 陈 勇. PWM DC-DC变换器中电流限制电路的设计[A]. 四川省电子学会半导体与集成技术专委会2008年度学术年会[C]. 2008.

[7] 周林富. 模拟信号光耦隔离方法及应用分析[J]. 工业仪表与自动化装置, 1995(3):14-15.

[8] 曾 东, 陈志明. 基于达林顿管阵列的多路数字量输入电路: CN, CN 202083932 U[P]. 2011.

[9] 翟国富, 崔行磊, 杨文英. 电磁继电器产品及研究技术发展综述[J]. 电器与能效管理技术, 2016(2):1-8.

[10] Techcon A. Broadcom licenses ARM Cortex-A9 multiprocessor core[J]. Eetimes Com, 2014.

[11] 刘 扬, 龚育昌, 李 宏,等. 嵌入式系统网络底层驱动的研究与实现[J]. 计算机工程, 2004, 30(5):111-113.

[12] 邱 铁. Linux内核API完全参考手册[M]. 北京:机械工业出版社, 2011.

[13] 王文植. 驱动多FPGA的实时嵌入式操作系统核心技术研究与设计[D]. 北京:北京工业大学, 2012.

[14] 郑尚志, 陈祖爵, 韩 云,等. Linux中信号量机制研究[J]. 计算机技术与发展, 2007, 17(12):92-95.

[15] 廖裕评,陆瑞强,郭书铭.嵌入式系统设计:ARM-Based FPGA 基础篇[Z].2014.

Magnetic Media Display System Based on DE1-SoC

Zhang Xiong, Zhou Yanling, Zhang Zijia,Zeng Zhangfan

(College of Hubei University,Wuhan 430062,China)

As a new prototype display system, the system based on DE1-SoC Development Board. DE1-SoC operates an improved magnetic Nano-material through controlling the underlying hardware for the specific content. By transplanting Lighttpd, the lightweight Web server and developing Linux program, Linux driver, a custom IP core and Verilog decoding program, networked mobile devices can control the underlying hardware and display system through crossing platform. The system, combined with magnetic fluid and weight, can display dot matrix of some Chinese characters, perfectly reflecting the charm of Chinese characters.

DE1-SoC;magnetic fluid;IP Core;low level driver;display prototype

2016-12-21;

2017-01-19。

国家自然科学基金(61301144;61601175)。

张 雄(1992-),男,湖北荆州人,研究生,主要从事嵌入式智能系统方向的研究。

周艳玲(1981-),女,湖北广水人,副教授,博士,主要从事卫星导航接收技术和信号设计方向的研究。

曾张帆(1983-),男,湖北武汉人,副教授,主要从事下一代无线通信系统方向的研究。

1671-4598(2017)03-0184-03

10.16526/j.cnki.11-4762/tp.2017.03.050

TP23

A