基于FPGA的MDDI数据处理电路实现

2017-03-27魏廷存郑海林

李 勇,魏廷存,郑海林

(1.中国电子科技集团第二十八研究所,南京 210007; 2.西北工业大学 计算机学院,西安 710072)

基于FPGA的MDDI数据处理电路实现

李 勇1,魏廷存2,郑海林1

(1.中国电子科技集团第二十八研究所,南京 210007; 2.西北工业大学 计算机学院,西安 710072)

介绍了一种基于FPGA的MDDI(mobiledisplaydigitalinterface)数据处理电路设计;基于单片集成AM-OLED驱动控制芯片的设计需求以及并行数据总线在移动显示设备上存在的不足,设计了MDDI数据处理电路;MDDI作为一种高速串行移动显示数字接口标准,具有连线数量少,信号传输可靠性高,低功耗等特点,广泛应用于移动显示终端领域;所设计的MDDIType2主端数据处理电路采用两级状态机控制内部电路,主状态机用于控制从状态机的状态切换,从状态机则用于实现MDDI数据的生成;通过加入可配置寄存器,实现对数据包生成和接口模式的控制;采用Verilog语言编写RTL级代码实现MDDIType2数据处理电路软核;使用Xilinx工具综合的结果表明,该数据处理电路能够支持480-RGB×320、26万色的AM-OLED显示屏,数据传输速率可达180Mbps,其性能指标满足系统设计要求。

移动显示数字接口;数据处理电路;有源-有机发光二极管驱动芯片;串行接口

0 引言

AM-OLED(active matrix-organic light emitting diode,有源-有机发光二极管),具有响应速度快、高画质、低功耗以及轻薄的特点,被公认为下一代平板显示的主流技术[1-2]。近年来,随着AM-OLED的制造工艺和量产技术不断进步,AM-OLED已成功应用于手机、数码相机、平板电视等消费类电子产品中。随着显示屏的尺寸、分辨率和颜色数的不断增加,主机与显示屏之间的数据传输量也急剧增加。为此,在手机等便携式显示产品中,面向VESA(video electronics standards association)的高速串行接口MDDI(mobile display digital interface)得到了越来越广泛的应用[3]。

MDDI作为一种新型的高速串行数据接口,具有连线少、传输数据速度快和低功耗的特点,在驱动芯片中作为主机与显示屏之间的高速数据通信接口。根据MDDI协议,主端数据处理电路的功能是,接收微处理器写入的控制信号和数据信号,数据处理电路生成符合协议的控制数据包和显示数据包,并通过LVDS接口发送给MDDI客户端。基于单片集成AM-OLED驱动控制芯片的设计需求,设计了MDDI的主端数据处理电路,可作为IP核应用于AM-OLED驱动控制芯片中。

1 MDDI概述

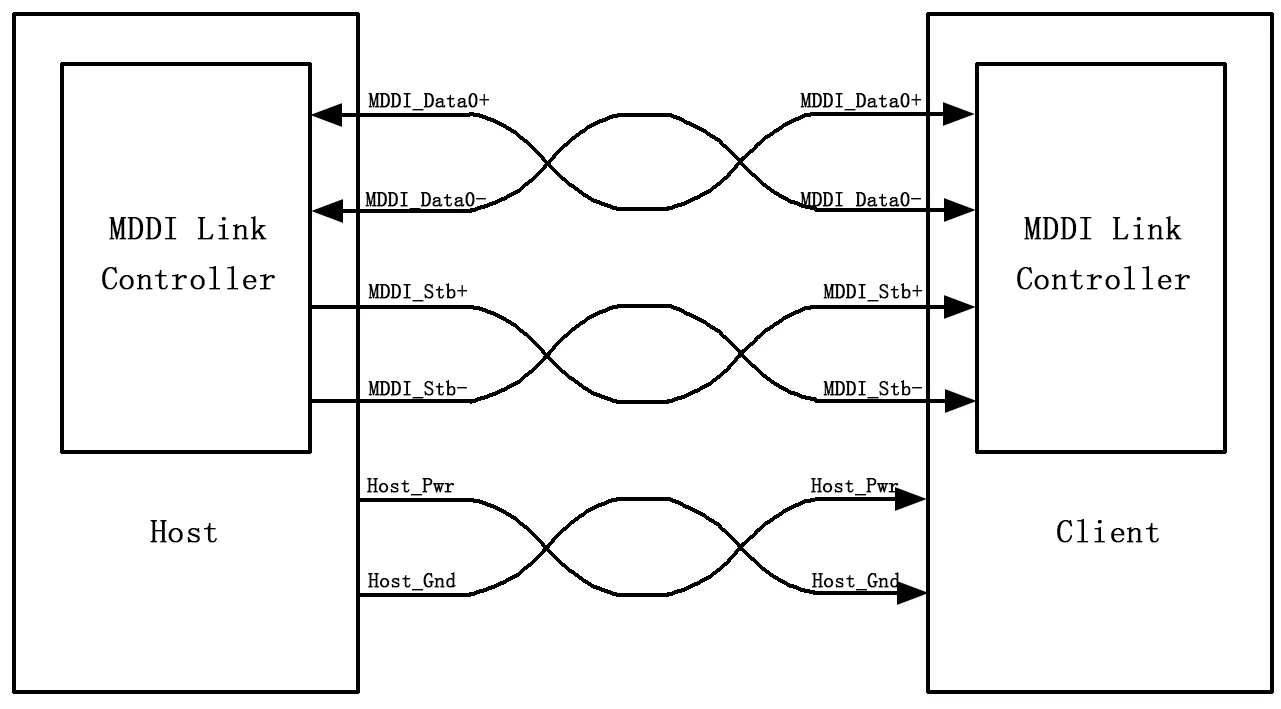

图1所示为MDDI主端和客端连接示意图。数据从主端向客端发送为前向链接,从客端向主端发送为反向链接。MDDI对数据传输的物理层和链接层都做了明确的规定。

图1 MDDI主端和客端连接示意图

物理层上,MDDI采用LVDS(low-voltage differential signaling)技术。与传统的LVDS接口不同的是,MDDI在信号传输之前采用数据-触发编码对时钟进行编码,在通道中实际传输的是数据MDDI_Data0和经过数据-触发编码的MDDI_Stb信号。客端通过将接收到的MDDI_Data0与MDDI_Stb信号进行异或操作,就可将包含在Data0和Stb信号线上的时钟信息恢复,恢复后的时钟信号频率为主端发送频率的1/2。与LVDS接口中直接传输数据和时钟相比,MDDI显著提高了高速数据传输时的抗干扰能力。

链接层上,MDDI协议规定了40多种类型的数据包,这些数据包用于实现包括显示屏在内的许多外设同主机间的数据通信。MDDI数据包由数据包长度、数据包类型、数据和CRC校验位4个部分组成[4]。图2所示为数据包和帧结构。

图2 MDDI的数据包和数据帧结构

根据系统设计的需要,所设计的电路支持5种前向传输数据包与4种反向传输数据包,表1所示为这9种数据包的名称与作用。

表1 驱动控制电路支持的9种MDDI数据包

Video Stream Packet用于传输图像显示数据;Register Access Packet用于初始化寄存器配置信息;Round-Trip Delay Measurement Packet用于测量环路传输延时;Reverse Link Encapsulation Packet用于反向数据的传输;Client Capability Packet与Client Request and Status Packet则是客端发送给主端用于配置主客端链接的数据包。

2 MDDI主端数据处理电路的系统结构

本文设计的MDDI数据处理电路应用于MDDI的主端,它接收MCU写入的图像数据和控制信息,并根据控制信息产生相应的数据包,完成数据发送。图3所示为本文设计的MDDI(Type2)主端数据处理电路的系统结构框图。该系统主要由特殊功能寄存器(SFR)、先进先出存储器(FIFO)、唤醒电路(Wake-up Checker)、链接控制器(Link Controller)、CRC校验电路(CRC Block)、串行发送模块(TX Driver)和并行接收模块(RX Driver)等构成。

图3 MDDI主端数据处理电路结构

MDDI主机可作为IP核挂载在微处理器总线上。微处理器通过地址总线和数据总线将控制信号和数据信号写入MDDI主机,主机产生符合协议的数据包并通过LVDS接口发送给MDDI客户端。控制信号写入特殊功能寄存器,该模块主要用于控制主机系统的接口模式和链接控制模块的数据包生成,配置数据包中相关参数值,如子帧长度、反向链接标识和读写信息等。数据信号则是多媒体数据流,它用于AM-OLED显示。写入FIFO中的多媒体数据以8-bit形式向链接控制模块和CRC校验电路传输。CRC校验电路采用16-bit的循环冗余校验算法产生校验结果,并传输给链接控制模块。链接控制模块根据控制信号生成Sub-frame Header Packet 、Video Stream Packet等6种前向传输数据包,最后以8-bit数据形式写入串行发送模块,经串行化处理后,将数据和数据-脉冲编码信号发送到MDDI客户端。

3 关键模块设计

3.1 数据-触发编码电路(Strobe)

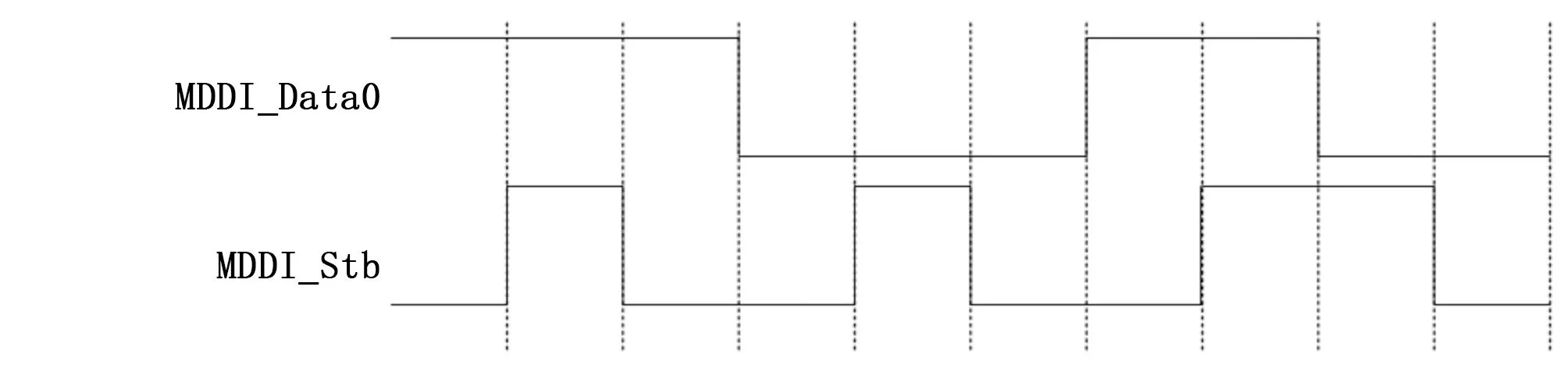

串行数据在发送到LVDS接口之前,需要经过数据-触发编码电路对数据和时钟信号进行编码,实际在LVDS通道中传输的是数据和经过编码的脉冲信号,图4为数据-触发编码电路。其工作原理是:假如输入数据发生改变,则MDDI_Stb保持原状态不变;但如果输入数据未发生改变,则MDDI_Stb发生改变。换句话就是,在每个时钟周期MDDI_Data和MDDI_Stb之间有且仅有一位发生改变,其时序如图5所示。

图4 数据-触发编码电路

图5 数据-触发编码电路时序图

3.2 链接控制器(Link Controller)

链接控制模块用于生成前向链接数据包,同时解析客户端发送的反向链接数据包,根据客户端的解码能力、接口性能等改变主机数据包参数和发送速率,实现主机-客户端链接最优化。该部分是主机数据处理电路的最重要模块。

链接控制模块主要由状态机实现,图6所示为链接控制模块的框图[5]。该状态机由主状态机(Main FSM)、前向链接状态机(Forward FSM)、关断状态机(Shutdown FSM)和服务请求状态机(Service-request FSM)。

图6 链接控制模块框图

链接控制模块读取寄存器堆中相关控制信号用于配置MDDI数据包中的相关参数;读取FIFO中的图像数据生成Video Stream Packet中的Pixel Data部分,最后将生成的数据包发送到串并转换模块。主状态机控制前向链接状态机、关断状态机和服务请求状态机之间的切换,选择其中一种状态机产生MDDI数据包,并通过选择控制信号(TX_Sel)控制选择器的输出。同时,主状态机通过TX_Driver控制驱动器的关断。为了降低设计复杂度,本系统将状态机分为主状态机和子状态机两级实现。

3.2.1 主状态机(Main FSM)

图7为主状态机状态转移图,表2为主状态机跳转指令。系统上电复位后,状态机默认处于休眠状态(Hibernation State),这样保证了内部电路能充分复位,高速驱动器和接收器能进入稳定的工作状态。当特殊功能寄存器中的状态控制寄存器Bit[0]有效时,状态机进入服务请求状态(Service_request State)。主状态机控制服务请求状态机(Service_request FSM)产生链接重启序列,通过选择电路选择服务请求状态机的输出,以唤醒客户端进入链接同步状态。当链接重启序列发送结束,且状态控制寄存器的Bit[1]有效时,链接控制状态机进入前向链接状态(Forward State)。主状态机读取寄存器堆中的相关数据包参数和FIFO中的图像数据,控制前向链接状态机(Forward FSM)产生Sub-frame Header Packet、Video Stream Packet、Round Trip Measurement Packet、Register Access Packet、Reverse Link Encapsulation Packet等前向链接数据包。当前向链接状态结束,状态控制寄存器Bit[7]有效时,链接控制状态机进入链接关断状态(Link-shutdown State),这时主状态机选择关断链接状态机(Shutdown FSM)产生关断数据包关断客户端,使主机和客户端都进入休眠状态,以降低MDDI系统功耗。接下来,文章将详细分析各个状态的转移关系以及相关时序。

图7 主状态机

表2 主状态跳转指令

3.2.2 服务请求状态机(Service Request FSM)

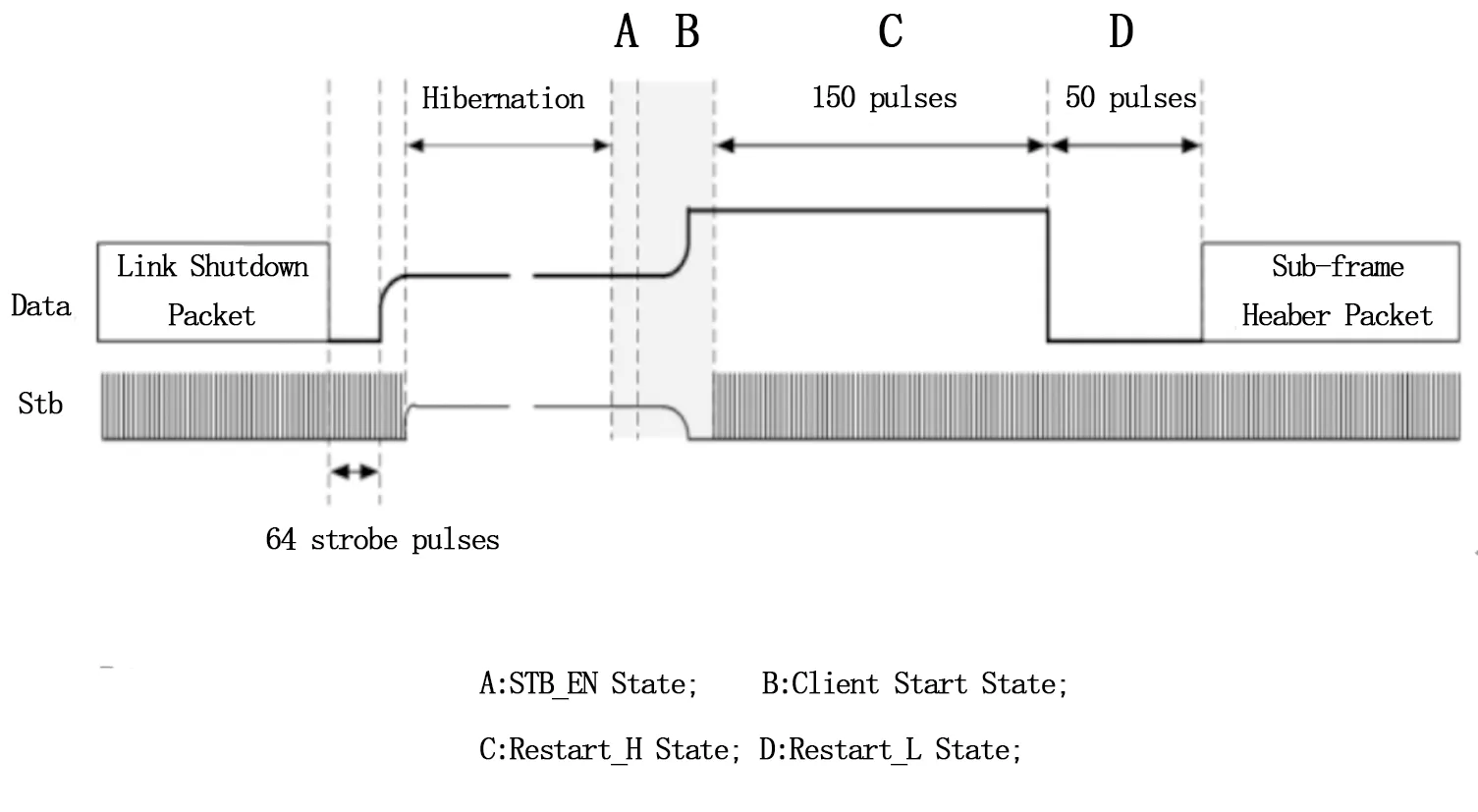

图8所示为服务请求状态机的状态转移图[5],该状态实现MDDI链接的休眠唤醒操作,使主机-客户端之间建立通讯。

图8 服务请求状态机

主机发送关断数据包(Link Shutdown Packet)通知客户端将进入休眠状态,这时主机也切换到低功耗休眠状态。其具体唤醒过程如下所述。

A.在休眠状态下,一段时间后,寄存器堆中状态控制寄存器Bit[0]有效,链接控制模块进入STB_EN状态,开始准备发送链接重启序列;

B.主机发送完一个数据-触发编码信号之后,链接控制模块进入客户端启动状态(Client Start State)。为了使客户端的高速接收器完全开启,主机至少经过200 ns的时间才发送数据-触发信号(使MDDI_Data驱动器能够达到稳定的“1”,MDDI_Stb驱动器达到稳定的“0”);为便于系统控制,本系统延时50个数据-触发信号周期,即50个Stb周期;

C.经过50个Stb周期后,链接控制模块进入重启高电平状态(Restart_H State),这时服务请求状态机产生逻辑高电平数据,使输出MDDI_Data信号逻辑高电平,并维持150个Stb周期,而MDDI_Stb经过数据-触发编码电路产生周期性变化脉冲信号;

D.主机完成150个Stb周期后,链接控制模块切换到重启低电平状态(Restart_L State),服务请求状态机将输出数据置为逻辑“0”,MDDI_Data输出逻辑低电平,并维持50个Stb周期,而MDDI_Stb输出周期性脉冲信号;

E.在完成40个Stb周期后,客户端开始检测子帧头数据包,以实现主机-客户端链接同步。如果暂时无数据,则进入IDLE状态。其链接时序图见图9所示。

图9 服务请求时序

3.2.3 前向链接状态机(Forward Link FSM)

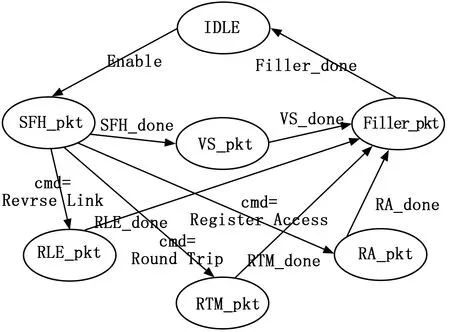

图10为前向链接状态转移图,表3为前向链接状态机跳转指令。该状态机主要用于生成Sub-Frame Header Packet,Video Stream Packet、Reverse Link Encapsulation Packet、Register Access Packet、Round-Trip Delay Measurement Packet等前向链接数据包。

图10 前向链接状态机

表3 前向链接状态机跳转指令

前向链接状态转移具体过程如下:

1)主机完成休眠唤醒之后,当前向链接状态机有效,且主状态机使能信号(Enable)有效,这时链接控制模块进入SFH_pkt状态,开始向客户端发送子帧头数据包,并建立链接同步。前向链接状态机根据寄存器中的值配置子帧头数据包中的参数,并通过串并转换电路发送给客户端;

2)当子帧头数据包完成发送之后,且Reverse Link、Round Trip和Register Access命令无效,这时前向链接状态机默认进入VS_pkt状态模式。VS_pkt状态下,前向链接状态机获取FIFO中写入的图像数据,并按照MDDI协议生成影像流数据包(Video Stream Packet),最后串行发送到客户端;

3)当子帧头数据包发送完,且Reverse Link命令有效时,前向链接状态机进入RLE_pkt状态模式,这时链接控制模块将向客户端发送Reverse Link Encapsulation Packet,使得客户端能根据反向链接标志将反向链接数据包反馈给主机,告知主机当前客户端的接口性能或状态,实现主机最优配置需要;

4)当子帧头数据包发送完,且Round Trip命令有效时,前向链接状态机进入RTM_pkt状态模式。这时链接控制模块将向客户端发送Round Trip Delay Measurement Packet,以测试主机-客户端-主机之间的环路延时,为其他数据包参数或接口提供参考;

5)当子帧头数据包发送完,且Register Access命令有效时,前向链接状态机进入RA_pkt状态模式。这时链接控制模块向客户端发送Register Access Packet,用于读/写AM-OLED驱动芯片中相关寄存器;

当环路测试数据包、寄存器访问数据包、反向链接数据包或者影像流数据包发送结束,前向链接状态机进入Filler_pkt状态模式。链接控制器产生Filler Packet填充在每个数据包之后,以保证数据包的完整性。为了使其他数据包具有最大的灵活性,本系统将该数据包的长度设置为32字节。

3.2.4 链接关断状态机(Shutdown FSM)

图11为链接关断状态转移图。当图像数据发送结束,主机产生链接关断数据包用于关断MDDI连接,以降低主机和客户端的功耗,使其进入低功耗休眠状态。

图11 链接关断状态机

在同步链接状态,如果休眠(Hibernation)指令有效,链接关断状态机开始工作,并产生链接关断数据包。主状态机通过选择电路将链接关断数据包发送给客户端,通知系统将进入休眠状态。

4 整体仿真验证

为了使MDDI接口支持480RGB×320像素、26万色的显示屏,取帧频为60 Hz,则显示数据的传输率为480×320×18-bit×60 Hz=166 Mbps,加上传输其他控制数据,帧格式数据传输需要的最高传输率为180 Mbps。为了验证本文设计的结果,采用Xilinx工具对所设计的Verilog编码进行了综合验证。验证时,采用45 MHz的工作时钟,然后观察内部节点和输出信号。通过对内部节点和输出信号的分析,证明电路系统能正确工作,且满足以上设计需求。

考虑到一帧数据量太大,本文采用一个子帧数据量,结合所设计的客端数据电路对主端数据处理电路进行功能验证。上电复位后,延迟1000个单位时间后,主机开始发送链接唤醒序列,这时MDDI_Data1和MDDI_Data0维持150个MDDI_Stb周期的高电平,然后被置为低电平。这时客户端检测到唤醒序列,开始恢复出时钟信号,无并行数据生成,包分析模块处于空闲状态。在低电平的第50个MDDI_Stb周期时,主机开始发送Sub-frame Header Packet。Sub-frame Header Packet发送结束,主机则向客户端发送Video Stream Packet,其中Video Stream Packet中的像素数据为1080个字节,功能验证如图12所示。

图12 系统仿真验证

5 结论

本文根据MDDI协议,设计了一种用于AM-OLED驱动控制芯片的MDDI主端数据处理电路。该数据处理电路支持9种数据包,在电路中增加可配置寄存器,可支持MDDI的Type I和Type II传输模型的配置。在链接控制模块中,将状态机分为主状态和同步状态,降低了电路实现难度,保证了状态机的健壮性,有利于降低状态跳转中的功耗。采用Xilinx工具的验证结果表明,本文设计的MDDI主端数据处理电路满足MDDI接口设计要求,可以支持480-RGB×320、26万色的AM-OLED显示屏。

[1] 熊文彬. 基于FPGA的OLED显示系统[D]. 成都: 电子科技大学,2011.

[2] 赵湘源. AM-OLED显示屏驱动芯片的研究与设计[D]. 上海: 上海大学, 2011.

[3] 李奇奋,李 妥,陈志良. 用于AM-OLED显示屏控制的MDDI数据处理芯片设计[J].液晶与显示,2011(6):801-807.

[4] VESA Mobile Display Digital Interface Standard[S].Version 1.2, July 9, 2008.

[5] Park J W,Lee K J,Kim J H,et al. An MDDI-Host Architecture with Low Complexity for SoC Platforms[J].IEEE Trans. Consumer Electronics, 2007,53(4):1668-1673.

MDDI Data Processing Circuit Based on FPGA Implementation

Li Yong1, Wei Tingcun2, Zheng Hailin1

(1.28th Research Institute of China Electronics Technology Group Corporation, Nanjing 210007,China;2.School of Computer, Northwestern Polytechnical University, Xi’an 710072,China)

A single chip Mobile Display Digital Interface (MDDI) data processing circuit was implemented based on FPGA. Based on the requirements of monolithic integrated AM-OLED driver IC and deficiency of parallel data bus in mobile display device, the MDDI data processing circuit is designed. MDDI is a high-speed serial digital interface standard, since it has many advantages such as less signal lines, higher signal transmission reliability, lower power consumption and the simpler circuits, it is widely used in the mobile display terminal. This paper proposes a novel design strategy for MDDI Type2 host data processing circuit to reduce the complexity of the circuit. In this design, the internal circuits are controlled with two-stage state machines. The master state machine is used to control the state switch from the secondary machine, and the secondary machine is used for generating MDDI data. The configurable registers control the packets generated and change the interface mode. RTL code of the MDDI data processing circuit is designed using Verilog to implement the soft-core. The synthesized results by Xilinx tools show that, this data processing circuit can support AM-OLED display with 480-RGB × 320 resolution and 260k color image data, the maximum transfer rate is 180 Mbps. The performances of the MDDI data processing circuit meet the requirements of system design.

MDDI; data processing circuit; AM-OLED driver IC; serial interface

2016-10-09;

2016-11-17。

陕西省科技统筹创新工程计划项目(2011KTCQ01-22)。

李 勇(1987-),男,四川内江人,硕士研究生,助理工程师,主要从事模拟与混合信号处理方向的研究。

魏廷存(1960-),男,陕西西安人,博士、教授,博士生导师,主要从事模拟与混合信号处理方向的研究。

1671-4598(2017)03-0172-04DOI:10.16526/j.cnki.11-4762/tp

TN

A