基于FPGA的DDS信号发生器设计

2017-03-21贺军义李男男

贺军义,蒋 坚,李男男

(河南理工大学 计算机科学与技术学院,河南 焦作 454000)

基于FPGA的DDS信号发生器设计

贺军义,蒋 坚,李男男

(河南理工大学 计算机科学与技术学院,河南 焦作 454000)

在FPGA芯片实现的DDS信号发生器已有一定的应用范围,为获得较宽的频率输出范围,一般需要存储相当数量的波形离散值,占用大量的芯片逻辑资源;这篇文章研究在存储较少量的波形离散值的情况下,通过对系统时钟进行分频,减小输出频率最小值,同时提高在低频处的频率分辨率,通过设定频率控制字为存储离散值个数的约数,保证输出波形重构良好、频率失真度低,节约芯片资源;该设计方案可输出多种波形,其中方波占空比亦可调节,将幅度调节设计在模拟运放电路中,可对幅度进行连续调节;整体设计软件化、模块化,易于调整和扩展;经验证,本设计方案可行,达到预期效果,有一定的工程指导意义和实用价值。

DDS;FPGA;Verilog HDL;分频

0 引言

信号发生器作为一种常用的信号调试工具,在诸多领域均有应用,尤其是在电子、通信方面,精度高、频率范围广的信号发生器应用非常广泛。现在常用的信号发生器多采用直接数字频率合成(DDS)技术,很多芯片公司都开发了自己的专用DDS集成芯片[1]。可编程逻辑门阵列(FPGA)芯片的数字逻辑资源丰富、工作频率高、接口丰富,用其来实现的DDS信号发生器具有频率宽度较宽、频率分辨率高、控制方式多样、信号质量良好、成本可控的优点,其应用范围越来越广泛[2]。由于基于FPGA的DDS信号发生器输出最高频率一般只能取到系统时钟的1/3,所以为了输出频率宽度较大,目前常用方法是通过存储离散波形值个数来控制输出频率宽度,即减小输出频率最小值,这就需要在FPGA芯片的ROM表内存储相当数量的离散波形值,占用FPGA大量的逻辑资源,而且在很多情况下,信号发生器输出信号在高频处并不需要和低频处一样高的频率分辨率。如果能在频率失真度有限的情况下,将系统时钟进行分频,则可在存储少量波形离散值的情况下仍能得到较宽的频率范围,且输出频率较低时有很高的分辨率、频率较高时有相对较低的分辨率,同时可设定频率控制字为存储离散值个数的约数,保证输出波形重构良好、频率失真度低,节约芯片资源。本文即研究在FPGA上实现DDS信号发生器,存储较少量的波形离散值,通过对系统时钟进行分频,设定频率控制字,获得较宽的频率输出范围,且输出信号质量良好,系统设计成本低,具有较好的可移植性。

1 DDS原理与设计思路

1.1 DDS原理

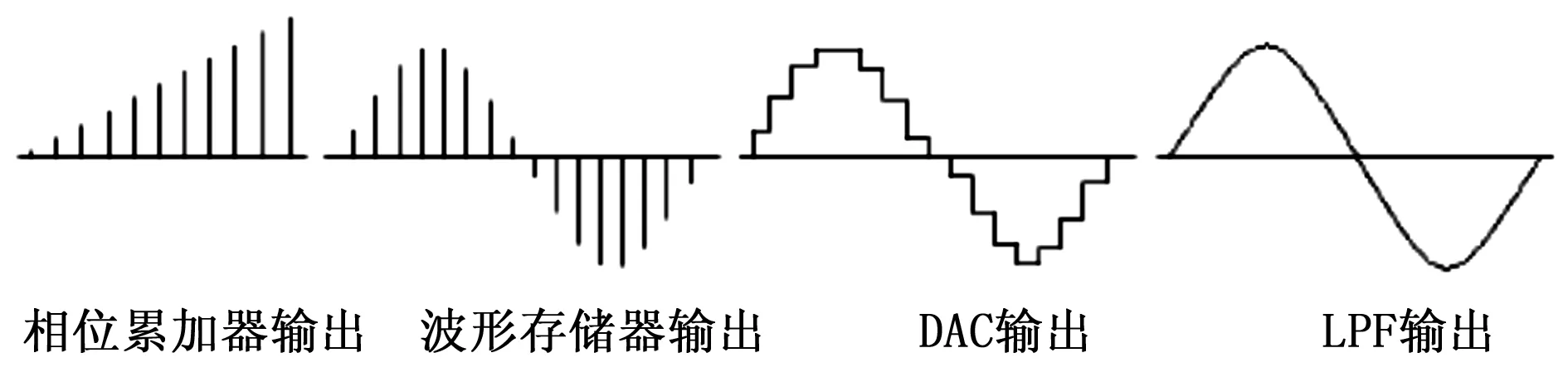

作为第三代频率合成技术,DDS基于抽样定理,从相位角度出发,依据已存储信号的离散值还原信号,实现原理如图1所示。其电路一般包括相位累加器、波形存储器、D/A转换器、低通滤波器等部分[3]。相位累加器由N位加法器与N位累加寄存器级联构成,输入的频率控制字也称相位步进量,是相位累加器的增量。系统时钟F_clk为相位累加器、波行数据读取、D/A转换提供时序控制。由于每个相位都对应一个离散波形值,故每次系统时钟脉冲输入时,离散波形值依次输入至D/A转换器,再经低通滤波器后输出。各阶段输出数据如图2所示。由于相位累加器位数有限,其累加到一定值后,便会产生累加溢出,完成一个周期的相位输出,即完成一个周期的波形数值读取,由此可见,相位累加器的溢出频率即为输出信号的频率。DDS原理的实质就是相位与幅度的映射[3],然后将读取的波形值进行D/A转换输出,DDS技术有以下几个主要参数。

输出频率:

f0=F_clk*K/2N

(1)

频率分辨率:

Δf=F_clk/2N

(2)

相位增量:

(3)

式中,F_clk为系统时钟频率,K为频率控制字,N为全加器位数。

图1 DDS原理框图

图2 各模块输出数据

1.2 系统设计思路

考虑到FPGA芯片内实现ROM表的资源有限,且ROM表的大小随着地址位数和数据位数的增加成指数递增关系,所以在满足输出信号性能要求的前提下,如何节省ROM表资源的开销是一个值得考虑的问题[4]。本研究中每种波形在其一个周期内取512个8位二进制离散值,软件设计部分采用Verilog HDL。为方便方波占空比调节,本设计将4种波形数值统一放在Function函数中,以便对方波波形离散值进行运算。四种波形通过按键进行循环切换。方波占空比通过按键进行循环切换。考虑到因单周期内离散点有限所导致的频率宽度较窄,本例在频率误差允许范围内,先通过按键设定分频系数,对系统时钟进行分频,然后再通过按键调整频率控制字,以便输出较低频率的信号。最终输出频率范围为50 Hz~12.5 MHz,其中在50~200 Hz范围内的频率分辨率可达到1 Hz。从FPGA芯片输出的8位波形信号经D/A转换、低通滤波、运算放大后输出。

1.3 系统总体设计

这篇文章设计的信号发生器,以ALTERA公司的CYCLONE系列芯片EP4CE6F17C8为主控,通过D/A转换芯片AD9708进行数模转换,用7阶巴特沃斯滤波器进行滤波拟合,拟合后的波形幅度可通过运放芯片AD8056构成的运放电路进行调节,所设计的信号发生器可产生方波、三角波、余弦波、锯齿波,各个波形的频率、幅度可调,且方波的占空比可调。通过按键调控,可产生幅度0~5 V、输出频率在50 Hz~12.5 MHz之间、方波占空比0.1~0.9可调的信号。数码管显示波形种类和频率。系统框图如图3所示。

图3 系统框图

2 系统重要模块设计

2.1 波形选择

通过操作按键选择波形控制字,可实现四种波形种类循环切换。每个波形离散值依次用Case语句列于Function函数中。波形切换改变Case语句查找的初始值,各波形控制字对应波形种类及Case语句波形值范围如表1所示。

Verilog语言描述如下:

always @(posedge Pin_Out)

if(!RSTn) i = 1'd0;

else if(i == 3'd3) i = 1'd0;

else i = i+1'd1;

表1 波形值范围

2.2 频率选择

通过按键改变频率控制字和时钟分频系数,从而调节频率。为获得较低的输出频率,在保持输出频率精确度的情况下,对系统时钟进行分频。本文所用FPGA芯片系统时钟为50MHz,一个周期存储离散值512个。当读取波形值的频率为系统时钟时,输出频率:

fo=K*50000000/512Hz

(4)

式(4)中,K为频率控制字,输出频率最小值:

(fo)min=50000000/512=97.656kHz

(5)

当要求输出频率小于系统时钟下的最小值时,需要减小读取波形值的频率,即要对系统时钟进行分频,此时输出频率:

fo=K*50000000/(M*512)Hz

(6)

式(6)中,M为分频系数。考虑到本研究中一个周期存储离散值个数为512,是2的幂级数,所以频率控制字取小于512的2的幂级数(1、2、4、8、16、32、64),这样可在一个周期内读取偶数个对称离散值,波形重构效果较好,频率失真度低。通过设定分频系数,使得当频率控制字为1时,输出波形频率范围为50~200 Hz,步进量为1 Hz,同时输出频率分辨率最高可达1 Hz。

3 相关硬件系统设计

3.1 低通滤波

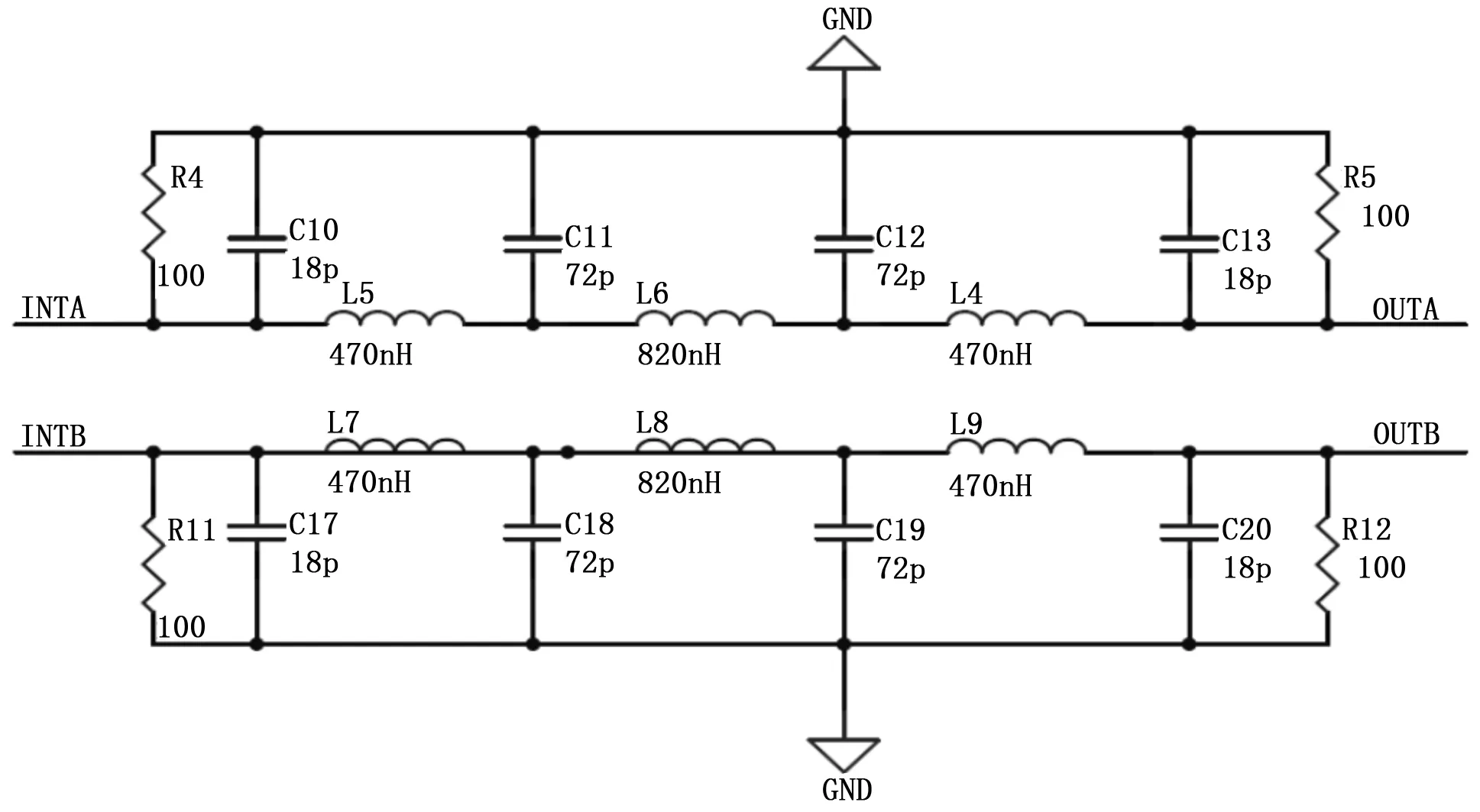

考虑到本设计方案输出频率带宽较大,而巴特沃斯低通滤波器作为一种无源电子滤波器,在通频带内的频率响应曲线非常平坦,能够很好地保持增益的平坦性,特别适用于低频应用,且电路制作容易、成本低,故本系统模拟滤波部分采用7阶巴特沃斯低通滤波器方案,经元器件选型,设计其通频带宽度为40MHz,滤除噪声干扰效果突出,可很好地满足本设计方案的要求。图4为本设计滤波部分原理图。其中INTA、INTB为AD9708模数转换后的差分信号,OUTA、OUTB为两路滤波后的输出信号。

图4 巴特沃斯滤波器电路

3.2 幅度调节

为了使幅度调节方便快捷,本设计的幅度调节采用运算放大方案,使用了2片145 MHz带宽、高性能的运放芯片AD8065,通过电位器调节输出信号幅度。运放采用双电源5 V、-5 V供电,其中-5 V电压由MC34063A反压电路提供。由于本设计使用的D/A芯片是两路差分信号输出,所以两片分别实现差分变单端和幅度调节,同时最大限度地提升了整个电路的性能。在第二个AD8065芯片运放电路中使用阻值为2K的滑动变阻器,即通过调节反馈电阻的阻值来改变输出电压,电压输出范围是-5~5V(10 Vpp),信号稳定,调节方便。本设计幅度调节部分电路如图5所示。

图5 幅度调节电路图

4 系统验证分析

系统设计完成后,将输出信号连接至示波器进行功能模块测试。系统时钟频率为50 MHz,当切换离散信号值的时间为系统时钟周期时,最小输出频率为97.658 KHz。当频率控制字较大时,每个周期读取的离散值有限,由于波形种类不同,其重构效果也不同,即在波形无明显失真的情况下各波形的输出最高频率不同。经验证,在波形无明显失真的前提下,正弦波的最高输出频率可达12.5 MHz,方波的最高输出频率可达1.562 5 MHz,三角波和锯齿波的最高输出频率可达6.25 MHz。表2是对系统时钟下不同频率控制字对应频率失真度分析。对于100 kHz以下频率信号,可先将系统时钟进行分频,再进行频率控制字的调整。表3是将系统时钟分频到25600(50*512)Hz时各频率控制字对应频率失真度分析,表4是将系统时钟分频到102400(200*512)Hz时各频率控制字对应频率失真度分析。

由表2、表3、表4分析可知:当控制字是一个周期所取离散值个数的约数,且每个周期读取的离散值个数为偶数时,输出频率失真度较低,波形质量较好;当控制字不是一个周期所取离散值个数的约数,或者每个周期读取的离散值个数为奇数时,频率失真度比较高。故本研究频率控制字取2的幂级数,输出频率较低时分辨率较高,输出频率较高时分辨率相对较低,始终有较低的失真度,同时大大节省了ROM表资源,验证了本研究设计要求的可行性。

表2 系统时钟下各控制字对应频率及失真度

表3 分频至25600 Hz后各控制字对应频率及失真度

表4 分频至102400 Hz后各控制字对应频率及失真度

5 总结

本研究采用系统分频数和频率控制字可调的设计方案,在存储周期信号离散点仅为512个的情况下,依然可以输出宽频率范围(50 Hz~12.5 MHz)、频率失真度较低、波形重构良好的信号,且信号在低频处分辨率可高达1 Hz,减小了高频处不必要的高分辨率,节省了ROM表资源。系统可输出方波、三角波、余弦波、锯齿波,方波占空比可调。相比于一般的在FPGA上实现的DDS信号发生器,本设计方案的幅度调节采用模拟运放方案,系统可分为数字信号和模拟信号两个模块:波形选择和频率设定部分为数字信号部分,可在线更新配置,也可固化为软核,方便移植;模数转换、滤波、运放(幅度调节)作为一个整体模块,为模拟信号部分,其使用灵活,扩展方便。整个系统设计软件化、模块化,调节、使用、拓展方便,由于占用芯片资源较少、占用接口数量较少,可灵活嵌入到其他系统中。

[1] 陈亚军,陈隆道.基于Verilog HDL的信号发生器的设计[J].电子器件,2011,34(5):525-528.

[2] 高士友,胡学深,杜兴莉,等.基于FPGA的DDS信号发生器设计[J].现代电子技术,2009,32(16):35-37,40.

[3] 黄乡生,杨占才,胡世文.基于DDS和FPGA的信号发生器的设计[J].东华理工大学学报,2009,32(4):390-393.

[4] 余 勇,郑小林.基于FPGA的DDS正弦信号发生器的设计与实现[J].电子器件,2005,28(3):596-599.

[5] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出社,2003.

[6] 谢留婉.简易DDS信号发生器设计与研究[J].电子世界,2016(10):104-105.

[7] 曹郑蛟,滕召胜,李华忠,等.基于FPGA的DDS信号发生器设计[J].计算机测量与控制,2011,19(12):3175-3177,3186.

[8] 邓耀华,吴黎明,张力锴,等.基于FPGA的双DDS任意波发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,30(11):2255-2261.

[9] 阮 围.基于FPGA的DDS设计[D].成都:成都理工大学,2011.

[10] 常高嘉,冯全源.基于FPGA的高速数据采集系统的设计与实现[J].电子器件,2012,35(05):615-618.

[11] 万书芹,陈宛峰,黄嵩人,等.基于改进CORDIC算法实现高速直接数字频率合成器[J].仪器仪表学报,2010,31(11):2586-2591.

[12] 刘 林,田进军,刘朝辉.基于DDS和直接频率合成技术的超宽带捷变频源设计与实现[J]. 兵工学报,2010,31(12):1648-1652.

[13] 刘禄禄.基于DDS的高性能雷达信号发生器的设计和实现[D].西安:西安电子科技大学,2009.

[14] 何 琼,陈 铁,程 鑫.基于FPGA的DMA方式高速数据采集系统设计[J].电子技术应用,2011,37(12):40-43.

[15] 付 扬.基于FPGA的信号源设计[J].工矿自动化,2016,42(7):59-62.

[16] 张 萍.基于DDS的低频信号发生器的设计[J].自动化技术与应用,2016,35(5):106-109.

Design of DDS Signal Generator Based on FPGA

He Junyi, Jiang Jian, Li Nannan

(College of Computer Science and Technology, Henan Polytechnic University, Jiaozuo 454000, Henan, China)

DDS signal generator in the FPGA chip has a certain range of applications. To obtain a wide range of output frequency, the generator need to store a considerable number of discrete values of waveform, which will take up a large number of chip logic resources. We make research on that with a lower amount of discrete values stored, the generator can reduce the minimum output frequency and improve the frequency resolution in the low frequency by dividing system clock. We set the frequency control word to ensure the quality of waveform reconstruction and the low degree of frequency distortion, saving the chip resources. The generator we designed can output a variety of waveforms, and the duty ratio of square wave can be regulated. The amplitude regulation is designed in analog amplifier circuit, so the amplitude can be regulated continuously. The overall design of hardware and software is modular and easy to adjust and extend. It is proved that the design is feasible and achieve the expectation, which means that the design has a certain engineering significance and practical value.

DDS;FPGA;Verilog HDL;frequency division

2016-04-07;

2016-06-21。

博士基金项目(60907023);高校重点项目基金(15A520001)。

贺军义(1982-),男,河南平舆人,讲师,博士,主要从事计算机测试和控制的设计与实现。

1671-4598(2017)02-0231-03

10.16526/j.cnki.11-4762/tp.2017.02.063

TP271+.5

A