图形处理器中图像处理单元的设计与实现

2017-03-07常立博

常立博, 王 琨

(1.西安邮电大学 电子工程学院,陕西 西安710061;2.西安市国土资源信息中心,陕西 西安710061)

图形处理器中图像处理单元的设计与实现

常立博1, 王 琨2

(1.西安邮电大学 电子工程学院,陕西 西安710061;2.西安市国土资源信息中心,陕西 西安710061)

针对图形处理器中关于图像、纹理的传输、偏移、缩放、映射等操作需求,采用具有泡沫挤压功能的流水线结构以及相同功能单元复用的方法,实现了GPU中图像处理流水线。提高了GPU处理图像的速度,同时减少了电路面积。结果表明,在TSMC 0.13 μm CMOS工艺下,电路消耗面积为390 726.09,速度可达200 MHz。现该设计已集成到完整GPU系统中并流片,用经典的测试图像对GPU芯片进行测试:绘制的图像质量与OpenGL的运行结果具有可比性;像素填充率可达80 M像素/s,满足实时处理要求。

图像处理; 图形处理器; 硬件流水线

作为图形显示卡(显卡)的核心,GPU(Graphics Processing Unit)不仅可以实现图形图像加速和实时处理功能,而且已发展成为一种高度可编程的并行处理器[1-2]。图像处理单元作为GPU中三维图形处理的一部分,主要完成图像、纹理和位图数据从帧缓冲区读取以及写入帧缓冲区时所执行的各种操作[3]。这些操作主要包括图像和纹理像素的包装与解包、映射、图像的缩放以及位图的绘制等。在目前高端GPU中,均有针对实现高清图像绘制的专用通道、针对纹理像素的缓存加速部件。可见,图像处理单元是GPU提高图像绘制质量、增强绘制场景真实性的重要模块,具有重要的研究价值和实用意义。

1 相关研究

国外对GPU技术的研究起步早,相对比较成熟。早期以ATI公司推出的M9系列芯片为代表的图形图像处理芯片,包含专用的图像处理单元,可用于图像处理、实现简单纹理处理等功能。目前以NVIDIA和AMD(ATI)两家公司成就最为显著,在GPU市场占据主流。NVIDIA公司在体系架构方面面向通用计算几经演进,从2009年开始先后推出Fermi、Kepler、Maxwell等产品,尤其是GPGPU(General Purpose GPU)模型CUDA(Compute Unified Device Archi-tecture)平台的推出进一步发挥了GPU的数据级并行计算能力。而AMD(ATI)最新的Radeon R9 390X GPU内建2816个流处理器,并且也有类似CUDA的编程模型CTM(Close to Metal)。由于图像处理属于数据密集型运算,GPU系统性能的飞速发展和编程语言灵活性的提高,在增强图像渲染质量、渲染场景真实性的同时,也提升了对复杂场景实时处理的能力。

相对于国外来说,国内对GPU的研究相对滞后,主要研究焦点还集中在GPU应用方面。GPU的核心算法和体系结构也将逐渐成为研究的热点。华南理工大学在ARM+Linux嵌入式平台上基于OpenGL 1.0完成了GPU的建模,涉及到纹理图像操作,但没有进行硬件实现[4]。北大众志微处理器研究中心研发的PKUnity86-3系统,其图形图像子系统可以支持OpenGL ES1.1/2.0和OpenVG标准、同时可实现高清1 080p 30 fps实时解码;长沙景嘉微电子公司研发的JM5400图形处理芯片能够高效完成2D、3D的图形加速功能,支持两路多种格式的外视频在图形上进行开窗、缩放、旋转以及叠加显示。西安邮电大学从2009年开始自主研究GPU,目前基于OpenGL1.5,已经完成嵌入式图形处理器芯片--“萤火虫1号”的系统级芯片测试。本文设计的图像处理单元是“萤火虫1号”的一部分,系统级芯片测试表明:图像处理单元功能正确,并且为系统进行实时动态渲染提供支持;在TSMC 0.13 μm CMOS工艺下,速度可达200 MHz,满足设计需要。

本文主要包括以下几个方面:首先介绍图像处理单元的设计思想;其次提出图像处理单元的硬件结构及主要模块的实现方法;最后介绍本文设计的验证方案及结果。

2 图像处理单元的设计思想

GPU中图像处理单元主要完成图像、纹理像素的相关操作以及位图的绘制。一个完整的图像处理单元的工作流程如图1所示[5-8]。

图1 GPU中图像处理的工作流程

在图像处理单元中,主要传输通道以及像素在各传输通道传输过程中的操作包括:

(1)从帧缓冲区到处理器内存。用于将图像(不包括纹理图像)从帧缓冲区读取到处理器内存,主要经过像素传输(像素值缩放与偏移)、像素存储格式的转换、像素的包装等操作;

(2)从处理器内存到帧缓冲区。本通道包含两条支路:一条支路经过像素解包、像素存储格式的转换、光栅化、片断操作,用于完成位图的绘制;另一条支路经过像素解包、像素存储格式的转换、像素传输、光栅化、片断操作,用于将图像(不包括纹理图像)从处理器内存写入帧缓冲区;

(3)从一个缓冲区复制到另一个缓冲区或同一缓冲区的其他位置。完成图像(不包括纹理图像)在帧缓冲区之间的移动,主要经过像素传输、光栅化和基于片段的操作;

(4)帧缓冲区到纹理内存。用于将纹理图像从帧缓冲区读取到纹理内存,主要经过像素传输操作;

(5)纹理内存到帧缓冲区。用于将纹理图像从纹理内存写入帧缓冲区,主要经过光栅化和基于片断的操作。

由上述分析可以看出:图形处理器中图像处理单元数据通道众多、而处理的数据多是图像类的大块数据。针对这一问题,本文提出一种具有泡沫挤压功能的流水线结构,在该流水线结构中各个传输通道相同的数据处理操作复用,不同操作采用多路选择器来旁路。因此这种结构既提高像素的处理速度,又可以最大程度的降低电路面积。对于需要在数据通道选择和功能选择时采用控制电路实现对于功能专一模块采用ASIC的设计方法实现。

3 图像处理单元的设计与实现

根据上一节分析,将GPU中图像处理单元划分成如下8个主要子模块,整体硬件结构如图2所示,其中虚框内为本设计所包含的子模块及连接关系,虚线框外为本设计的外围模块。各子模块功能如下:

(1)解码器模块。对命令处理单元发来的命令进行解码。判断当前命令是否为本单元要处理的命令,如果是,则存储相应参数;反之,则不对这条命令进行处理,并透传给GPU流水线的下一级;

(2)控制模块。根据解码器存储的命令参数和其他单元电路的工作状态控制运算模块,产生与GPU中相关单元电路(DMA单元,帧缓冲区单元,内存管理单元)的通信信号,完成数据交互功能;

(3)主流水线模块。在控制模块的控制下,接收原始图像信息(从DMA单元或帧缓冲区单元),完成图像的读取、写入、复制、缩放等操作,并将处理后的像素信息发送到GPU系统中的相关单元(像素输出控制单元,GPU内存或DMA单元);

(4)参数存储模块。如果GPU系统处理的是glPixelTransfer或 glPixelZoom命令,图像处理单元的控制模块启动参数存储模块,并将glPixelTransfer命令中的像素偏移因子或像素缩放因子存储到相关寄存器,或将glPixelZoom命令中的缩放因子存储到相关寄存器;

(5) 像素映射模块。如果GPU系统处理的是glPixelMapv命令,图像处理单元的控制模块启动本模块,将像素映射表存储到相关RAM中,当进行像素映射操作时,根据主流水线模块计算出的像素地址信息,本模块计算出对应的映射像素信息,完成像素映射操作;

(6)运算参数堆栈模块。当GPU系统进行压栈操作时,图像处理单元的控制模块启动本模块将像素偏移因子、像素缩放因子和图像缩放因子压入堆栈中,如果堆栈已满时,系统再进行压栈操作,则发出上溢信号;当GPU系统进行弹栈操作时,图像处理单元的控制模启动本模块将像素偏移因子、像素缩放因子和图像缩放因子从堆栈中弹出,并将这些信息写入到对应寄存器。当堆栈已空时,如果系统再进行弹栈操作,则发出下溢信号;

(7)位图处理模块。在控制模块的控制下,从DMA单元接收位图信息,完成位图绘制操作,并将处理后的图像信息发送到像素输出控制单元;

(8)卷积过虑模块。在绘制图像过程中,如果启动了卷积过滤功能,则主流水线模块处理后的图像信息输入到本模块,本模块完成图像的卷积过滤操作后,再将图像信息发送到像素输出控制单元。

图2 图像处理单元整体结构

3.1 数据处理模块

关于不同流水级之间的数据交互,通常是采用FIFO[9]。考虑到流水级的数量较多,如果采用FIFO进行数据交互,则需要消耗大量芯片面积;在GPU图像处理流水线中,每一级输入数据不一定每一时钟都到达,并且多个输入到达时间未必相同,各级流水线容易产生泡沫,造成资源浪费和性能降低。综合权衡面积和效率因素,数据处理模块采用带泡沫挤压功能的双轨握手协议实现不同流水级的互连以提高整体性能,同时减少芯片面积,如图3所示。

图3 泡沫挤压双轨握手协议形式的接口

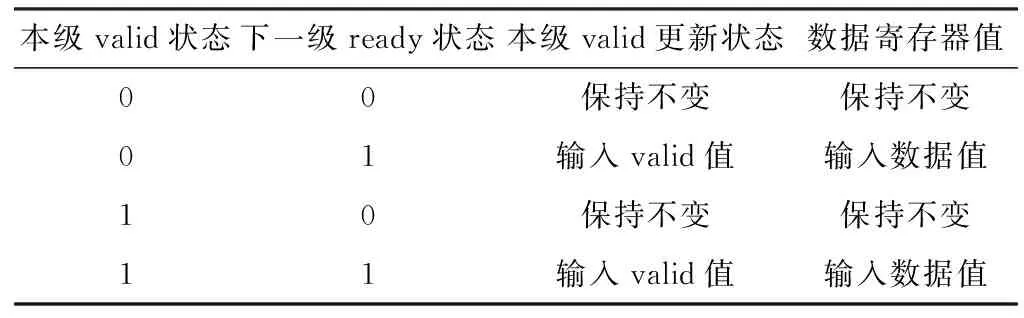

各个流水级的输入和输出采用valid和ready控制信号,其中valid信号表示数据线上是否有数据;ready信号表示本单元是否可以接受数据。当数据信号data到达时,控制信号valid应该是1;当没有数据信号时,控制信号valid应该是0。在不同的输入控制信号组合时,valid寄存器和数据信号反应如表1所示。

表1 泡沫挤压双轨握手协议接口信号反应

图4 数据处理模块体系结构

采用泡沫挤压双轨握手协议形式的接口互连和各个传输通道数据处理的相同操作复用、不同操作采用多路选择器来旁路的设计方法实现的数据处理模块体系结构如图4所示,虚线部分为采用泡沫挤压双轨握手协议形式实现的流水线控制结构。信号data_fb表示来自帧缓冲区数据位宽为128位的数据,data_dma表示数据位宽为32位来自DMA的数据,data*表示位宽为32位的流水线各级输出数据,valid*表示流水线各级输出数据的有效信号,ready*表示流水线各级是否需要停顿,zoom_en表示是否需要启动图像缩放功能,map_en表示是否需要启动映射功能。流水线各级所完成的功能如下:

第一级对输入的不同位宽数据进行格式转换,使输出的像素均为32b位的统一位宽;

第二级完成像素传输操作中的像素值偏移操作;

第三级完成像素传输操作中的像素值缩放操作;

第四级完成对整幅或部分图像与纹理的缩放;

第五级根据像素映射表内容,完成颜色索引功能。

3.2 控制模块

控制模块是图像处理单元的核心模块,除完成对本设计其他功能模块的控制外,还要根据各功能模块的反馈信息与外围单元(DMA、DDR2、译码单元、帧缓冲区、扫面转换)进行通信。由于GPU中图像处理单元的传输通道比较多,使得控制比较复杂,因此本文采用状态机完成控制模块的设计[10],控制模块的状态机示意图如图5所示。

图5 控制模块状态机

其中,各个状态的说明如下:

(1) IDLE。此状态为空闲状态,等待接收命令。当没有接收到本单元要处理的命令时,在此状态下,图像处理单元处于空闲状态,不进行任何操作;如果接收到本单元要处理的命令,则命令中的参数存储到相关寄存器中;

(2)RECEIVE_1。如果一条OpenGL命令需要两条指令或三条指令才能传送完成,则此状态等待接收命令的第二部分,一旦接收到命令的第二部分,将命令中的参数存储到相关寄存器中;

(3) RECEIVE_2。如果一条OpenGL命令需要三条指令才能传送完成,则此状态等待接收命令的第三部分,一旦接收到命令的第三部分,将命令中的参数存储到相关寄存器中;

(4) SEND_PARA。根据相关命令参数,向相邻单元发送数据交换请求信号,并等待相邻模块完成处理数据的准备工作和请求应答信号,一旦接收到应答信号,则进入图像处理阶段;

(5) SEND_ONE_IDLE。完成参数存储或堆栈操作的功能。如果处理的是glPixelTransfer命令或glPixelZoom命令,则将相关参数存储到寄存器中;如果处理的是堆栈操作命令,则完成堆栈操作;

(6) BITMAP。和相邻单元建立数据传输通路后,产生启动位图处理信息,由位图处理模块完成位图绘制的功能;

(7) WAIT_FIFO。等待相邻模块输入数据。如通过DMA单元从CPU内存读取要处理的像素信息,且此时用于缓存DMA单元输入数据的FIFO为空时,则流水线停顿,在此状态等待DMA单元写数据;如通过帧缓冲区单元读取要处理的像素信息,且此时用于缓存帧缓冲区单元输入数据的FIFO为空时,则流水线停顿,在此状态等待帧缓冲区单元写数据;

(8) PIPELINE。当相关输入缓存FIFO中有要处理的图像信息时,在此状态下,发出启动流水线信号,由主流水线模块完成设置像素偏移和像素缩放,图像缩放及像素映射的功能;

(9) PIXELMAP。当处理glPixelMap命令,且用于缓存DMA单元输入数据的FIFO不为空时,启动像素映射模块完成像素映射表的存储功能。

4 综合与验证

为了验证本文设计的正确性和实用性,本文分别进行了综合、基于FPGA的模块级验证及基于西安邮电大学“嵌入式图形处理器(GPU)芯片-萤火虫1号”的系统级测试。

4.1 综合结果

采用Synopsys公司的Design Compiler工具,使用TSMC 0.13 μm库单元中的typical元件,在包含线上延时条件下,本设计得到的速度和面积指标如表2所示。

表2 电路性能指标

4.2 模块级验证方法及结果

本文采用Xilinx的Zedboard开发平台构建硬件加速验证平台,实现模块级验证。具体开发借助Xilinx公司的Vivado集成开发环境实现,Zedboard开发平台上Zynq FPGA芯片分为SoC处理器系统(Processor Systerm,PS)和片上可编程逻辑(Programmable Logic, PL)组成。PS部分包括两个ARM Cortex-A9 MPCore微处理器、基于AXI标准的片上互联总线和存储控制器。PL部分通过多个ARM AMBA AXI端口和PS部分连接起来。在本文的设计中,处理器完成外设控制、下发和收集数据以及特定数据处理功能。AIX4总线将包括图像处理单元在内的外设同处理器有机连接起来,将测试软件产生的激励输入到输入同步器,UART模块将输出同步器收集到的测试结果传送给软件验证环境,具体结构如图6所示[11-13]。

图6 验证平台结构

该硬件加速验证平台中各部分功能说明如下:

(1)参考模型。本验证方案采用System Verilog语言描述图像处理流水线周期精确的参考模型,为被测设计的自动检查提供一个黄金参考;

(2) 比较器。该模块用于将硬件加速器的运算结果和参考模型的运算结果做周期精确比较。如果两者的结果有差异则给出对应错误提示;

(3)ARM处理器。该模块用于管理图像处理单元和外部设备,并提供用软件访问被测设计的方法;

(4) AXI总线控制器。该模块用于将ARM Cortex处理器和外部设备连接起来,完成处理器和各外部设备之间的通信功能。

(5)UART模块。该模块将测试激励从外部软件传送到硬件加速平台的片上FIFO中,以及将硬件加速平台的片上FIFO中的运算结果传送到外部软件;

(6) 包装后的图像处理单元。为了便于从软件终端向被测电路送入测试激励,并把被测电路的运算结果送回到软件终端,在被测电路、输入和输出均增加一个FIFO缓存数据。这样可以避免因软硬件速度不匹配而导致数据丢失的问题。

经验证,图像处理单元设计和其周期精确的模型接口时序是完全一致的。由于图像处理单元的传输通道中,从处理器内存到帧缓冲区所经历的处理单元是最完整的,所以本文以这条通道的验证结果来说明设计的正确性。待处理图像与经历从处理器内存到帧缓冲区传输通道(像素值偏移设置为2,像素值缩放设置为0.25,图像行和列均缩小2倍)后的图像分别如图7所示。

图7 原始图像与帧缓冲区传输通道后的图像对比

4.3 系统级测试

为了进一步验证本文设计的正确性和实用性,设计作为嵌入式图形处理器(GPU)芯片(“萤火虫1号”)的一个子模块,基于该芯片对本文设计进行系统级测试,整个GPU系统可在时钟频率200 MHz时稳定工作。因为本模块采用完全流水的设计,所以在理想情况下像素填充率可达200 M像素/s。在实际测试中,由于GPU各级存在数据等待的情况,所以统计结果显示约每10个时钟周期可以处理4个像素,像素填充率可达80 M像素/s。图8所示为萤火虫图形处理系统与图像处理单元相关的部分渲染结果。图8(a)所示为GPU系统执行glCopyTexImage2D相关命令,完成从帧缓冲区复制一个先前绘制的四边形作为纹理数据,再经过图像处理单元及纹理处理单元给一个矩形图元贴图,最后再绘制到帧缓冲区;图8(b)所示为GPU系统执行glCopyPixels相关命令,完成从帧缓冲区中的一个矩形区域(它的)复制像素数据,数据被复制到帧缓冲区的一个新位置; 图8(c)所示为GPU系统执行glDrawPixels及glPixelZoom命令,从CPU内存中读取一幅图像并放大两倍绘制到帧缓冲区;图8(d)为GPU系统执行glBitMap相关命令,完成位同绘制。图8(e)为添加纹理贴图后的旋转木箱,在木箱的每一个面上贴不同的纹理;图8(f)为绘制一幅复杂图像,并将其作为环境纹理包裹在3D模型上,让它看起来像反射了周围的场景一样。

图8 GPU芯片与图像处理单元相关的部分渲染结果

5 结束语

本文针对GPU中的图像处理单元做了深入的研究,并基于OpenGL对图像处理进行了硬件电路设计和验证工作。通过对GPU中图像处理单元关键技术的研究,可为国内自主GPU设计奠定理论基础。以后

需要继续完善的工作有:

(1) 根据现有的图像处理算法,采用专用处理器的设计方法,提取设计出适合图像处理算法的指令集,以实现更高效、更灵活的图像处理单元[14];

(2) 研究现代GPU处理中复杂的图像处理算法:如颜色表替换,图像信息统计等,以完善图像处理器的功能。

[1] 吴恩华,柳有权. 基于图形处理器(GPU)的通用计算 [J]. 计算机辅助设计于图形学报,2004,16(5):601-612.

[2] 韩俊刚,刘有耀,张晓.图形处理器的历史现状和发展趋势[J].西安邮电学院学报,2011,16(3):61-64.

[3] Owens J D, Houston M, Luebke D, et al. GPU Computing[J]. Proceedings of the IEEE, 2008, 96(5):879-899.

[4] 黄伟钿.面向移动平台的3D图形处理器的设计[D].广州: 华南理工大学,2011.

[5] Shreiner D.OpenGL编程指南[M].7版.李军,徐波,译.北京:机械工业出版社, 2010.

[6] Samuel R B.3D computer graph-ics[M].3rd ed.Beijing:Tsinghua University Press,2006.

[7] Angel E.Interactive computer graphics: a top-down approach using OpenGL[M].4td ed.Beijing: Tsinghua University Press,2006.

[8] Richard S,Wright Jr,Nicholas Haemel,et al. OpenGL超级宝典[M].5版.付飞,李艳辉,译.北京:人民邮电出版社, 2012.

[9] Seng L S,Parameswaran S.Design methodology for pipelined heterogeneous multiprocessor system[C]. MA,USA:IEEE Design Automation Conference,IEEE,2007.

[10] 杜慧敏,李宥谋,赵全良.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学社,2006.

[11] Ruan A,Wang Y,Shi K, et al. SOC HW/SW co-verification technology for application of FPGA test and diagnosis [C]. Hong Kong:International Conference on Computational Problem-Solving (ICCP),IEEE,2011.

[12] Xu Huang,Liu Lintao,Li Yujing,et al. FPGA verification methodology for SiSoC based SoC design [C].Beijing:International Conference of Electron Devices and Solid-State Circuits (EDSSC),IEEE,2011.

[13] Spear C,Tumbush G.System Verilog for verification.A guide to learning the testbench language features [M].Germany:Springer Ebooks,2009.

[14] Shreiner D,Woo M,Neider J,et al.OpenGL编程指南[M].8版.王锐,译.北京:机械工业出版社,2014.

Design and Implementation of the Image Processing Unit in GPU

CHANG Libo1, WANG Kun2

(1. School of Electronic Engineering, Xi’an University of Posts & Telecommunications, Xi’an 710061, China;2.Information Center of Land and Resources in Xi’an, Xi’an 710061, China)

In view of the image and texture processing requirements of graphics in Graphic Processing Unit (GPU), this paper proposes an image processing pipeline with foam extrusion function and multiplexing same function unit, thus improving the speed of image processing while reducing the circuit area. The design was synthesized under TSMC 0.13 um CMOS technology by Synopsys Design-Compiler. The frequency of this design is up to 200 MHz at a circuit area of 390726.09. The design is integrated into a complete GPU system and the results are comparable with the operation results of OpenGL. The pixel fill rate is 80 Mpixels/s, which meets the requirements of real-time processing.

image processing; graphic processing unit; hardware pipeline

2016- 04- 01

国家自然科学基金重点项目(61136002);陕西省科技计划资金资助项目(2011k06-47)

常立博(1985-), 男, 博士研究生, 助教。研究方向:ASIC设计,GPU开发。王琨(1988-), 女, 硕士, 工程师。研究方向:GPU软件开发。

10.16180/j.cnki.issn1007-7820.2017.02.005

TP391.41

A

1007-7820(2017)02-016-06