基于SRIO的LTE-A基带系统接口设计

2017-03-02张德民

张德民,张 巍,薛 尧

(重庆邮电大学 光电工程学院,重庆 400065)

基于SRIO的LTE-A基带系统接口设计

张德民,张 巍,薛 尧

(重庆邮电大学 光电工程学院,重庆 400065)

针对TD-LTE-A射频一致性测试仪中传统的EMIF并行接口已经不能满足芯片间大量数据交互的需求,提出了一种串行高速输入输出的设计方案。实现了基带系统中DSP芯片和FPGA芯片间的互连,对此进行仿真测试并在基带系统中进行了板级验证。结果证明了整个传输方案在实际应用中的正确性与可行性,并且得出SRIO平均传输速率为2.09 Gb/s,满足芯片间大量数据交互的需求。

LTE-A;SRIO;FPGA;DSP

0 引言

随着LTE-A诸多创新技术的应用[1],系统对数据的处理能力要求越来越高,与此同时高速数字信号处理( Digital Signal Processor,DSP) 以及大规模现场可编程门阵列( Field Program-mable Gate Array,FPGA) 也被广泛应用。由于串行高速输入输出口( Se-rial Rapid IO,SRIO) 接口具有占用的IO资源少、传输速度快以及抗干扰能力强等优点,所以带来了更高的性能、更低的成本和更简化的设计[11]。SRIO 接口已经成功应用在多种嵌入式系统的数据互连[3]。目前大部分TD-LTE -A系统采用的是多处理芯片的结构,因此亟需一种新的高速接口来满足系统芯片间高速数据交互的要求。在深入研究 SRIO 协议及相关技术后,设计了一种可靠的互连协议标准,实现 DSP芯片与 FPGA 芯片之间的数据传输方案,在提高数据交互能力的同时,分析其传输时延。结果证明其满足了TD-LTE-A射频一致性测试系统的性能要求。

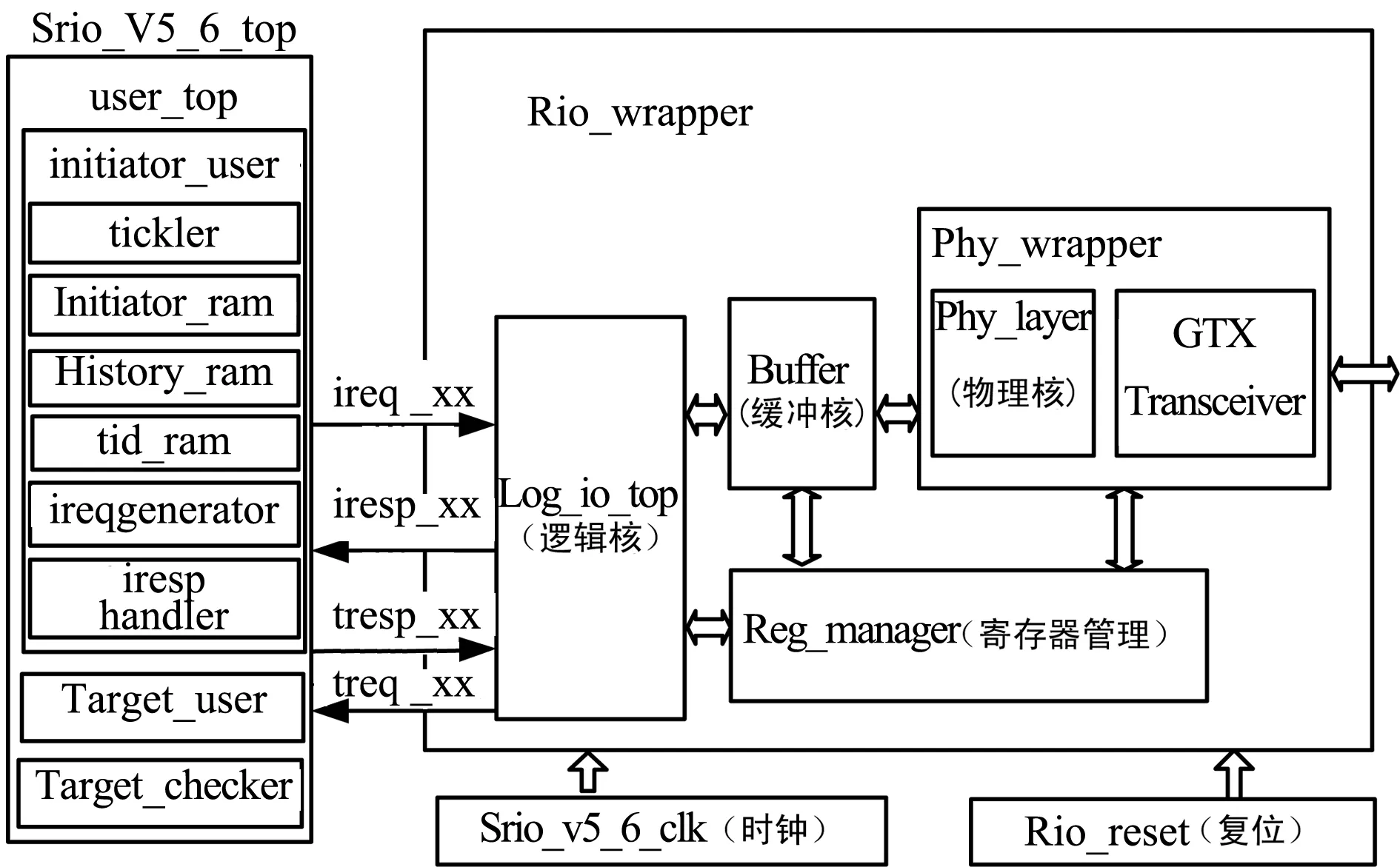

1 基于FPGA的SRIO设计

该方案采用的FPGA芯片是Xilinx公司Virtex-6 系列XC6VLX475T。在FPGA端,通过调用IP核实现SRIO接口的传输层与物理层,逻辑层需要用户自己根据项目需求进行设计、修改与实现[4]。如图1所示,核工程由Rio_wrapper(包含逻辑层核、寄存器管理模块、缓冲核和物理层wrapper)模块、时钟模块及复位模块等模块组成。

逻辑层核由用户接口、链路接口和维护接口组成,用户可以通过维护接口对逻辑层的配置寄存器进行读写,从而配置SRIO的工作模式。缓冲核在SRIO协议中负责数据包的缓存。物理层核实现了SRIO物理层协议[5],其主要完成CRC校验、8B/10B编码或解码以及缓冲器核的缓冲区管理等功能[6]。

图1 SRIO核工程图

SRIO核工程是基于虚拟IO模块的示例工程,该工程是仅仅可使用户在开发板上对SRIO的各种传输机制进行验证[8],当SRIO需要进行新的操作(事务类型改变)时,用户则需要手动调整代码。这种事务类型的配置方式很不灵活,不适合在实际工程中应用。因此,基于实际项目的需求,方案对核中的user_top模块进行了设计与改进,下文将从以下几个方面对SRIO的设计进行详细介绍。

1.1 逻辑层协议设计与实现

1.1.1 信令与数据区分的方案设计

基带系统基带板不仅有数据交互,还有信令交互,如DSP需要向FPGA的小区搜索模块下达小区同步命令;FPGA需要向DSP汇报小区搜索结果:小区ID组号、ID组内号等。信令量远远小于数据量,但信令的重要性却高于数据,设计合理的用户协议决定了该工程能否适应于当前项目。SRIO提供了17种事务类型,有2种写事务类型:NWRITE和SWRITE,SWRITE的速率高于NWRITE,因此NWRITE事务一般适用于数据量较小的情况,而SWRITE适用于数据量较大的情况。信令调用NWRITE发送,数据使用SWRITE发送,这样就很容易区分数据帧的类型。

这种方案具备几下几点优势:① 不占用数据段空间,不会降低SRIO的传输速率;②只需知道格式包类型就可以知道数据类型,有利于简化工程开发难度;③ 可移植性强,不需根据硬件不同而修改地址段。

1.1.2 信令与数据发送优先级的方案设计

信令的量虽然少,但它是系统选择工作模式的重要依据。在此采取类似于单片机中断的方法来体现其优越性与重要性,即当有信令需要发送时,优先发送信令,所谓的优先是:如果有数据帧正在发送,则等该数据帧发完,立马发送信令;否则立马发送信令。

1.2 时钟和复位设计

时钟模块的外部输入时钟只有2种频率,分别为125 MHz和156.25 MHz,不同时钟频率对应着接口不同的传输速率,SRIO协议规定了输入时钟与带宽之间的关系[7]。

在基带验证平台中,DSP端的SRIO工作时钟为156.25 MHz,因此FPGA端的SRIO外部输入时钟也设为156.25 MHz[10]。

在原有的SRIO IP核工程中,主要有2个外部输入的复位信号,它们分别是local_reset和link_reset,而接口内部的复位操作就比较复杂。在实际应用中,复位信号过多势必会增加工程应用的难度,使复位花费的时间过长,从而影响整个方案所设计的SRIO接口模块在项目中高速数据收发的性能。因此,方案将核工程顶层模块的2个外部复位信号local_reset和link_reset合二为一,并利用该复位键对内部各模块复位信号进行直接复位处理,使SRIO上电后能快速进入准备就绪的状态,这样可极大简化SRIO的复位处理[12]。

1.3 触发方式设计

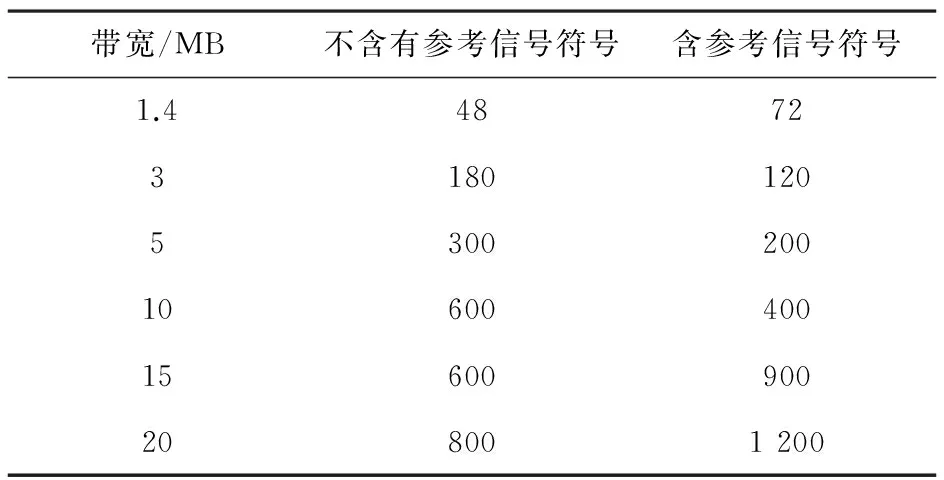

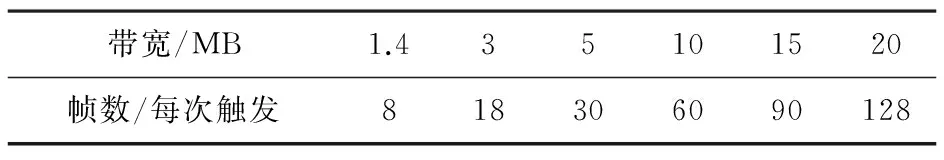

整个方案以“TD-LTE-Advanced系统试验设备开发”为项目背景,设计并改进了SRIO的触发方式。LTE-A系统支持6种不同的带宽(1.4、3、5、10、15、20 MB),每帧含有10子帧,每个子帧包含14个符号[17],每个符号含有的有效子载波数如表1所示。

表1 有效子载波数

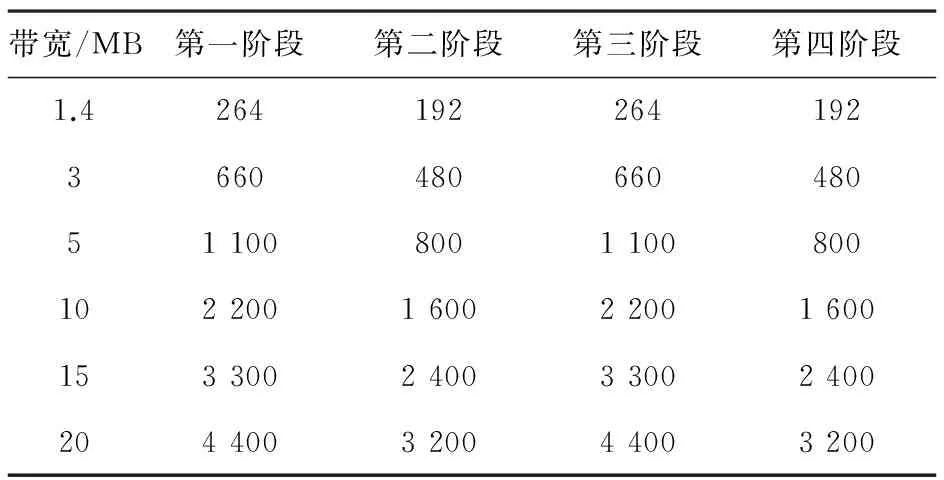

在LTE-A系统中,往往以子帧为单元进行上下行分配,在接收端以子帧为单元进行FFT等操作。实现一个子帧信号检测数据传送采用如下方式:在一个子帧中,分几个阶段把数据发送出去。由于SRIO每帧最多发16个双字,不同带宽每个符号的有效子载波数不同,而且也不全是16个双字的倍数。这种方式传送的时机恰当,既能减少时延,也能降低冗余量,还能把冗余放在子帧数据的末尾,降低DSP对接收数据的处理难度。根据工程中信号检测的流程(参考信号位置),将数据传输分为4个阶段,符号0、1、2、3第一阶段,符号4、5、6第二阶段,符号7、8、9、10第三阶段,符号11、12、13第四阶段。

1.4 一次触发传输的数据量

1.3节设计了SRIO的触发方式,接下来亟需解决的问题是如何确定每次触发要发送的帧数与每帧的双字数。以常规循环前缀(Cyclic Prefix,CP)下的无线帧为例说明触发量的设计方案。常规CP下,每个符号的有效子载波数如表1所示,根据1.3节的4个阶段触发方式以及表1,可以计算出每个阶段要发送的有效数据量,如表2所示。依据表2以及大量的测试得到每次触发发送的帧数如表3所示。

表2 每个阶段的有效数据

表3 每次触发发送帧数

2 基于DSP的SRIO设计

根据前文的介绍,在“TD-LTE-A系统试验设备开发”项目中,FPGA需要将几个过程处理后的数据通过SRIO发给DSP,同时,DSP也要发送一些信令个FPGA[9]。需要强调的是,第2节设计的SRIO是FPGA与DSP均可作为主发器件或目标器件。因此,在DSP端应尽快完成SRIO的硬件驱动,使SRIO上电后尽快进入准备就绪的状态。

在DSP TMS320C6455芯片上,SRIO的相关控制寄存器分布在地址0x02D00000至0x02D3FFFF空间上。接下来将对几个重要的控制寄存器加以说明: SRIO有4组装载存储单元(Load Store Unit,LSU)寄存器组,即LSU1-LSU4,其负责IO数据包和维护数据包的发送,寄存器BLK1_EN的第0位是其使能位。内存访问单元(Memory Acess Unit,MAU)寄存器负责控制IO数据包的接收,由寄存器BLK2_EN的第0位使能。TXU负责Message(消息事件)数据包的发送,RXU则负责该事件的接收,它们分别由寄存器BLK3_EN的第0位与寄存器BLK4_EN的第0位使能[2]。

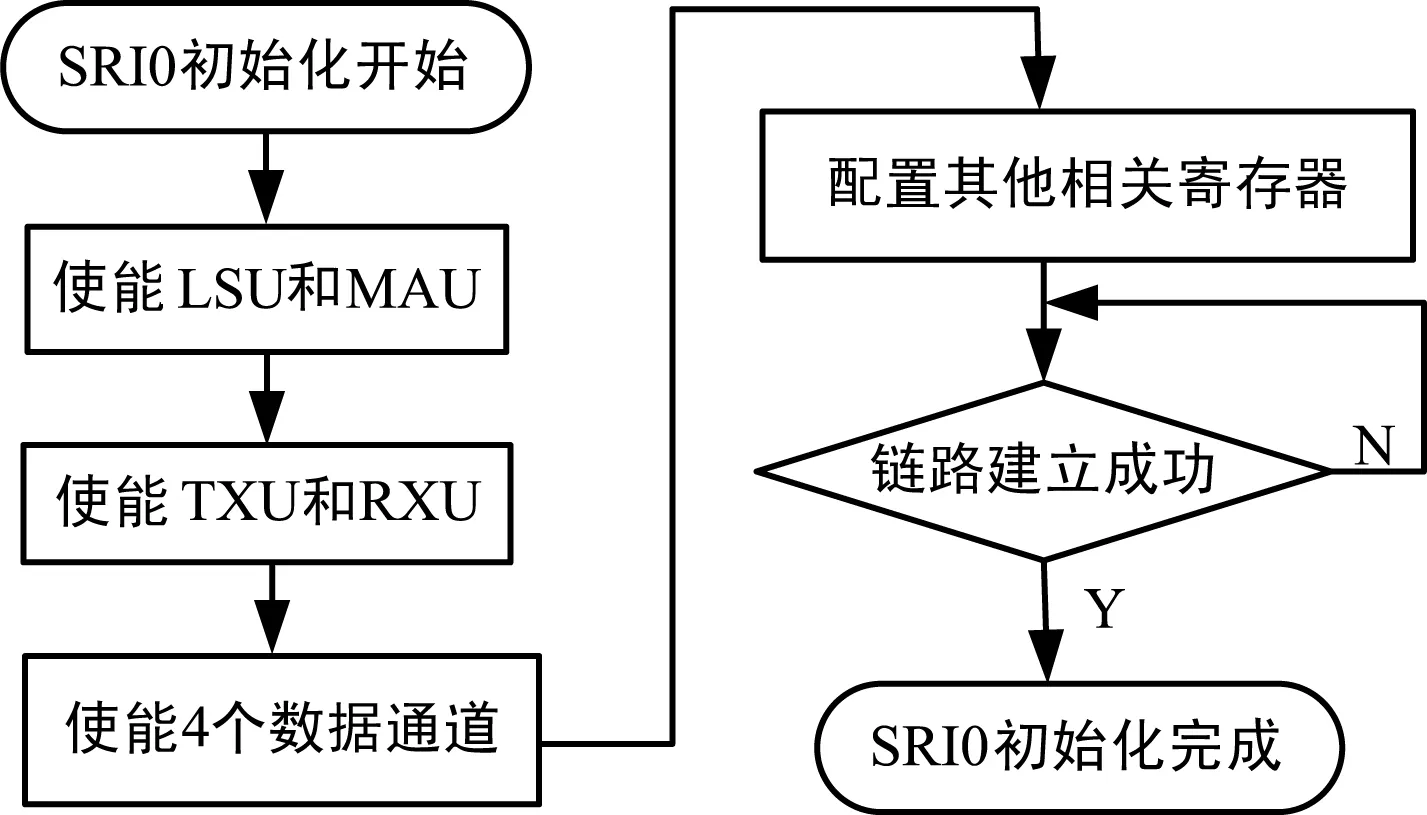

整体方案根据上述设计需求,在CCS(Code Composer Studio)开发平台上编写了一个相应的SRIO初始化函数,命名为SRIO_int,函数的处理流程如图2所示。

图2 SRIO初始化流程图

为了使SRIO快速进入工作状态,SRIO_int函数作为SRIO的硬件驱动函数,应将其放在DSP整体初始化函数init_6455中其他设备驱动函数之前。

3 数据传输的仿真与实现

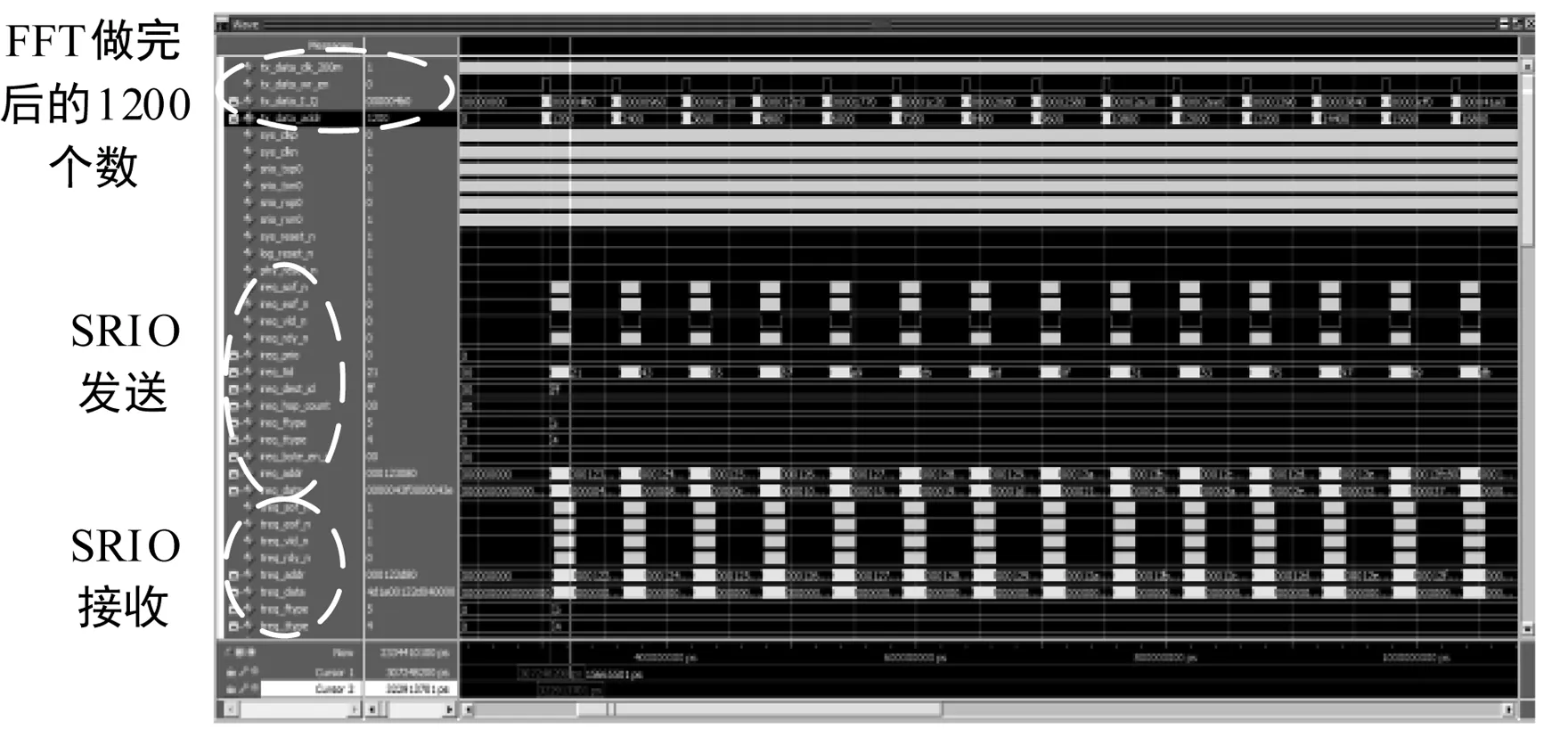

为了验证SRIO模块的逻辑功能的正确性,以及能够满足当前项目的需求,将其添加到下行接收工程中,并对整个工程进行了Modelsim仿真以及板级验证。如图3所示,图中SRIO发送的是FFT完成后的数据,由图可见SRIO被触发了14次(每个符号FFT后将去CP后的数据传送给DSP),这种触发方式大大提升了系统的实时性,降低了系统的处理时延。

图3 SRIO在下行接收工程中的仿真图

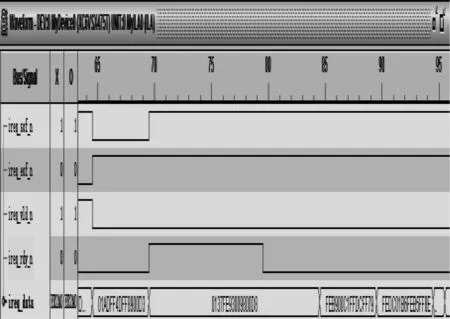

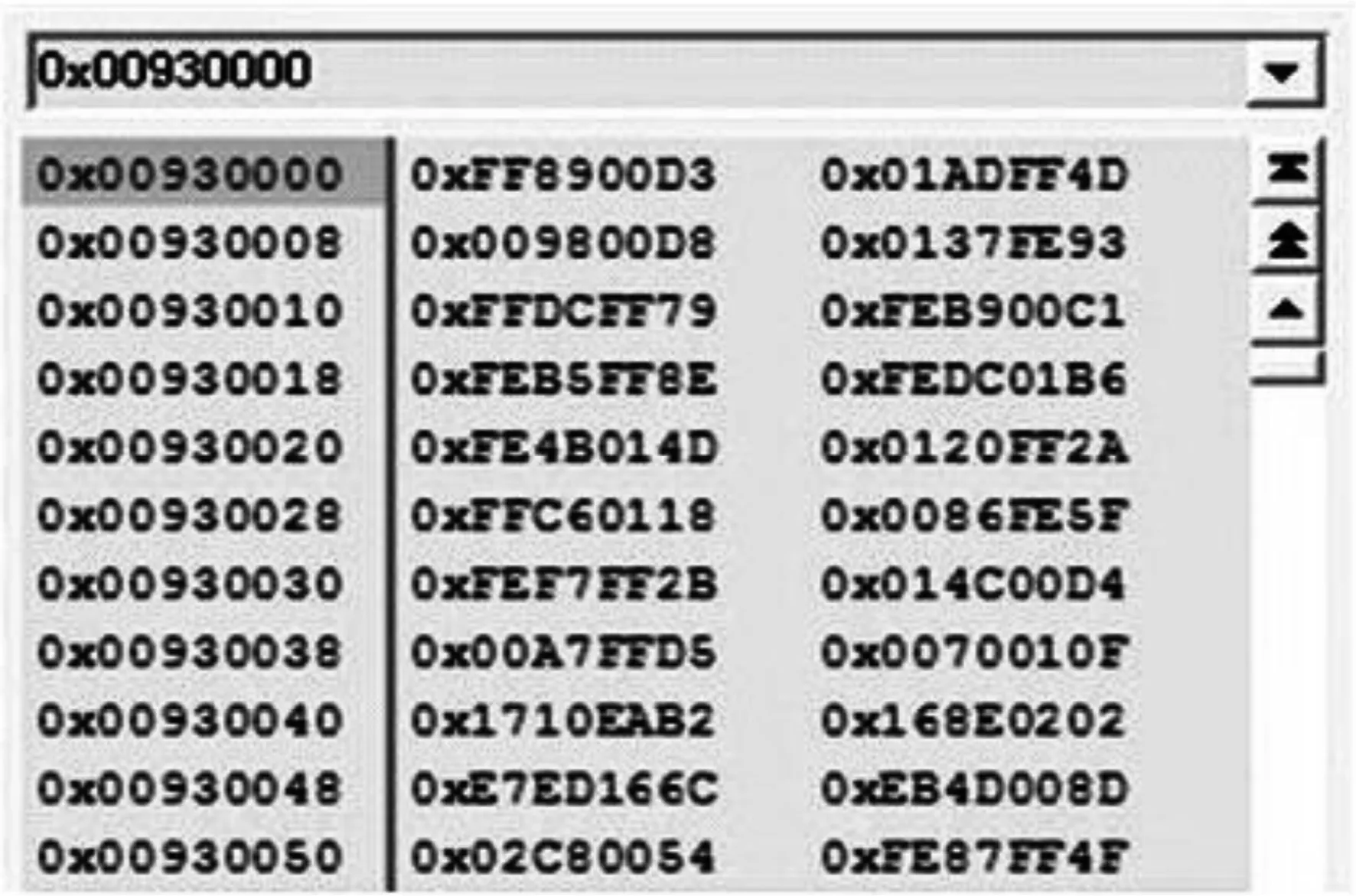

为了验证整个传输方案的正确性,FPGA通过SRIO传输经过信号检测后一个子帧完整的数据给DSP,DSP将接收到的数据与FPGA发送的数据进行比对,与此同时,借助CCS3.3观察一子帧的数据以及该子帧的星座图,如图4与图5所示,该子帧的数据均被正确接收,无重复无遗漏;图5中的星座图符合正交相移键控(Quadrature Phase Shift Keying,QPSK)调制理论,证明整个传输方案的正确性与可行性。

图4 SRIO发送信号检测后的数据

图5 DSP接收到信号检测后的数据

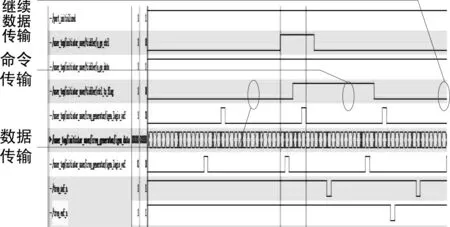

方案利用Chipscope对前文所设计的信令与数据的传输方案进行了验证,结果如图6所示。由图可知信令的传输没有影响数据正常发送,也没有一帧数据的丢失或重复发送。到此,SRIO的主要设计方案均得以验证。

图6 命令与数据优先级验证图

4 结束语

全文对高速SRIO接口的技术特点做了简单介绍,而后在Xilinx公司提供的相关IP核基础上,根据实际工程需要对IP核逻辑层进行了改进与完善,与此同时保留IP核原有的缓冲核与物理层核。最后使用相关软件对整个设计进行了仿真测试与硬件的实现,验证了DSP芯片与FPGA芯片间数据交互的可行性与正确性,并将其应用于TD-LTE-A射频一致性测试仪系统开发中。通过相关工程验证,其工作可靠,满足了实际工程中对数据传输的性能要求。

[1] 沈 嘉,索士强,全海洋,等.3GPP长期演进(LTE)技术原理与系统设计[M].北京: 人民邮电出版社,2008: 220-221.

[2] 徐贵州,李跃进.TMS320C6455高速串行接口SRIO应用研究[J].通信与广播电视,2015 (2):1-9.

[3] Akiyama Y,Sakuta M,Nishino Y,et al.Performance Evaluation of SRIO Which Comply to the Number of Active Connections in DiffServ Network for the Assured Forwarding Service[J].Technical Report of Ieice Cq,2001,101(444):95-101.

[4] 许树军,黄 镠,牛戴楠,等.基于FPGA的Serial RapidIO协议的设计与实现[J].雷达与对抗,2015 (4):36-38.

[5] Jeon J,Kim D,Lee D.IEEE1588-based Clock Synchronization for Embedded Networked System with SRIO[C]∥ International Conference on ICT Convergence.Jeju: IEEE Press,2013: 843-845.

[6] 杨 婧.12.5Gb/s时钟数据恢复电路设计及6.25Gb/s SerDes接收芯片集成[D].南京:东南大学,2012.

[7] 秦 蒙,王 辉,秋云海,等.光纤通信中8B/10B编码器的设计与实现[J].电视技术,2014,38(1): 50-54.

[8] 宁赛男.RapidIO协议在图像处理系统中的应用研究[D].合肥: 中国科学技术大学,2013.

[9] Liu J,Tian Y,Hao W,et al.Design and Implementation of Serial Rapidio Based on DSP and FPGA[C]∥ 2014 International Conference on Mechatronics and Intelligent Materials(MIM).Switzerland: Trans Tech Publication Ltd,2014: 1581-1585.

[10]张守将.基于ROCKET I/O的高速数据传输系统研究[D].西安: 西安电子科技大学,2013.

[11]潘国祯.基于FPGA实现的高速串口传输技术与实现[D].上海: 复旦大学,2009.

[12]Kwak K,Kwon O.Power-Reduction Technique Using a Single Edge-tracking Clock for Multiphase Clock and Data Recovery Circuits[J].IEEE Transaction on Circuits and Systems II: Express Briefs,2014,61(4): 239-243.

Interface Design of LTE-A Baseband System Based on SRIO

ZHANG De-min,ZHANG Wei,XUE Yao

(College of Electronic Engineering,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

The traditional EMIF parallel interface in the TD-LTE-A wire-less comprehensive test instrument has been unable to meet the needs of the large number of data exchange between the chips.In view of this problem,a design scheme of serial high-speed embedded technology SRIO is proposed.The scheme realizes the interconnection between the DSP chip and the FPGA chip in the baseband system and is simulated with actually verified on the PCB board.The results show this scheme is correct and feasible,the average transmission rate of the SRIO is 2.09 Gb/s and can meet a large number of data interaction between the chips.

LTE-A;SRIO;FPGA;DSP

10.3969/j.issn.1003-3114.2017.02.21

张德民,张 巍,薛 尧.基于SRIO的LTE-A基带系统接口设计[J].无线电通信技术,2017,43(2):83-86.

2016-11-15

重庆市教委科学技术研究项目(KJ1500428)

张德民(1955—),男,教授,博士生导师,主要研究方向: 数字信号处理在通信中的应用。张 巍 (1987—),男,硕士研究生,主要研究方向:TD-LTE-A基带系统接口开发。

TN492

A

1003-3114(2017)02-83-4