支持向量机(SVM)算法用于计算机CPU功耗管理

2017-03-01周平强

廖 凯,周平强

(1.中国科学院上海微系统与信息技术研究所 上海200050;2.上海科技大学 上海 201210;3.中国科学院大学 北京100049)

支持向量机(SVM)算法用于计算机CPU功耗管理

廖 凯1,2,3,周平强1,2,3

(1.中国科学院上海微系统与信息技术研究所 上海200050;2.上海科技大学 上海 201210;3.中国科学院大学 北京100049)

基于减少CPU功耗的目的,采用了机器学习SVM算法为CPU的动态频率电压调节技术(DVFS)制定决策模型,采用EDP(Energy Delay Product)作为最终优化指标。通过GEM5和McPAT工具进行仿真实验,发现新建的模型按照执行程序不同最多可以节省20%的EDP。

DVFS;SVM;EDP;功耗管理;预测优化

随着集成电路的发展,现代CPU芯片集成度越来越高,性能飞速发展,伴随而来的是居高不下的功耗和散热成本,单位面积的功耗太高已成为了CPU性能突破的瓶颈。如何降低CPU芯片的功耗,成为了当前研究的重点。

1 CPU的低功耗技术——DVFS简介

CPU低功耗技术很多,譬如时钟门控技术(Clock gating),电源门控技术(Power gating)和动态电压频率调节技术(DVFS)等。其中Clock gating技术通过在电路中增加额外的逻辑单元、优化时钟树结构来节省能量[1]。Power gating技术通过关掉当前电路中空闲的模块,从而节省能量[2]。DVFS技术通过动态调节当前芯片的电压和频率来节省能量。这3种方法在CPU中都有广泛的应用。文中针对DVFS技术,研究如何优化DVFS技术的执行策略。

1.1 DVFS与功耗

在芯片设计中,功耗一直是备受关注的优化目标之一。处理器的功耗计算有如下关系式,

其中,α是活动因子 (Activity Factor),C是电路中所有晶体管的等效电容,f是电路运行频率,Vdd是电路的供电电压,I是静态电流。处理器的功耗P分别与频率f和电压Vdd的二次方成正比,而处理器运行频率f越高,需要提供的电压Vdd也越高,两者可以看成是正比关系。通过降低处理器的运行频率f和电压Vdd,处理器的总功耗将以三次方的同比速度降低。DVFS技术就是通过调节处理器的频率f和供电电压Vdd从而达到节省功耗的目的。

1.2 DVFS策略

DVFS技术的合理应用能显著减少CPU的整体功耗。但是,降低处理器频率和电压势必会降低处理器的运算性能,导致运算时间变长。能耗是功耗与时间的乘积,不合理的DVFS有时候可能导致更多的能耗。所以,如何合理运用DVFS技术,准确预测CPU下阶段应选择的电压和频率成为了问题的关键。

2 研究方法(Methodology)

DVFS是在CPU任务较少的时候 (此时可能的状况是Cache miss较多,访存时间长,CPU处于等待时间)降低其运行频率和电压从而达到降低能耗的目的。这需要CPU内部的参量数据来建模量化DVFS策略标准。

2.1 相关研究

南加州大学的Kihwan Choi教授等人提出将CPU的工作任务分为 onchip和 offchip两部分,onchip工作量表示完成当前工作所需的CPU工作时钟周期数,offchip工作量表示外部内存操作所需的时钟周期。通过比较两部分工作量的比例从而制定DVFS策略[3]。三星电子公司的Sungpack Hong等人通过准确预测CPU工作量,结合给定的deadline constraint时间,调节处理器运行频率和电压[4]。另外一种比较有意思的做法是IBM公司Waston研究中心的Canturk Isci等人通过应用Phase[5-7]的概念,将程序按照其特征分为多个Phase,给每个Phase选择最佳的运行频率和电压,通过预测下个Phase来判断CPU下阶段的频率和电压[8]。美国威斯康星(Wisconsin)大学的Aman Rakesh Chadha等人将机器学习SVM算法应用到CPU的动态功耗管理中,通过训练得到模型对CPU频率选取进行决策,并探索了能量和时间的转换关系[9]。

2.2 SVM算法构建决策模型

文中研究采用了和文献[9]相似的方法。运用了GEM5[10-11]和McPAT[12-13]的组合来得到CPU内部参量和功耗数据,利用机器学习SVM算法构建决策模型。

如图1所示,整个流程可以分为训练阶段和测试运行阶段两部分。

图1 流程图

在训练阶段,首先要得到用于训练的数据。我们将要仿真的程序按固定指令数平均划分为n段,对每个程序段,利用GEM5和McPAT工具可以得到一组形如<Parameter vector,F,EDP>形式的数据,称为一个“Set”。其中Parameter vector是由几个CPU参量组成的向量,例如 IPC,Cache miss数,Memory Access数等,F为CPU频率,EDP为此程序段执行消耗的能量和延迟的内积。以不同频率执行此相同程序段,得到多组这样的Set。在处理环节中,选择出拥有最低EDP的一组Set,我们认为它所对应的执行频率F是此程序段的最佳运行频率,将其作为一个“Sample”(样本)。运行不同程序段,得到更多的样本,组成我们用于训练的数据集合。

我们将样本数据按频率分类,F作为类的标志。我们的目的是,给定一组Parameter vector,我们要能准确判断其适合的频率。这需要首先构建分类模型来进行判定。我们引用了机器学习领域的SVM算法来解决这个问题。

训练阶段得到模型后,在测试运行阶段,我们修改了GEM5代码,将训练阶段得到的模型集成到GEM5中,此模型从CPU获取数据,输出选择结果来控制DVFS模块。DVFS模块执行Model的选择结果改变CPU电压和频率(V/F)进行下个周期的运行。

相比文献[9],我们做了很多改进:

1)程序段划分标准。文献[9]中GEM5执行仿真时,将程序以固定cycle数来划分程序段。但是,当CPU以不同频率如1 GHz和2 GHz分别执行时,需要的总cycle数会不一致。文中采用按固定指令数的方法来划分程序段。

2)静态功耗。随着静态功耗在CPU总功耗中占的比重越来越大,静态功耗已经不能忽视。文献[9]中只考虑了CPU的动态功耗,本研究中综合考虑了静态功耗和动态功耗。

3)优化目标。文献[9]中探索了应用DVFS后,能量和时间的权衡关系。文中采用了能量和时间的内积(EDP)作为最终优化目标。

4)搭建了通用平台。通过修改GEM5源代码,将LIBSVM[14]提供的库函数利用python接口集成到了GEM5中。训练时,每次得到的DVFS决策模型将被保存为一个单独的文件,并可直接通过文件调用,这样构建了一个实验平台。若要更换决策模型,可直接通过平台调用新的决策模型进行DVFS仿真实验。

3 实 验

实验按照GEM5默认的参数配置,在GEM5的SE模式下仿真,并选择SPEC CPU2006[15-17]作为仿真程序(benchmark)。

我们将仿真程序按照每一千万个指令分段,运行可得到每段的输出数据。图2中描绘了bzip2程序前29个程序段L2 Cache miss数,IPC和仿真时间这3个参量的变化趋势。由图中可以看出,不同的程序段的各参量变化趋势明显,且存在一定关联,如L2 Cache miss数和仿真时间成正相关,与IPC成负相关。

图2 bzip2程序段参量变化趋势图

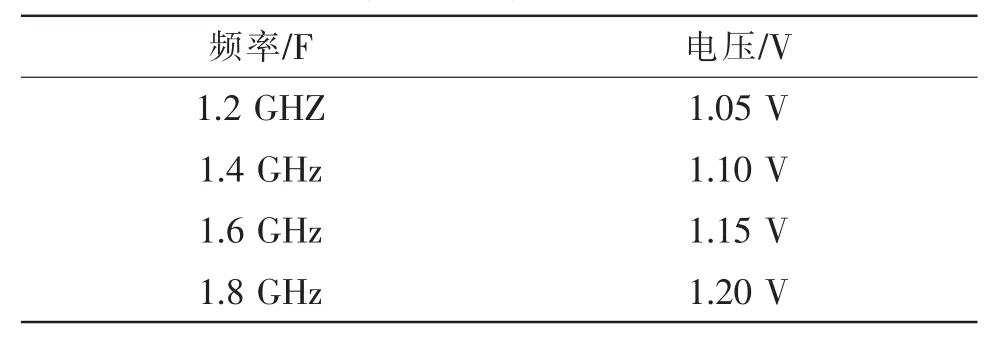

我们选择了Cache miss的数据和IPC等指标共同组成了Parameter vector。采用了如表1所示的电压频率对应关系来实验构建DVFS策略。

首先,我们考虑比较简单的情况,即CPU只有两种运行频率,分别为1.2 GHz和1.8 GHz,对应的电压分别为1.05 V和1.20 V(表1)。

表1 频率和电压

两频率的DVFS实验结果见图3。图3中列举了SPEC CPU 2006中的gcc(compute bound)和mcf(memory bound)两个程序的实验结果。图中,横坐标表示程序执行的频率,纵坐标表示程序消耗的EDP。从图中可以发现,采用DVFS动态调节频率所消耗的EDP是最低的。相比于采用单一频率,DVFS最多分别可节省16.26%和8.87%的EDP。另外,从图中可以看出,采用DVFS运行gcc时,选用1.8 GHz的时间会远远多于选择1.2 GHz,mcf程序相反。这是因为gcc是计算需求比较多的程序,发生Cache miss次数很少,需要以较高频率运行。mcf程序访问内存比较多,大部分时间CPU处在等待状态,所以选择较低频率运行来节省EDP。

图3 两频率DVFS(gcc,mcf)实验结果

表2列举了其他几个仿真程序的实验结果。其中,第二列预测准确度表示构建的DVFS决策模型对下阶段F/V选择的预测准确度,基本都在95%以上。当预测结果不准确时,会出现本应选择1.2 GHz(1.8 GHz)的执行频率却选择了1.8 GHz(1.2 GHz)的情况,导致EDP的浪费。

相比两频率DVFS,四频率DVFS(表3)多出了1.4 GHz和1.6 GHz两种频率选择,意味着更精细的调控。所以整体而言,四频率DVFS节省的EDP比两频率的高。但是,由于四频率增加了分类的难度,所以其预测准确度有所降低。

表2 两频率DVFS实验结果

表3 四频率DVFS实验结果

4 结束语

文中采用机器学习领域的支持向量机算法(SVM)来构建动态频率电压(DVFS)决策模型,在节省能耗的过程中兼顾处理器性能,采用能量和延迟的内积(EDP)作为最终优化目标,实验证明,SVM算法优化得到的模型对不同程序最多可以节省将近20%的EDP。

[1]Wu Q,Pedram M,Wu X.Clock-gating and its application to low power design of sequential circuits[J].Circuits and Systems I:Fundamental Theory and Applications,IEEE Transactions on,2000,47(3):415-420.

[2]Chiou D S,Chen S H,Chang S C,et al.Timing driven power gating[C]//Proceedings of the 43rd annual design automation conference.ACM,2006: 121-124.

[3]Choi K,Soma R,Pedram M.Dynamic voltage and frequency scaling based on workload decomposition [C]//Proceedings of the 2004 international symposium on Low power electronics and design. ACM,2004:174-179.

[4]Hong S,Yoo S,Jin H,et al.Runtime distributionaware dynamic voltage scaling[C]//Proceedings of the 2006 IEEE/ACM international conference on Computer-aided design.ACM,2006:587-594.

[5]Sherwood T,Perelman E,Hamerly G,et al. Discovering and exploiting program phases[J]. Micro,IEEE,2003,23(6):84-93.

[6]Sherwood T,Sair S,Calder B.Phase tracking and prediction[C]//ACM SIGARCH Computer Architecture News.ACM,2003,31(2):336-349.

[7]Lau J,Schoenmackers S,Calder B.Transition phase classification and prediction[C]//High-Performance Computer Architecture,2005.HPCA-11.11th International Symposium on.IEEE,2005: 278-289.

[8]Isci C,Buyuktosunoglu A,Martonosi M.Longterm workload phases:Duration predictions and applications to DVFS[J].Micro,IEEE,2005,25(5):39-51.

[9]Chadha A R,Pandey A,Prakash A.ECE 752-AdvancedComputerArchitectureI[J].Dynamic Power Management using Machine Learning,2003:1-16.

[10]Binkert N,Beckmann B,Black G,et al.The gem5 simulator[J].ACM SIGARCH Computer Architecture News,2011,39(2):1-7.

[11]Spiliopoulos V,Bagdia A,Hansson A,et al.Introducing DVFS-management in a full-system simulator[C]//Modeling,Analysis&Simulation of Computer and Telecommunication Systems(MASCOTS),2013 IEEE 21stInternationalSymposium on. IEEE,2013:535-545.

[12]Li S,Ahn J H,Strong R D,et al.McPAT:an integrated power,area,and timing modeling framework for multicore and manycore architectures[C]//Microarchitecture,2009.MICRO-42.42nd Annual IEEE/ACM International Symposium on.IEEE,2009:469-480.

[13]Li S,Ahn J H,Strong R D,et al.The McPAT framework for multicore and manycore architectures:Simultaneously modeling power,area,and timing[J].ACM Transactions on Architecture and Code Optimization(TACO),2013,10(1):5.

[14]Chang C C,Lin C J.LIBSVM:A library for support vector machines[J].ACM Transactions on IntelligentSystemsandTechnology(TIST),2011,2(3):27.

[15]Henning J L.SPEC CPU2006 benchmark descriptions[J].ACM SIGARCH Computer Architecture News,2006,34(4):1-17.

[16]王友春,文闪闪,秦跃进,等.基于ARIMA-SVM模型的微电网短期负荷组合预测研究 [J].陕西电力,2014(3):19-23.

[17]吕意飞,郝立泉,任忠远,等.混沌最小二乘支持向量机的短期风功率预测[J].工业仪表与自动化装置,2015(3):76-78.

Power management in CPU based on SVM algorithm

LIAO Kai1,2,3,ZHOU Ping-qiang1,2,3

(1.Shanghai Institute of Microsystem and Information Technology,Chinese Academy of Sciences,Shanghai 200050,China;2.School of Information Science and Technology,Shanghai Tech.University,Shanghai 201210,China;3.University of Chinese Academy of Sciences,Beijing 100049,China)

Power management of processor is always an important research field.In this paper,we take advantage of Support Vector Machine (SVM)Algorithm in Machine Learning to train and get the decision model for Dynamic Voltage and Frequency Scaling(DVFS)technology.We set the Energy Delay Product (EDP)as our optimization goal,to get a better trade-off between energy and performance. Experiment result shows that it can reduce as much as 20%EDP with different applications.

DVFS;SVM;EDP;power management;prediction and optimization

TN409

:A

:1674-6236(2017)02-0055-04

2015-12-28稿件编号:201512284

廖凯(1990—),男,湖南邵阳人,硕士研究生。研究方向:计算机体系结构(CA),计算机辅助设计(CAD)。