一种基于FPGA的微处理器软错误敏感性分析方法

2017-02-06梁华国孙红云孙骏黄正峰徐秀敏易茂祥欧阳一鸣鲁迎春闫爱斌

梁华国孙红云孙骏黄正峰徐秀敏易茂祥欧阳一鸣鲁迎春闫爱斌

一种基于FPGA的微处理器软错误敏感性分析方法

梁华国①孙红云①孙 骏①黄正峰*①徐秀敏①易茂祥①欧阳一鸣②鲁迎春①闫爱斌②

①(合肥工业大学电子科学与应用物理学院 合肥 230009);②(合肥工业大学计算机与信息学院 合肥 230009)

为了自动快速地分析微处理器对软错误的敏感性,该文提出一种基于FPGA故障注入的软错误敏感性分析方法。在FPGA芯片上同时运行有故障和无故障的两个微处理器,并充分利用FPGA的并行性,把故障注入控制、故障分类、故障列表等模块均在硬件上实现,自动快速地完成全部存储位的故障注入。以PIC16F54微处理器为实验对象,基于不同负载分别注入约30万个软错误用以分析微处理器软错误敏感性,并对敏感性较高的单元加固后再次进行分析,验证该方法的有效性。实验数据表明,使用该方法进行故障注入及敏感性分析所需的时间比软件仿真方法提高了4个数量级。

FPGA;故障注入;单粒子翻转;软错误;敏感性分析

1 引言

随着集成电路特征尺寸的缩小、供电电压的降低以及时钟频率的提高,使得微处理器对串扰、电压扰动、辐射等因素变得更加敏感。尤其在航空航天等特殊应用领域,高能粒子辐照作用引起的单粒子效应,严重影响微处理器的可靠性。研究结果显示,计算机系统中80%~90%的失效都是由于瞬态故障引起的[1]。因此,为提高集成电路的可靠性,需要对瞬态故障导致的软错误进行敏感性分析,分析结果可作为选择性加固的依据。

故障注入作为一种灵活方便、便宜有效的方法广泛应用于可靠性评估领域[2]。常用的故障注入方法有物理故障注入、仿真故障注入和现场可编程门阵列(Field-Programmable Gate Array, FPGA)故障注入。文献[3,4]中使用重离子辐射及引脚级注入的物理方法引入故障,此方法的优点是实验结果与实际结果最为接近,但需要昂贵的实验设备和已制造出的电路原型。文献[5-9]中使用软件仿真的方法实现故障注入,该方法虽然具有很好的观察性和可控性,但是时间开销较大,难以进行大量的故障注入。

近几年,受到研究人员关注的是基于FPGA的故障注入,它既具有物理故障注入的快速性,又具有仿真故障注入的可控性,可通过重配置或修改源代码实现。文献[10,11]利用重配置方式实现故障注入,但该方式每进行一次故障注入需要重新配置FPGA,时间开销较大。文献[12-15]中使用修改源代码的方式实现故障注入,其故障注入平台是由硬件和软件两个部分组成。每次故障注入都需等待主机传送控制命令到FPGA开发板,主机与FPGA之间频繁的数据通信严重阻碍实验的速度。

基于以上分析,本文提出一种基于FPGA故障注入的软错误敏感性分析方法,把故障列表、故障注入控制、故障分类等模块全部放到FPGA硬件上实现,减少主机与FPGA之间的通信,保证该方法的快速性。该方法使用状态机自动地完成所有触发器的故障注入,使用超级终端一次性显示所有的故障分类结果。利用该方法对PIC微处理器注入大约30万个软错误,来分析微处理器的软错误敏感性,并对敏感性较高的寄存器进行三模冗余加固后再次进行分析,验证该方法的有效性。

2 相关介绍

2.1故障注入点及故障注入控制电路

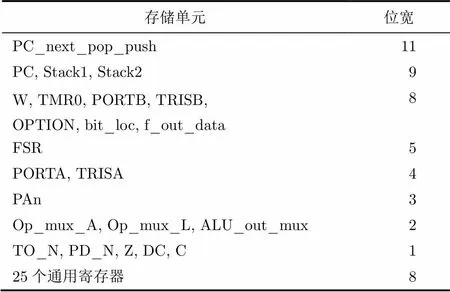

任何软错误不管产生于组合逻辑还是时序逻辑,如果要产生显式的处理器运行失效,都必须通过触发器传递错误状态,因此对所有触发器进行故障注入就可模拟大多数的软错误。本文研究对象为PIC16F54微处理器,具有两级的堆栈深度,7个特殊功能寄存器,25个通用寄存器,1个工作寄存器,1个PC指针,3个不可寻址寄存器。对这些寄存器以及设计PIC微处理器过程中的一些控制信号全部进行故障注入(共48个存储单元,即321位),所有的存储单元以及每个存储单元的位宽如表1所示。

表1 PIC包含的存储单元

本文选择对软错误而言最常用的位翻转作为故障模型。使用源代码修改技术,对微处理器中的所有触发器进行修改,使其具有单粒子翻转(Single Event Upset, SEU)故障注入控制功能,修改后的控制电路如图1所示。FIS(Fault Injection Set)为故障注入设置位,当FIS值为低电平时,正常的输入值传递到触发器输出端;当FIS值为高电平时,输入的相反值传递到触发器的输出端,即一个故障注入到相应位置。把这种故障注入控制电路添加到每一个触发器,通过控制FIS值来决定是否对该触发器进行故障注入。

图1 故障注入控制电路

2.2故障注入结果分类

软错误在处理器中的表现形式是不一样的,一些软错误不产生任何作用,而另一些则产生功能性错误。为分析不同存储单元的软错误敏感性,我们将处理器注入软错误后的运行结果分为以下3类:

显式失效:故障处理器和无故障处理器的输出结果不一致,即产生了显式的错误。

隐式失效:故障和无故障处理器的输出结果一致,但存储单元的状态不完全一致,把运行结果归为隐式失效。虽然该故障目前没有表现出来,但改变了处理器的状态,例如通用寄存器的数据,则在用到该寄存器的时候就可能使系统产生显式失效。

完全匹配:故障处理器和无故障处理器不仅输出结果一致,而且存储单元的状态也完全一致,该类软错误被完全屏蔽,不影响微处理器的功能。

3 故障注入与分析平台

3.1平台框图

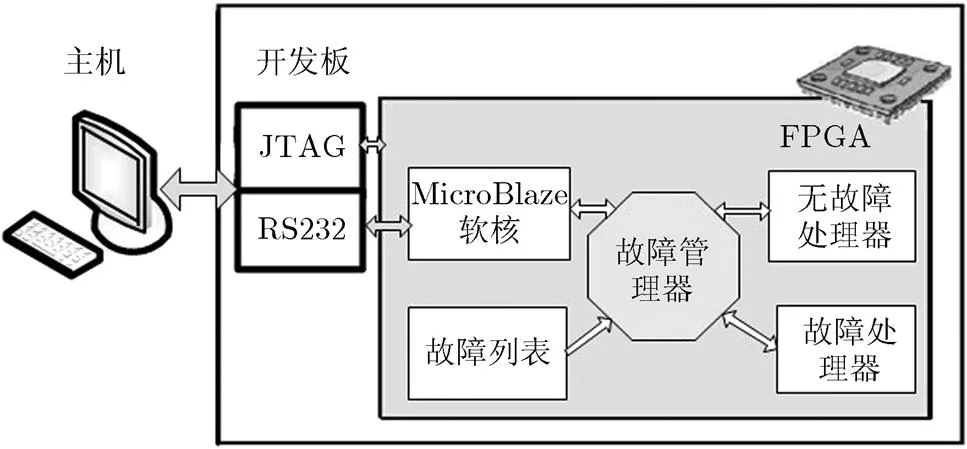

构造实用的故障注入平台是将故障注入方法应用到实际实验中的重要步骤,图2为所构造的故障注入及分析平台结构示意图。在FPGA芯片上,运行两个微处理器,一个是无故障处理器,其运行结果作为对故障注入结果分类时的参考状态。另一个是故障处理器,用于执行具有故障注入机制的处理器,它们两个在故障管理器的控制下运行。一旦故障管理器启动之后,该平台自动对故障处理器的存储位进行故障注入,在运行一定周期之后,把故障处理器与无故障处理器进行输出端口及存储单元状态的比较,并把所有比较分类结果保存在FPGA的寄存器中。待所有存储位的故障注入完成之后,在Microblaze软核的控制下,通过接口电路把结果信息一次性显示到主机的超级终端上,完成一轮完整的故障注入。其中的故障列表是一片位宽为10、深度为321的单端口块ROM,在故障管理器的控制下对其解码并设置FIS值。

图2 基于FPGA的故障注入与分析平台

3.2故障管理器

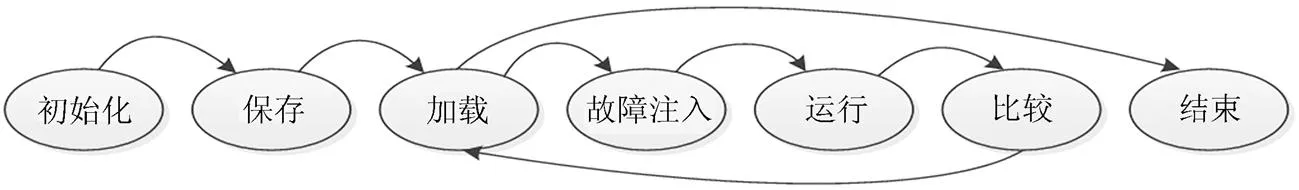

该平台中故障管理器起着重要作用,控制着故障注入、数据收集、状态比较等过程。故障管理器的控制过程使用一个含有7个状态的状态机实现,状态转移如图3所示,各个状态所执行的操作如下:

(1)初始化状态:当Microblaze接收到主机发送的开始故障注入命令之后,启动状态机,进入初始化状态,完成相应寄存器的清零或置数操作。

(2)保存状态:当初始化完成后进入到保存状态,把保存标志寄存器置1,以便无故障及故障处理器把该故障注入时刻的所有寄存器值保存起来。

(3)加载状态:当保存状态或比较状态完成后,自动进入到加载状态,即把加载标志寄存器置1,以便故障处理器及无故障处理器把在故障注入时刻的寄存器值重新加载到寄存器中。另外还需检测是否到故障注入的最后一位,以便进入到结束状态。

(4)故障注入状态:该状态控制故障处理器按照所采用的故障模型在相应的存储位进行故障注入,即设置FIS值,激活故障注入控制电路。

(5)运行状态:故障注入完成以后进入到运行状态,如果到达所需比较的时间,则进入到比较状态。

(6)比较分类状态:把故障处理器与无故障处理器的运行输出结果及所有的寄存器进行比较,并把分类结果保存起来。由于平台实现的是自动对所有存储位进行故障注入,所以在此状态还需进行故障列表地址加1的操作,以便对下一位进行故障注入。

(7)结束状态:所有的存储位注入完成后,状态机进入到结束状态。把结束标志位置1,以便主机查询注入是否结束,通过控制命令把所有的故障数及分类结果一次性传到超级终端以便用户观察。

4 实验结果

4.1实验环境及步骤

基于自动快速故障注入的考虑,该故障注入平台在FPGA硬件上实现,所使用的FPGA芯片为Xilinx公司Spartan-6系列的xc6slx16。主机为I3处理器,频率3.4 GHz。软件为ISE 13.2,用该软件对故障及无故障PIC16F54微处理器、故障管理器以及故障列表进行RTL建模。用Microchip公司的MAPLAB设计负载程序,编译生成16进制文件。用MathWorks公司的MATLAB将16进制文件生成ISE能够识别.v文件作为微处理器的运行负载。最后使用ISE综合工具及实现工具编译之后,将生成的二进制配置文件通过JTAG接口下载到FPGA开发板上。MicroBlaze软核负责主机与FPGA芯片之间的通信,通过RS232接口一方面接收主机发送的故障管理器启动命令,另一方面把故障管理器获得的分析结果传送到主机的超级终端上进行显示。

图3 状态转移图

4.2敏感性分析及敏感单元加固

根据存储单元所在位置不同,把故障注入分为5个模块,试验首先进行的是按不同模块进行故障注入。对特定负载下的PIC处理器注入约30万个软错误,得出不同模块的软错误敏感性即(/)×100%,为对该模块进行故障注入的总数,为故障运行结果为显式失效的个数。表2给出了故障注入模块、该模块包含的触发器个数以及该模块的敏感性。从表2中可以看出,系统失效较高的敏感模块为取指令模块以及特殊功能寄存器模块。该平台也可获得每一个存储单元的软错误敏感性,不同负载下处理器的敏感单元略有不同。第1个负载为使用TMR0定时器的计数器,在此负载下注入约30万个软错误,敏感性结果如图4所示,该图的横坐标为存储单元名称,纵坐标为该存储单元的故障注入结果。单元名称依次为Stack1, Stack2, PC_next_pop, Op_Mux_A, Op_Mux_L, ALU_out_Mux, bit_loc, TRISA, TRISB, OPTION,PC, W, f_out_data, PORTB, PORTA, FSR, TMR0, Pan, TO_N, PD_N, Z, DC, C, dataram,图中横坐标只是列出其中的几个。可看出,敏感单元包含TMR0, PC, W等,对没有使用到的Stack1, Stack2等单元故障注入结果是隐式失效。

表2不同模块的软错误敏感性

故障注入模块触发器个数模块敏感性(%) 取指令 2931.0 译码 14 8.4 通用寄存器200 3.2 特殊功能寄存器 5832.1 不可寻址寄存器 200

第2个负载是调用子函数的延时程序,该程序频繁使用Stack1, Stack2,在此负载下故障注入,敏感性结果如图5所示。可看出,敏感性较高的存储单元含Stack1, Stack2, PC, W等,而TMR0为隐式失效。从图4,图5中得出,微处理器在同一负载下,不同存储单元对软错误的敏感性是不一样的;不同负载下,同一存储单元的软错误敏感性也不一样,但除了与负载有关的特定存储单元外,其余的总体趋势基本一致;微处理器中的软错误敏感单元包括频繁使用的PC指针、工作寄存器(W)以及译码模块中的控制信号;对于没有使用到的存储单元,注入结果为隐式失效。这些结果都与理论分析相符,也与文献[3]中的结论一致,由此证明该平台的正确性。由于PORTA, PORTB在本实验中作为微处理器失效的输出,所以对其进行故障注入敏感性达到100%,实际情况下不会有这么高的敏感性。

使用文中的故障注入平台可以快速准确地分析出在定负载下的敏感单元,运行负载1的微处理器敏感性较高的存储单元包括TMR0, PC, W,寄存器输出文件(f_out_data)以及译码模块中的控制信号Op_Mux_A, Op_Mux_L, ALU_out_Mux, Z。对这些敏感性较高的存储单元以及PORTA, PORTB端口采取三模冗余方案进行加固,加固后再次使用该平台对其进行故障注入,所得结果如图6所示,可以看出三模冗余方案完全屏蔽SEU故障,同时进一步验证了该平台的正确性。在三模冗余加固方案下,仅仅通过加固20%的触发器,可以使微处理器对SEU故障的软错误敏感性降低到1%以下。

4.3速度比较

为了证明本文提出的基于FPGA故障注入与敏感性分析方法的快速性,使用Modelsim软件仿真的方法,同样采用RTL修改源代码技术对PIC微处理器再次进行故障注入及敏感性分析。表3中数据为微处理器在不同负载下,分别使用两种方法进行一次故障注入及敏感性分析所需的时间,单位为μs。最后一列数据表明,本文提供的FPGA方法比软件仿真的方法速度提升了4个数量级,从而使得在可以接受的时间范围内,为获得具有统计意义的结果而进行更多的故障注入成为可能。

表3 不同方法的时间开销

5 总结

本文基于FPGA的故障注入技术,提出一种自动快速并便于观察的敏感性分析方法。用该方法,对不同负载下的PIC16F54微处理器,分别注入大约30万个软错误,分析每个存储单元的敏感性。该方法在FPGA芯片上同时运行两个处理器RTL模型,方便实现故障结果的分类,降低了设计的复杂度;利用内部的故障管理器实现对故障注入过程的控制,自动完成所有触发器的故障注入;把故障分类、故障列表都放到FPGA上实现,减少实验过程中主机与FPGA之间通信时间,加快了敏感性分析的过程;使用超级终端一次性显示所有的故障注入结果,具有良好的观察性。

图4 负载1故障注入结果 图5 负载2故障注入结果 图6三模冗余加固后故障注入结果

[1] CLARK J and PRADHAN D. Fault injection: a method for validating computer-system dependability[J]., 1995, 28(6): 47-56. doi:10.1109/2.386985.

[2] 孙峻朝, 王建莹, 杨孝宗. 故障注入方法与工具的研究现状[J]. 宇航学报, 2001, 22(1): 99-104.

SUN Junzhao, WANG Jianying, and YANG Xiaozong. The present situation for research of fault injection methodology and tools[J]., 2001, 22(1): 99-104.

[3] KARLSSON J, FOLKESSON P, ARLAT J,.Application of three physical fault injection techniques to the experimental assessment of the MARS architecture[C]. Proceedings of 5th IFIP Working Conference on Dependable Computing for Critical Applications, Urbana-Champaign, IL, 1995, (10): 267-287.

[4] GAISLER J. A portable and fault-tolerant microprocessor based on the SPARC V8 architecture[C].International Conference on Dependable Systems and Networks, Washington, D.C., 2002: 409-415.

[5] 黄海林, 唐志敏, 许彤. 龙芯1号处理器的故障注入方法与软错误敏感性分析[J]. 计算机研究与发展, 2006, 43(10): 1820-1827.

HUANG Hailin, TANG Zhimin, and XU Tong. Fault injection and soft error sensitivity characterization for fault-tolerant Godson-1 processor[J]., 2006, 43(10): 1820-1827.

[6] 武振平, 付方发, 肖立伊. 基于VHDL故障注入的处理器敏感性分析[J]. 微电子学与计算机, 2012, 29(10): 51-55.

WU Zhenping, FU Fangfa, and XIAO Liyi. Sensitivity analysis for processor based on VHDL fault injection[J].&, 2012, 29(10): 51-55.

[7] 吴杰. 基于VHDL的故障注入工具的研究与实现[D]. [硕士论文], 哈尔滨工业大学, 2013.

WU Jie. Research and implementation of VHDL-based fault injection tool[D]. [MsSter. dissertation], Harbin Institute of Technology, 2013.

[8] ADMANE N and ROTAKE D. Fault tolerant system for FPGA using simulation based fault injection technique[C]. 2015 International Conference on Communications and Signal Processing, Melmaruvathur, 2015: 0855-0859.

[9] 薛茜男, 李振, 姜承翔, 等. 面向航空环境的多时钟单粒子翻转故障注入方法[J]. 电子与信息学报, 2014, 36(6): 1504-1508. doi: 10.3724/SP.J.1146.2013.01296

XUE Qiannan, LI Zhen, JIANG Chengxiang,. A single event upset fault injection method based on multi-clock for aviation environment[J].&, 2014, 36(6): 1504-1508. doi: 10.3724/ SP.J.1146.2013.01296

[10] SERRANO F, CLEMENTE J, and MECHA H. A methodology to emulate single event upsets in flip-flops using FPGAs through partial reconfiguration and instrumentation [J]., 2015, 62(4): 1617-1624. doi:10.1109/TNS.2015.2447391.

[11] SHOBANA M and SENTHIL S. Reconfigurable data processing using duplex fault tolerance system[C]. 2015 International Conference on Innovations in Information, Embedded and Communication Systems, Coimbatore, 2015: 1-5. doi: 10.1109/ICIIECS.2015.7192935.

[12] EBRAHIMI M, MOHAMMADI A, EJLALI A,.A fast, flexible, and easy-to-develop FPGA-based fault injection technique[J]., 2014, 54(5): 1000-1008. doi:10.1109/DATE.2012.6176538.

[13] MOHAMMADI A, EBRAHIMI M, EJLALI A,. SCFIT: A FPGA-based fault injection technique for SEU fault model[C]. Design, Automation & Test in Europe Conference & Exhibition, Dresden, 2012: 586-589. doi: 10.1109/DATE.2012.6176538.

[14] CIVERA P, MACCHIARULO L, REBAUDENGO M,.FPGA-based fault injection techniques for fast evaluation of fault tolerance in VLSI circuits[C]. Field-Programmable Logic and Applications, Berlin Heidelberg, 2001: 493-502.

[15] SHOKROLAH-SHIRAZI M and MIREMADI S. FPGA- based fault injection into synthesizable verilog HDL models [C]. Secure System Integration and Reliability Improvement, Yokohama, 2008: 143-149.

梁华国: 男,1959年生,教授,研究方向为嵌入式系统综合与测试、数字系统设计自动化.

孙红云: 女,1991年生,硕士,研究方向为基于FPGA的故障注入、软错误敏感性分析.

孙 骏: 男,1991年生,硕士,研究方向为软错误敏感性分析.

黄正峰: 男,1978年生,副教授,研究方向为数字集成电路的硬件容错、星载SoC芯片的抗辐射加固.

徐秀敏: 男,1989年生,博士,研究方向为超大规模集成电路(VLSI)设计与测试、软错误敏感性分析.

易茂祥: 男,1964年生,教授,研究方向为超大规模集成电路(VLSI)设计与测试.

欧阳一鸣:男,1963年生,教授,研究方向为片上网络(NoC)与片上系统(SoC)、数据挖掘与信息系统.

鲁迎春: 男,1979年生,博士,研究方向为嵌入式系统综合与测试、数字系统设计自动化.

闫爱斌: 男,1983年生,博士,研究方向为软错误敏感性分析.

FPGA-based Soft Error Sensitivity Analysis Method for Microprocessor

LIANG Huaguo①SUN Hongyun①SUN Jun①HUANG Zhengfeng①XU Xiumin①YI Maoxiang①OUYANG Yiming②LU Yingchun①YAN Aibin②

①(&,,230009,);②(&,,230009,)

In order to quickly and automatically analyze the soft error sensitivity for microprocessors, a soft error sensitivity analysis method using FPGA-based fault injection is proposed. The fault and fault-free microprocessors on a FPGA are board run simultaneously. Moreover, a fault injection controller, a fault classification module and a fault list module are also implemented on the hardware. The method inherits the parallelism of the FPGA and achieves a fast and automatical fault injection for all storage bits. Further, using a PIC16F54 microprocessor as experimental subject, approximate 300, 000 soft errors are injected into the microprocessors to analyze its softerror sensitivity. In order to demonstrate the sensitivity evaluation efficiency of the method, the quite sensitive storage cells are hardened and the sensitivity is analyzed again. Compared to the simulation approach, experimental results show that the proposed technique achieves four orders of magnitude speedup.

FPGA; Fault injection; Single event upset; Soft error; Sensitivity analysis

TP302.8

A

1009-5896(2017)01-0245-05

10.11999/JEIT160225

2016-03-11;改回日期:2016-07-22;

2016-10-09

黄正峰 huangzhengfeng@139.com

国家自然科学基金(61274036, 61371025, 61474036, 61574052),安徽省自然科学基金(1608085MF149)

The National Natural Science Foundation of China (61274036, 61371025, 61474036, 61574052), Anhui Provincial Natural Science Foundation (1608085MF149)