基于1149.7标准的测试生成方法研究

2017-01-13潘金海颜学龙

潘金海,颜学龙

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

基于1149.7标准的测试生成方法研究

潘金海,颜学龙

(桂林电子科技大学电子工程与自动化学院,广西桂林 541004)

单芯片多核设计、片上系统等技术的不断发展为边界扫描技术带来了新的挑战,多扫描拓扑的测试矢量自动生成也成为了研究的重点与热点;基于1149.7标准对测试生成方法进行了研究,包括互连测试矢量、调试应用指令及数据和寄存器配置命令的生成,提出了测试生成的总体框架,以VS2008作为软件平台搭建自动测试生成系统,从数据库中提取目标板信息对寄存器进行配置,生成互连测试矢量或调试数据,最后将生成的信息插入数据库中,在互连测试矢量生成过程中,提出了一种基于边界扫描寄存器的功能来设置网络结点类型的新方法,有效地完成了对复杂网络的测试。

IEEE1149.7;边界扫描;互连测试;调试应用;寄存器命令

0 引言

边界扫描技术在发展初期被应用于大规模数字集成电路的可测性设计与故障诊断中,极大地提高了电路的可观测性与可控制性[1]。上世纪九十年代初,JTAG小组委员会首次颁布了1149.1标准,并经过不断地发展,于2001年形成了IEEE1149.1-2001标准,该标准致力于为组合印刷电路板以及其它基于高复杂性数字集成电路和高密度表面装配技术的印刷电路板存在的测试问题提供一种解决方案[2]。相对于以往传统的测试,JTAG采用边界扫描测试在测试技术上是一个飞跃[3]。但是随着单芯片多核设计、片上系统和叠层裸片等技术的不断发展,这套解决方案已很难满足测试、调试和功能应用等多方面的挑战。为此,可测试性总线标准委员会于2009年表决通过IEEE1149.7标准提出了紧凑型边界扫描技术(CJTAG)[4]。CJTAG在完全兼容1149.1标准基础的同时增加了新特性,支持片上多TAPC结构和后台数据传输机制,同时增加了芯片级旁路、功耗控制等功能,满足了多内核、多功能系统芯片的新要求。

由于目前国内外对CJTAG的研究还处于起步阶段,尤其是对1149.7标准的测试生成方法的研究几乎空白,因此本文主要研究基于1149.7标准的测试生成方法,包括互连测试矢量的生成,调试数据的生成,寄存器配置命令的生成。

1 1149.7标准的扫描拓扑结构

IEEE1149.7标准将边界扫描芯片的测试存取端口(TAP)从功能上划分为6个层次,每一层次都在它上一层次的基础上增加新的功能。T0层以TAP.1(支持IEEE1149.1标准的TAP控制器)为基础,支持多片上TAPC串行结构;T1层支持TAP.7(支持IEEE1149.7标准的TAP控制器)控制器命令及寄存器,功能复位与测试复位等;T2层通过使用1位的芯片旁路功能,可大幅度缩短扫描链长度,从而提高芯片的测试与调试效率;T3层支持可直接寻址的星型扫描拓扑,与传统的串行扫描拓扑相比,两者在扫描测试性能上有等同作用;T4层使用高级协议来传输扫描数据,TDIC与TDOC管脚可省略或作其他用途;T5层使用高级协议以及8个数据通道来传输后台数据。

IEEE1149.7标准测试控制器扫描拓扑分为串行扫描拓扑、四线星型扫描拓扑、两线星型扫描拓扑3种[5]。如图1所示为具有IEEE1149.7标准性能的边界扫描系统结构,该系统采用混合拓扑结构,DTS可通过TAP.7控制器来识别不同的分支。DTS选择一个或部分分支时可进行调试应用,选择全部分支时可进行测试应用。对于串行拓扑,其互连测试原理与IEEE1149.1标准的规定的原理相同,对于星形拓扑,则采用串行等价扫描进行测试。

图1 IEEE1149.7混合拓扑系统结构

2 系统测试生成总框架

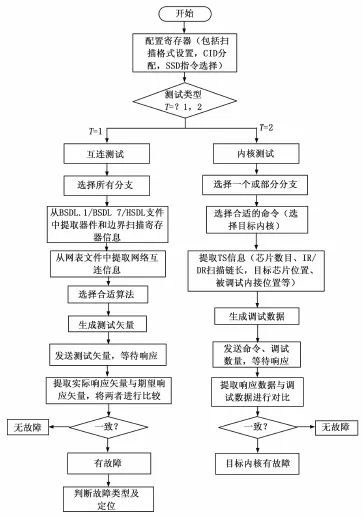

IEEE1149.7标准增加了新的特性以同时支持测试与调试应用,对于测试生成而言,需要生成测试应用需要的互连测试矢量,调试应用需要的调试数据和指令,同时需要对系统的寄存器进行配置,生成相应的配置命令代码。系统测试生成总框图如图2所示。

图2 测试生成总框架

2.1 互连测试矢量生成

2.1.1 互连测试矢量生成原理

边界扫描技术的主要思想是通过在芯片管脚和芯片内部逻辑电路之间增加由移位寄存器构成的边界扫描单元,实现对芯片管脚状态的串行设定和读取,使管脚具有可控性和可观测性[6]。互连测试是边界扫描技术的主要内容之一,它能够对电路板之间的互连线进行测试,主要检测电路板级的开路、短路或者呆滞型等故障[7]。测试向量生成是测试的基础和前提[8]。测试需要清楚知道各芯片间的互连情况,即测试所有芯片的网络互连是否出现故障,对象是所有支持边界扫描的芯片。1149.7标准提供了一个CLTAPC来连接系统测试逻辑(STL)和测试存取端口(TAP.7),硬件结构包括CLTAPC,边界扫描寄存器,相关指令有EXTEST,PRELOAD和SAMPLE。

测试原理与1149.1标准相同,即在靠近器件的每一输入/输出管脚处增加一个或多个移位寄存器单元[9]。在测试期间,这些寄存器单元用于控制输入管脚的状态,并读出输出管脚的状态,这样就可测试出电路板中器件的好坏及相互连接的正确性。在正常工作期间,这些附加的移位寄存器单元是“透明的”,不影响电路板的正常工作。

2.1.2 可测网络结点设置

影响互连测试矢量生成效率的因素主要在于生成初级矢量的算法和对可测网络类型的判断之上,由于国内外对生成初级矢量的走步0、走步1、改良计数序列等算法的研究已相对成熟,所以本文侧重研究如何有效而准确地判断出可测网络结点的类型,以为后续的初级矢量在链路中顺利展开作准备。

PCB电路板上的结点类型主要有两种,一种是用于输出数据的驱动结点,另一种是用于接收数据的检测结点。可测网络中驱动结点和检测结点的个数直接决定了可测网络的类型。一般来说可测网络有4种类型:具有一个驱动结点和一个检测结点的单入单出型;具有一个驱动结点和两个及两个以上检测结点的单入多出型;具有两个及两个以上驱动结点和一个检测结点的多入单出型;具有两个及两个以上驱动结点和检测结点的多入多出型。网络的最大入数M决定了DR链路矢量的个数N,两者之间的关系可用如下式(1)表示:

式(1)中,n表示网络个数,N表示DR链路矢量的个数,假设最大入数为M,则DR的有效链路矢量个数为网络个数的M倍,系统在发送第一条矢量之前需要多发送一条随机矢量将寄存器中原来的值顶出去,在发送完最后一条矢量之后也需要多发送一条随机矢量以将最后一条响应矢量取出来,所以要加上2。IR链路矢量的个数与DR链路矢量个数相等,式(2)表明了链路矢量的个数是DR链路矢量的两倍,为DR和IR链路矢量之和。

本文根据边界扫描单元的功能属性来设置网络结点的类型,其中与网络结点设置相关的边界扫描单元功能属性有如下几种:

input:为输入管脚接收数据。

output2:为二态输出提供数据。

output3:为三态输出提供数据。

bidir:双向管脚的双向单元。

control:控制一个三态驱动。

observe-only:只能接收I/O管脚相关的数据,不能输出。

设置网络结点类型主要分为以下3个步骤:

1)若结点的边界扫描单元功能属性只有input和observe-only两种类型,则结点设置为检测结点。

2)若结点的边界扫描单元功能属性只有output2和output3两种类型,则结点设置为驱动结点。

3)若结点的边界扫描单元功能属性既有input或observe -only类型,又有output2、output3或bidir类型,则先判断所属网络是否已经有驱动结点,若有,则设置为检测结点,否则为驱动结点,且将与该结点连接到同一总线上的其它三态管脚设置成同一类型。

2.2 调试指令及数据生成

调试需要清楚知道芯片内部的组件情况(EMTAPC),即调试一个或多个芯片内部的组件看其是否正常工作。1149.7提供的T2 TAP.7串行扫描拓扑与传统的TAP.1串行扫描拓扑相比,T2 TAP.7串行扫描拓扑能为STL(Systems Test Logic,系统测试逻辑)提供器件级旁路功能,即为STL提供1位的IR和DR扫描,而传统的TAP.1串行扫描拓扑只能对DR扫描旁路,不能旁路IR扫描。IEEE1149.7的全新芯片级旁路功能可冻结器件中无关的TAP控制器[10]。由于调试主要针对一个芯片而言,在这种情况下对其他不需要调试的芯片进行器件级旁路,可大大减少扫描链长度,从而提高调试效率。

器件级旁路要与SSD指令结合使用:先发送SSD_DA指令取消选择所有芯片;再发送SSD_SOC选择相应的芯片进行调试。

具体调试步骤如下:

1)发送SSD_DA指令,旁路所有芯片。

2)发送SSD_SOC指令,选择目标芯片的CLTAPC。

3)向CLTAPC发送TAPC_SELECT<field>指令,选择目标EMTAPC进行调试。

4)向目标EMTAPC发送TAPC_DBG调试指令,非目标芯片发送TAPC.bp旁路指令。

5)向目标EMTAPC发送32位的调试数据。

2.3 寄存器配置

控制器命令有two-part和three-part两种类型,一条two-part命令由CP1产生的5比特操作码和由CP2产生的5比特操作数构成。一条three-part命令除操作码和操作数外,还包括一条CR扫描[11]。如图3所示,CP1是由第一次DR扫描产生的5位操作码,CP2是由第二次DR扫描产生的5位操作数,CR是控制寄存器扫描,访问局部寄存器,其值最低可为0位,没有最高位限制。CP1和CP2组成了two-part命令,CP1、CP2和CR组成了three-part命令。

图3 寄存器命令结构

TAP.7控制器命令可实现对局部寄存器进行有条件的存储。在串行扫描拓扑中,TAP.7控制器命令可直接根据TAP.7控制器在扫描链中的位置来改变局部寄存器中的值进行基本配置,并设置扫描格式;在星形扫描拓扑中,则根据分配给TAP.7控制器的地址对局部寄存器进行存储,因此第一步首先要给控制器分配CID(Controller ID),再根据配置寄存器CNFG(Configuration Register)中的信息对寄存器进行基本配置,最后设置扫描格式。

3 测试结果与分析

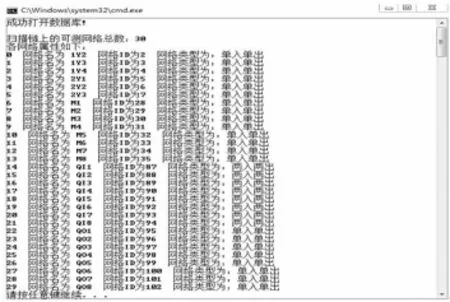

3.1 互连测试矢量生成结果与分析

互连测试以T0层TAP.1为例生成测试矢量。目标板由9个边界扫描芯片以串行扫描拓扑的方式构建测试对象,每个边界扫描芯片有18个边界扫描单元,指令寄存器长度8位。图4所示为网络分析后的结果,由图4可知,可测网络总数为30条,网络类型有单入单出和多入多出两种,其中网络QI1-QI8为两入两出类型,即最大入数为2。

图4 网络分析结果

针对目标板的线与故障采用走步0算法,图5展示了扫描链路矢量的部分截图,图中x代表任意值。由图可知,生成的DR链路长度为9个芯片的边界扫描单元数的总和,即162位;IR指令有72位,为9个芯片的指令寄存器长度总和,由上得知可测网络个数为30,最大入数为2,由公式(1)和(2)可知,生成的DR链路矢量个数应为62条,链路矢量总数应为124条,结果分析表明,本文采取的算法及测试方法能够有效地针对复杂网络生成所需要的测试矢量。

图5 互连测试生成结果

3.2 调试指令及数据生成结果与分析

如图6所示为数据库中提取出来的调试目标板的信息分析结果,图表中列出了目标板各条扫描链串包含的芯片个数,以及每个芯片内部的EMTAPC信息,包括EMTAPC的个数、旁路指令和调试指令等。

图6 调试目标板信息分析结果

本文选择第一条扫描链的芯片D4进行调试,则需要发送一条SSD_DA指令000旁路所有芯片,再发送SSD_SOC指令010 0101选择D4进行调试,由图6可知,D4中有两个EMTAPC,若调试EMTPAC1,则发送IR扫描指令<CLTAPC.TAPC_SELECT_NE,TAPC2.bp,TAPC1.DBG>,其中CLTAPC.TAPC_SELECT_NE为CLTAPC的选择指令,用于将目标EMTAPC置为Normal状态,非目标EMTAPC置为Exclusion状态,TAPC2.bp和TAPC1.DBG分别为EMTAPC2和EMTAPC1的旁路命令和调试命令,由图6可知其代码分别为0010和1 000。最后进行DR扫描,发送1位的CLTAPC旁路数据和32位的全0调试数据。图7显示了生成的调试指令及数据,由以上分析表明,所生成的指令和数据达到了预想的结果,符合要求。

图7 调试指令及数据

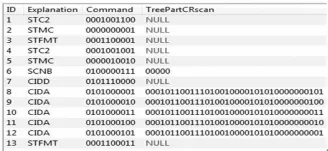

3.3 寄存器配置结果与分析

寄存器配置以四线星型扫描拓扑的调试应用为例,实验板采用5个T3和T4层TAP.7的边界扫描芯片。图8所示为根据1149.7标准对命令的定义而生成的命令代码。首先发送STC2(0001001100)和STMC(0000000001)命令进行初始化,选择四线星型拓扑,退出命令控制级别,继而生成扫描拓扑串序列,发送四条命令,分别为STFMT(0001100001)、STC2(0001001001)、STMC(0000010010)和SCNB(0100000111 00000),扫描拓扑串序列是DTS产生的命令序列,用于激励T3及以上的TAP.7控制器使TAP.7控制器能辨别出其所在的是哪个扫描拓扑分支;接着进行CID分配,首先发送CIDD,取消分配所有CID,进而发送CIDA命令为拓扑内所有控制器逐个分配CID,CIDA为three-part命令,CR部分为TAP.7控制器地址(TCA),系统根据CIDA的CR扫描部分来识别控制器;最后发送STFMT(0001100011)命令设置调试应用所需的JSCSAN3扫描格式。

图8 寄存器配置命令生成结果

4 结语

本文在IEEE1149.7标准基础上提出了测试生成的方法,包括互连测试应用所需的互连测试矢量生成和调试应用所需的调试指令和数据,并完成寄存器的配置,其中,对互连测试复杂网络的矢量生成方法进行了改进。利用VS2008和SQList搭建软件平台,结合数据库和面向对象的优点对测试生成方法进行设计。实验结果表明,该测试生成方法具有易操作、效率高的特点,并具备较高的准备性和故障覆盖率。

工艺的提升使得集成电路与芯片朝着超微型化、超复杂化的方向发展[11]。IEEE1149.7标准的新特性为边界扫描技术提供了更广阔的应用,同时也提出了更高的要求,在今后对紧凑型边界扫描技术的研究中,CJTAG IP的应用、测试系统的升级、多扫描拓扑的测试矢量自动生成将是研究的重点与热点[12]。因此,本文在IEEE1149.7标准的基础上对边界扫描关键技术之一的测试生成方法进行了研究,对边界扫描技术的发展具有重要意义。

[2]IEEE Standard Test Access Port and Boundary Scan Architecture [Z].IEEE Computer Society,2001.

[3]徐志磊.紧凑型JTAG接口的设计与验证[D].上海:上海交通大学,2010.

[4]IEEE Std 1149.7.IEEE standard for reduced-pin and enhancedfunctionality test access port and boundary-scan architecture[S].IEEE Standard Board,2009.

[5]徐志磊,郭 筝.基于IEEE1149.7的新一代测试接口实现与应用[J].信息技术,2010(08):164-166.

[6]徐建洁,李 岳,胡 政.边界扫描测试系统软件设计与实现[J].计算机测量与控制,2006(07):975-977.

[7]张学斌.基于JTAG的互连测试技术[J].今日电子,2004:5 -6.

[8]王美娟,吴 宁.基于边界扫描的板级测试向量自动生成[J].计算机工程,2009(12):279-282.

[9]潘小龙.基于边界扫描技术的测试系统的研究与应用[D].南京:南京航空航天大学,2008.

[10]Lau S.在SoC调试中重塑JTAG的作用[J].电子设计应用,2009(02):26-28.

[11]江 坤,高俊强.基于IEEE1149.7的TAP控制器命令研究[J].国外电子测量技术,2013(05):41-43.

[12]杨 轲,颜学龙.IEEE1149.7标准两线星型扫描格式研究[J].微电子学与计算机,2015(10):147-150.

[13]雷 加,黄文君.紧凑型边界扫描技术的功能与现状[J].计算机测量与控制,2012,20(2).

Study on Method of Test Generation Based on IEEE1149.7

Pan Jinhai,Yan Xuelong

(School of Electronic Engineering and Automation,Guilin University of Electronic Technology,Guilin 541004,China)

The continuous development of multicore-on-chip design and system-on-chip technology has brought new challenges to the boundary-scan technology,and the automatical test vector generation of multiple scan topology test has become a research focus and hot spots.To explore the method of test generation based on IEEE1149.7,including interconnect test vector generation,debugging application instructions and data generation and register command generation,a general framework for test generation is presented.A automated test generation system is built using VS2008 as software platform,and the information of target board is extracted from database to configure register and generate interconnect test vector or debug data,which will be inserted into the database.

IEEE1149.7;boundary scan;interconnect test;debugging application;register command

1671-4598(2016)08-0005-04

10.16526/j.cnki.11-4762/tp.2016.08.002

:TP274

:A

2016-03-03;

:2016-03-27。

潘金海(1989-),女,硕士研究生,主要从事智能控制与检测系统方向的研究。

颜学龙(1964-),男,硕士研究生导师,教授,主要从事可测性设计与故障诊断、测试信号处理方向的研究。