一种内嵌于DSP2F0X的ECAN设计及其通讯系统实现

2017-01-05

(中国电子科技集团公司第58研究所,江苏无锡214072)

一种内嵌于DSP2F0X的ECAN设计及其通讯系统实现

鲍宜鹏,强小燕

(中国电子科技集团公司第58研究所,江苏无锡214072)

通过对ECAN 2.0协议的深入研究,通过发送状态机以及过滤状态机实现消息的传输,完成了ECAN模块的核心逻辑设计,并通过APB总线将ECAN内嵌于DSP2F0X上,完成了ECAN的ASIC电路设计及其通讯系统的实现。主要介绍了该系统的硬件模块、连接结构和实现通信的基本配置及自检测试程序的设计。该系统的硬件实现使用verilog语言描述,采用了tcbn55lpwc工艺,在Synopsys/syn14.12环境下综合,信号传输速率最高可达1 Mb/s能力。实验结果表明,该系统完全满足CAN总线通信要求,与以往基于单片机的CAN总线通信系统相比较,具有更高的通讯效率及可靠性,同时功能也更加完备。

ECAN;总线协议;总线通信;自检程序

1 引言

上世纪80年代末期,伴随着汽车电子工业的发展,汽车各电子部件间的通讯就需要一种标准来规范,来减少通信信号线,CAN总线在这种背景下应运而生。随着CAN总线技术的发展和成熟,在铁路、轮船、楼宇自动化等领域,CAN都能够发挥作用[1]。在1986年,Bosch公司提出了正式的CAN协议。1991年 PHILIP公司首次提出标准和扩展的CAN协议。

在传统的CAN总线数据通信系统中,通常采用MCU+SJA1000+CAN总线收发器的方案实现,但是单片机速度较低、资源较少,当受到强电磁干扰时很容易出现程序跑飞。这种问题在航天控制中表现得尤为突出[2]。而在航天系统中,需要对数据进行大量的计算处理,因此本文提出采用DSP+ECAN的系统结构,保留了对数据的处理能力。本系统的设计完全兼容CAN2.0标准[3],性能较之已有的单片机CAN总线收发器系统,在进行总线通信时数据传输更加灵活方便,数据量更大,可靠性更高,功能也更加完备。

本文使用的DSP2F0X芯片是一款用于电机控制的SOC,芯片内部有一个32位的RISC处理器,工作频率达400 MHz,最大运算能力达6.4 GMACs。本文设计的ECAN是属于它的片上外设。

2 硬件实现

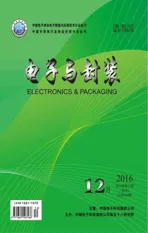

本通讯系统的整体结构如图1,将ECAN模块设计为DSP2F0X芯片的外设,DSP2F0X通过APB总线对ECAN模块的寄存器进行访存,从而对ECAN模块的内存、消息接收与发送、超时等功能进行管理。在进行数据传输时,进入ECAN 2.0协议核心层,将按照ECAN 2.0标准协议将消息缓存到接收缓存或者发送缓存中。ECAN与外界的接口通过一根接收数据线和发送数据线与外界相连。

图1 ECAN方框图和接口电路

2.1 消息设计

ECAN模块主要通过消息来实现不同设备之间的通讯,一个消息有以下几种类型。

数据帧:数据帧携带数据从发送器至接收器;

远程帧:总线单元发出远程帧,请求发送具有同一识别符的数据帧;

错误帧:任何单元检测到总线错误就会发出错误帧;

过载帧:过载帧用以在先行和后续的数据帧或远程帧之间提供附加的延时。

其中数据帧和远程帧可有使用标准帧(11位标示符)和扩展帧(29位标示符)两个格式。它们使用帧间空间与前面的帧分割。设计邮箱控制寄存器来标识要发送哪种类型的消息。

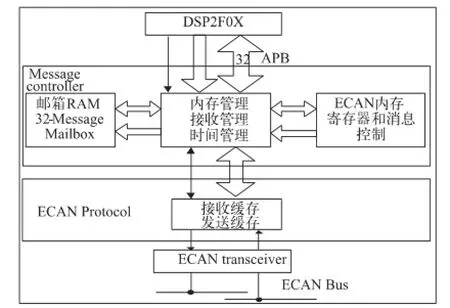

一个消息是否被有效接收,需要通过CRC序列检测,CRC序列包含了发送器的计算结果。接收器的CRC计算方法与发送器相同,如果计算结果与接收到的CRC序列不匹配,则会产生一个CRC错误,消息不能被有效接收,其CRC的计算代码见图2。图2中①式表示下接收到的数据与CRC最高位进行异或操作,②式表示CRC中间变量,③式表示CRC初始化。当需要CRC计算时,需要将CRC使能位打开,图2中④式表示CRC计算。

图2 CRC计算代码

2.2 模块设计

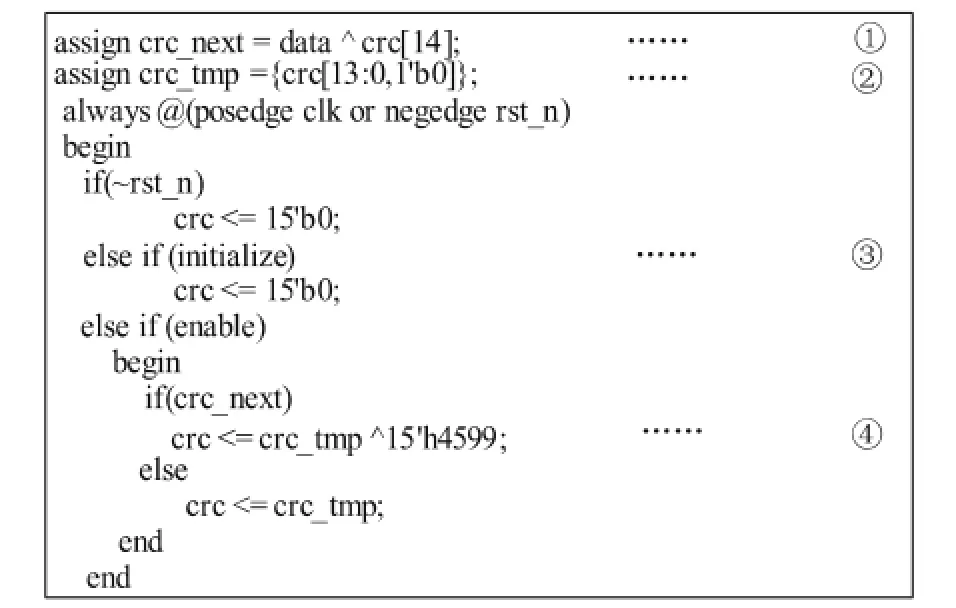

ECAN模块设计共包含8个子模块,具体划分如图3所示,而ECAN模块包含APB和ECAN时钟域。在 APB时钟域的模块分别为 ECAN_APB,ECAN_MEM,ECAN_FILTER,ECAN_TX;在ECAN时钟域的模块分别为ECAN_TIMER,ECAN_BTL,ECAN_BSP,ECAN_CRC。当不同时钟域的信号传输时需要做同步处理。

图3 ECAN子模块

ECAN_APB挂在APB总线上,该模块的设计目的是使DSP2F0X能够通过APB总线对ECAN的寄存器进行访存。ECAN_MEM模块可以对SRAM 128× 32和SRAM 96×32进行管理。

ECAN_BTL为位接收模块,工作在ECAN时钟域,由于发送单元和接收单元存在的时钟频率误差以及传输路径上的相位延迟会引起同步偏差[3],因此位接收单元需要通过硬件同步或者再同步的方法调整时序进行接收[3]。而为了防止突发错误,在本模块中设计了位填充功能,即当同样的电平持续5位时,则添加一位与前5位相反的数据,如图4所示。如果第6位的电平与前5位相同,将被视为错误并发送错误帧。由于位填充使原来的数据变长,因此在接收数据时需要将填充的位当作无效位来处理,保持数据的有效位不变。

图4 位填充

ECAN_TIMER模块的设计主要是为了实现时钟标志和超时功能,在模块中使用一个自由运行的32位计数器。当一个消息被存储或者被发送时,定时器的值被写入到邮箱的时间标志寄存器。当接收数据或发送数据发生超时,将超时标志发送到超时标志寄存器中。

ECAN_TX模块为发送控制模块,是ECAN模块的核心设计之一。发送逻辑控制采用有限状态机的方式完成,其状态机流程如图5所示。起始状态为IDLE,当检测到有数据要发送时,进入RDSELP状态。在RDSELP状态时,读取邮箱的优先级以及发送标志,当有发送标志时,依然返回RDSELP状态,否则进入RDID状态。在RDID状态读取邮箱的ID号,随后进入RDMDL状态。在RDMDL状态,需要读取低32位数据,当传输数据控制位为高时,进入RDMDH状态,读取高32位数据,否则,进入TXSTART状态。在TXSTART状态,开始发送数据,当发送结束标志置位时,则进入TXEND状态,结束发送状态,随后进入TXNEXT状态,为发送下一个数据做准备,随后再进入IDLE状态。

图5 发送逻辑控制状态机流程图

ECAN_BSP模块为ECAN 2.0协议的核心模块,负责发送与接收数据时,根据ECAN 2.0协议,产生ECAN总线上的控制信号和数据。

ECAN_FILTER为接收过滤模块,是ECAN模块的核心设计之一。本模块可以从ECAN_BSP模块中接收控制信号、ID号和数据,对接收到的数据进行解码和ID匹配,找到与ID匹配的邮箱,如果是数据帧,则存储数据,如果是远程帧,等待发送数据。模块的逻辑控制同样采用有限状态机的方式完成,状态机的流程如图6所示。

起始状态为IDLE,当检测到接收ID1请求,进入ID1状态。在ID1状态下,获取ID1号,当检测到接收ID2请求,进入ID2状态,进而获取ID2号。在ID2状态下,当检测到获取MEMID号时,进入RDMEM状态。在RDMEM状态下,从内存中获取ID号,随后进入CMP状态。在CMP状态下,将获取的ID号进行比较,当ID匹配,则进入WDT0状态,否则当检测到发送结束标志时,进入END状态。在WDT0状态时,如果接收成功,则进入WDT1状态,否则一直处于自身状态。在WDT1状态下,在发送接收成功且发送结束时,进入发送结束状态。在END状态下,将传输数据所用时间写入内存中,如果传输结束标志置位,则进入IDLE状态。

图6 接收FILTER的状态转换

2.3 仿真综合

整个硬件模块采用Verilog HDL语言进行描述,在cds/incisiv142环境下,调用NC_SIM进行仿真。选择两个ECAN设备之间的数据传输作为仿真Case,将ECAN0和ECAN1设备的两个输入输出引脚相连接,将ECAN0的前8个邮箱设置为发送邮箱,ECAN1的前8个邮箱设置为接收邮箱,其仿真波形见图7。在图7的仿真波形中,tx_o为输出引脚,rx_i为输入引脚,trs_reg为发送请求置位寄存器,tx_request为发送请求信号,ta_reg为发送响应寄存器,trs_fsm为发送有限状态机,filter_fsm为接收过滤有限状态机。当trs_reg不为0时,tx_request发送请求信号置1,启动发送有限状态机。当数据发送成功时,tx_successful信号置1,trs_reg中相应邮箱的发送请求位被清0,同时ta_reg中相应邮箱的发送响应位置1。

图7 ECAN设备之间数据传输的仿真结果图

ECAN1为接收设备,id_ok为 ID匹配信号,rx_end为接收数据结束信号,rx_id1为接收ID1请求,rmp_reg为接收消息未决寄存器。当收到数据时,rx_id1置位,启动接收过滤有限状态机,当数据接收结束,rx_end信号置1,同时rmp_reg相应邮箱的接收相应位置1。

系统的硬件实现在Synopsys/syn14.12环境中综合,采用了tcbn55lpwc工艺,一共包含约30870门数,可以达到100MHz运行速度,具有1Mbps的通信速率。2.4 通信接口

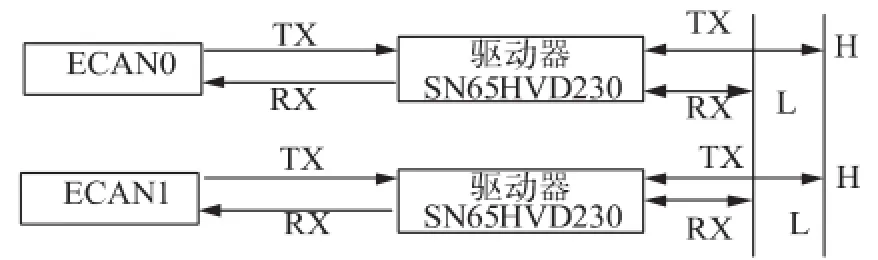

将不同设备的ECAN连接起来,需要采用驱动芯片,这里采用德州仪器公司生产的SN65HVD230,对ECAN发送引脚与接收引脚进行驱动,SN65HVD230芯片完全兼容ISO11898标准,具有抗干扰、热保护、信号传输速率最高可达1 Mb/s的能力[4]。图8为两个不同ECAN设备之间的连接示意图。

图8 ECAN设备之间的连接示意图

3 软件设计

3.1 应用程序设计

在使用DSP2F0X内嵌的ECAN设备之前,首先必须对DSP先进行配置,然后进行ECAN的设置,配置流程如图9。在DSP2F0X的初始化阶段,需要初始化DSP,配置ECAN的时钟门,配置APB时钟,此应用程序配置APB为100 MHz,由于ECAN两个引脚CANTX和CANRX在DSP2F0X中均为复用I/O口,因此,需要将DSP2F0X的I/O配置为ECAN的I/O口,且需要将CANTX配置为输出引脚,CANRX配置为输入引脚。

图9 ECAN设备的配置流程

在ECAN位初始化阶段,对位时序配置寄存器进行配置,包括采样次数和重同步方式、通讯波特率、同步跳转宽度。在初始化邮箱阶段,主要是设置邮箱的标识符、发送字节数和优先级别,数据帧还是远程帧及相应的邮箱赋初值。在ECAN发送阶段,配置邮箱为发送邮箱且使能,配置发送请求。在ECAN接收阶段,将DSP2F0X外部的ECAN设备的邮箱配置为接收邮箱且使能。完成上述配置后,接着实现对数据的发送和接收。在数据接收时,只有当所接收到的信息的标识符与相应邮箱的标识符相同时,数据才能被接收,否则该信息被过滤掉。

3.2 自检测试程序设计

在测试过程中,每次都要通过软件工具查看数据接收正确与否,多次测试需要多次人为查看结果,为了避免这种情况,设计自动检测程序,如图10所示。

图10 自检测试程序设计

首先将DSP2F0X的通用输入输出A端口配置成输出端口,如图10中①式,然后读出接收的数据,如②所示。将接收到的数据读出,与理想值进行比较,如图10中③式所示,如果比较相等,则程序继续执行,否则程序跳转到⑥式。

如果DSP2F0X的通用输出端口输出0xfeedbeef,则表明ECAN之间的通讯正确,如果DSP2F0X的通用输出端口输出0xdeadbeed,则表明ECAN之间的通讯出现错误,程序执行退出。

4 总结

本文提出采用DSP+ECAN的系统结构,不仅实现ECAN强大的通讯能力,还保留了DSP对数据的处理能力。本通讯系统的ECAN设计完全兼容CAN 2.0标准,通过ECAN配置和自检测试程序,可以方便实现ECAN设备之间的通讯和测试,较之已有的单片机CAN总线收发器系统,数据传输更加灵活方便,数据量更大,可靠性更高,功能也更加完备。

[1]Renjun Li,Chu Liu,Feng Luo.A Design for Automotive CAN Bus Monitoring System [C].Vehicle Power and Propulsion Conference,2008,VPPC'08.IEEE.3-5 Sept, 2008:1-5.

[2]陈萍,姜秀杰.基于FPGA的CAN总线通讯系统[J].计算机测量与控制,2009,17(12):2482-2484.

[3]BOSCH公司.CAN Specification V2.0[P].1995.

[4]德州仪器公司.SN65HVD230[P].Datasheet.

A Design of ECAN Embedded in DSP2F0X and Communication System

BAO Yipeng,QIANG Xiaoyan

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

By referring to ECAN 2.0 protocol and the message transmission process relating to the transmit state machine and filter state machine,the core logic of ECAN module is designed.By embedding ECAN in DSP2F0X though the APB bus,ECAN ASIC is designed and corresponding communication system is developed.The paper describes the hardware structure,the connection structure and the self-test program of the system.The system is described by the verilog language and developed using tcbn55lpwc technology.The system is integrated in the Synopsys/syn14.12 environment,the transmission rate reaching 1 Mb/s.The communication system improves communication efficiency and reliability with more functions.

ECAN;bus protocol;bus communication;self-test

TN402

A

1681-1070(2016)12-0026-04

2016-5-23