一种I2S音频数据处理电路的FPGA设计

2016-12-29赵海亮

赵海亮,李 琦

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

一种I2S音频数据处理电路的FPGA设计

赵海亮,李 琦

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

为满足现代汽车电子系统成本低、灵活性高和扩展性强的设计要求,基于FPGA,设计了一种I2S音频数据处理电路。以I2S协议为基础,采用ZYNQ-7000开发平台,为音频解码芯片AUDU1761与CPU完成音频数据通信,实现了音频输入和输出功能。为音频解码设计独立时钟,解决了传统设计中占用CPU过多的问题,同时可以降低失真。仿真结果表明,电路设计合理,可实现对音频数据的接收和发送功能。

I2S;FPGA;ZYNQ;独立时钟

对于现代汽车电子系统,音乐播放、FM广播等都是必备功能,因此,音频数据的解码芯片就必不可少。此外,现在相当多的智能车载系统都有语音控制功能,通过语音识别,系统能自动识别驾驶者的命令并进行相关操作,因此,音频编码芯片也必不可少。现在主流的音频编码、解码芯片绝大部分都支持I2S格式音频数据的传输。对于一个智能车载控制系统,I2S音频数据处理模块的工作效率至关重要。

由于音频的数据带宽相比系统总线的带宽要小得多,传输的数据量很小,故汽车电子设计中都将音频数据全部交给CPU处理[1],但是音频的实时性特点决定了CPU必须要在极为恰当的时刻把音频数据接收进来或发送出去,太早或太晚均会对音频的还原产生较大的影响。而采用CPU自行计时控制并按要求的格式传输数据将会占用过多的CPU时间,同时失真较大。鉴于此,为车载电子控制系统设计一种I2S音频数据处理电路,并增加了独立的时钟在恰当的时刻通知CPU传输音频数据,通过I2S协议传到音频解码、编码芯片。

1 I2S规范

I2S是IC间传输音频信号的一种接口标准,采用数字序列传输的方式传输2组(左右声道)音频数据。由于I2S传输协议将数据信号和时钟信号分开传输,故其抖动失真很小。

I2S使用MCK、BCK、WCK、SDA四条信号线[2]。其中:MCK为系统主时钟,通常为采样频率的256或384倍;BCK为串行比特流数据的同步时钟;WCK为字同步时钟,等于采样频率;SDA为串行数据。

图1为I2S通信时序。WCK和SDA均在BCK的下降沿处变化,在BCK的上升沿处采样。WCK在低电平表示正在传输的是左声道(left channel)数据,高电平表示正在传输的是右声道(right channel)数据。SDA在WCK变化后的第2个BCK周期开始传输数据,传输顺序由最高位到最低位。当WCK的单次脉冲宽度不足以传输全部的比特流数据时,低位的部分会被忽略;当全部比特流数据传输完毕而WCK的单次脉冲仍未结束时,低位的部分会自动补齐。基于此特点,I2S协议使不同音频数据长度的音频处理单元之间的相互兼容变得更加容易[3]。

图1 I2S通信时序Fig.1 Communication sequence of I2S

2 系统设计

本设计采用Xilinx ZYNQ-7000全可编程SOC系列目标板。ZYNQ-7000是首款将高性能ARM Cortex-A9硬核与可编程逻辑集成的器件,既可发挥处理器在处理复杂控制算法、运行操作系统等方面的优势,又利用FPGA在并行算法加速、可动态重配置的特点,实现了系统加速,增加了灵活性;同时给予片内结合的方案,减少了板材面积,降低了功耗,也加快了硬件开发的速度[4]。

ZYNQ-7000板使用AD公司的CODEC芯片ADAU1761与SOC的I2S接口相连。ADAU176是一款集成了数字音频处理的低功耗立体声CODEC芯片,支持48 kHz立体声录音和回放;采样率为8~96 kHz,且提供了数字音量调节功能。ADAU1761具有可编程特性,通过内部的DSP控制接口编辑该器件的控制寄存器,并且能够编译I2C、SPI两种规格的接口,但传输的音频数据只支持I2S规格。该芯片内部基本结构和接口如图2所示。

图2 ADAU1761内部结构及接口Fig.2 The structure of data processing module

3 系统工作原理

ADAU1761作为一款编解码芯片,本身无法单独工作,在工作时需要根据SPI格式的控制字进行编解码处理,之后进行数据传输,传输的音频数据满足I2S等格式;而ZYNQ芯片的作用是产生控制字并进行音频数据的存储,ZYNQ包含2个SPI控制器,可在主/从模式或多主机模式下工作。SPI控制器在连接到MIO的情况下,支持高达50 MHz的外部时钟,同时支持128 bit的读/写FIFO,但却不包含I2S接口模块,无法直接发送或者接收I2S格式的数据。因此,设计了一种音频接口模块,可以协调ADAU1761芯片与ZYNQ SOC芯片之间的数据交互,该模块既能将ZYNQ SOC发出的I2S格式音频数据传输到外部设备(耳机),也可以将外部设备(麦克风)I2S格式音频数据接收到SOC。

音频接口模块首先完成符合SPI传输协议的控制字的传输,控制数据传输有4种主要的信号线:CS(数据有效片选信号)、MODE(模式选择信号)、SDIN(控制数据输入信号)和SCLK(控制串行时钟信号)。在MODE有效的情况下,CS置低时,有效数据在SCLK的下降沿到来时立即开始传输。SPI数据位的传输采用大端模式的传输方式,先传高8位数据,后传低8位数据,连续传输16位。控制寄存器地址为高8位,控制数据为低8位。数据传输过程中,CS信号必须一直保持低位,待数据传输完成,立即拉高CS信号,传输终止[5]。音频信号的传输主要是数据从ADAU1761传入ZYNQ SOC和从ZYNQ SOC传入ADAU1761,其中音频信号的传输必须遵守I2S传输协议。

4 系统模块实现

系统模块主要由3个部分组成:1)SPI控制模块,负责在读/写使能的控制下将音频数据写入移位寄存器。2)I2S传输模块,通过4组移位寄存器完成数据的全双工传输,控制数据传输的时钟由分频器发出。3)时序接口模块[6],完成各种数据的基本传输。模块连接如图3所示。

调用接口AXI总线IP核,通过内部接口以及SPI、I2S直接将SOC的SRAM与AUDU1761芯片的外部接口相连。接口信号线有:写使能信号(WEn)、读使能信号(REn)、存储器片选信号(CSn)、数据信号(D0~D15)和地址选择信号(A0~A4),另外还有数据传输的主时钟信号(CLK)。数据处理模块结构如图4所示。

图3 模块连接图Fig.3 Module connection

图4 数据处理模块结构Fig.4 The structure of data processing module

SPI控制模块是在一组16位计数器的控制下完成数据的传输。在CPU发出写使能信号后,16位的数据寄存器SPI_data将数据并行写入寄存器,同时产生SPI使能信号,令计数器SPI_counter在主时钟MCK的下降沿开始记数,当计数器为1时,存储器片选信号的有效信号拉低,同时寄存器开始移位,数据开始传输;当计数器超过16时,存储器片选信号拉高,停止移位,数据传输终止。

I2S传输模块由4组移位寄存器实现,每组的最底层是按址寻址寄存器。当选中寄存器地址后,开始进行读写操作,读写完成后,在下一时钟节拍到来时,数据被并行写入移位寄存器。

I2S全双工传输结构如图5所示。CODEC1和CODEC2内的ADC传输数据完成串并转换后存于寄存器IN_REG1和IN_REG2,同时产生中断信号,通知CPU对G2C_TMP1和G2C_TMP2写数据。IN_REG1和IN_REG2的数据分别写入移位寄存器C2G_TMP1和C2G_TMP1,CPU依此从移位寄存器中提取数据;G2C_TMP1和G2C_TMP2的数据分别写入OUT_REG1和OUT_REG2,通过I2S格式分别写入DAC1和DAC2,这样就完成一次完整的全双工传输[7]。

图5 I2S全双工传输结构Fig.5 The full-duplex transmission structure of I2S

接口模块只是实现基本的传输功能,将ZYNQ CPU提供的片选使能、读写使能以及地址信号传输给SPI和I2S模块。

5 功能仿真与测试

5.1 模块配置

模块配置仿真用来测试模块能否被CPU正确配置完成所需功能。模块配置仿真结果如图6所示。从图6可看出,CPU从100 ns开始依次向地址30h、31h、32h和33h写入F0h、0Fh、01h和0Fh,全部中断在110 ns时被开启,在130 ns时模块被设置为由模块内分频器提供数据发送同步时钟,由外部输入数据接收同步时钟,在150 ns时BCK0被设置为MCK0的4分频,在170 ns时WCK被设置为BCK的64分频,即48 kHz的采样率。仿真结果表明,模块能够完成配置功能。

图6 模块配置仿真结果Fig.6 The simulation of module configuration

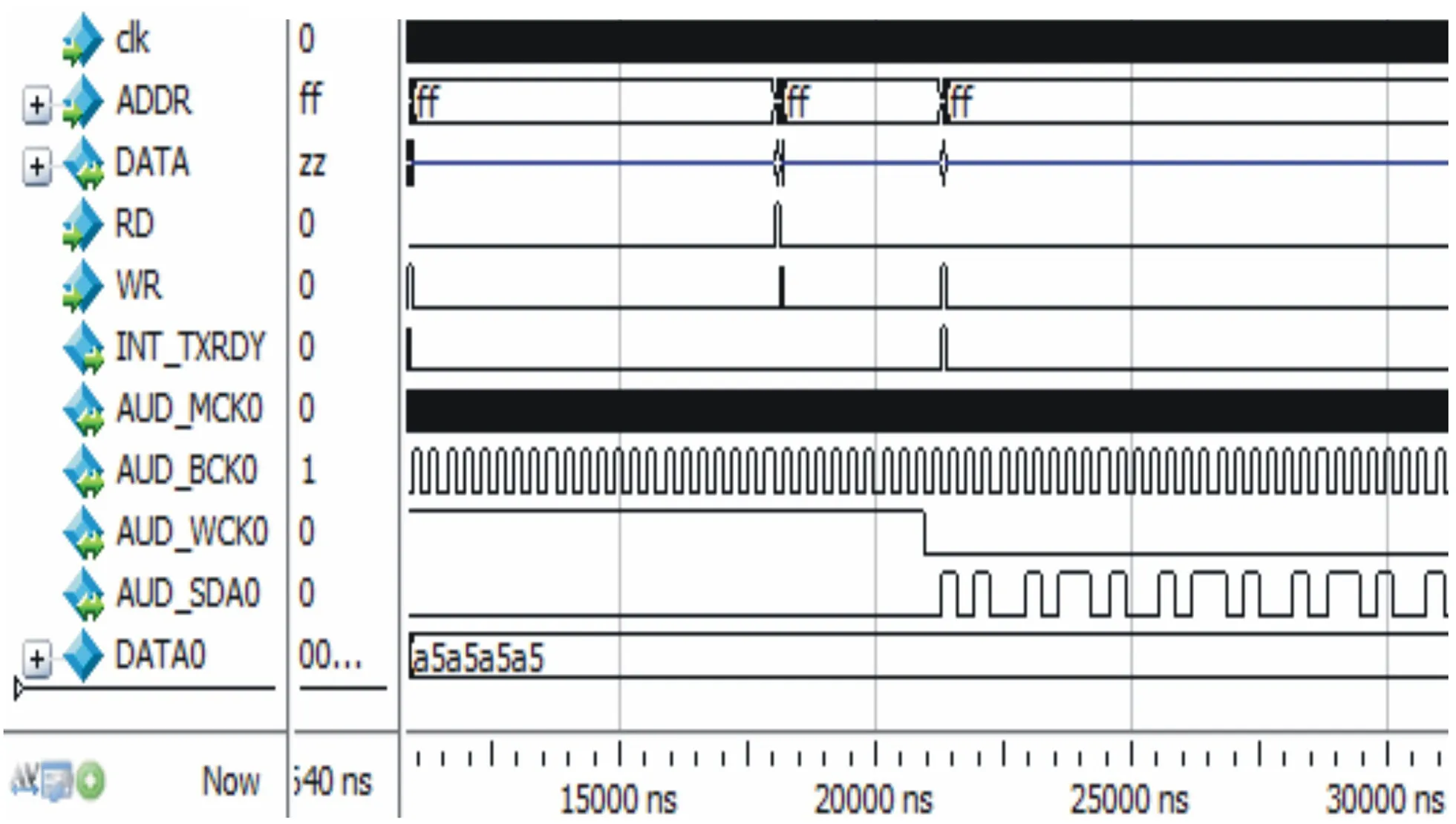

5.2 数据发送

数据发送仿真用于测试模块能否以中断形式通知CPU装入待发送的数据,并按I2S协议格式发送数据[8]。音频数据发送仿真如图7所示。从图7可看出,在10 800 ns时INT_TXRDY(数据发送就绪中断)输出中断信号后,CPU向DATA0寄存器写入待发送的音频数据A5A5A5A5h,在10 890 ns时DATA0寄存器写入预定数据;随后CPU向TXRDY(数据发送就绪)寄存器写入“1”,在10 900 ns时中断信号被清零;音频数据在下一次WCK0变化时由SDA0输出,其格式符合I2S协议要求。仿真结果表明,数据发送模块能完成I2S格式音频数据的发送。

图7 音频数据发送仿真Fig.7 The simulation of audio data sending

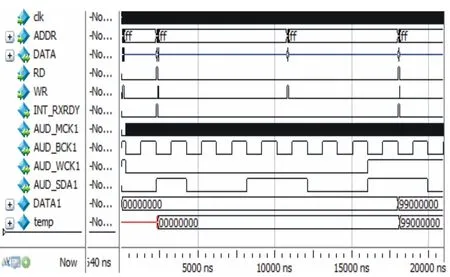

5.3 数据接收

数据接收仿真用于测试模块能否以I2S协议格式将接收的数据存入寄存器,并以中断形式通知CPU获取数据。音频数据接收仿真如图8所示。从图8可看出,从300 ns开始,音频数据99h开始从SDA1输入;在18 020 ns时DATA1寄存器被装入数据99000000h(99h的低位被自动补齐),INT_RXRDY(接收就绪中断信号)产生中断信号,CPU开始从DATA1寄存器读出数据,并存入测试用寄存器temp;在18 120 ns时temp内数据与输入的音频数据一致;随后CPU向RXRDY(接收就绪标志)寄存器写入“1”,中断信号被清零,完成本次音频数据的接收。仿真结果表明,数据接收模块能完成对I2S格式音频数据的接收。

图8 音频数据接收仿真Fig.8 The simulation of audio data reception

6 结束语

基于FPGA设计了一种音频模块电路,实现了XYNQ SOC上音频解析芯片ADAU1761与CUP及外设的通信。给音频模块增加一个独立时钟,解决了传统车载电子系统设计中采用CPU自行计时占用过多CPU的问题,同时也降低了信号失真。仿真结果表明,CPU能够正确完成配置,I2S格式音频数据的发送和CPU的接收也很及时,达到了设计的要求。不足之处是单独为车载电子系统增加一个音频数据处理模块,会增加芯片面积,不利于降低成本。

[1] 曹红兵.现代汽车电子控制技术[M].北京:机械工业出版社,2012:203-211.

[2] 邵福杰,张国利,周勇.基于I2S总线实现嵌入式语音采集与回放[J].微计算机信息,2011,27(6):23-25.

[3] 韩延义,李航,李岳.基于FPGA的音频芯片输出控制设计[J].实验室研究与探索,2013,32(5):95-96.

[4] 焦再强.基于Zynq-7000的嵌入式数字图像处理系统设计与实现[D].太原:太原理工大学,2015:7-10.

[5] 王丹雨,孙万蓉,成龙,等.基于FPGA实现的PCI-I2S接口转换电路[J].电子科技,2015,28(5):50-56.

[6] 关杰,王建.基于FPGA与ARM协同工作的网络数据采集系统[J].桂林电子科技大学学报,2014,34(8):315-318.

[7] 李小平.基于PCI总线结构的数据采集系统设计[D].哈尔滨:哈尔滨工程大学,2012:28-30.

[8] 赵磊.基于FPGA的音频信号处理的设计与实现[D].成都:电子科技大学,2012:47-51.

编辑:翁史振

Design of I2S data processing circuit based on FPGA

ZHAO Hailiang, LI Qi

(School of Information and Communication Engineering, Guilin University of Electronic Technology, Guilin 541004, China)

In order to meet the low-cost, flexible and extensible design demands of modern automotive electronic system, a hardware circuit which adopt the I2S agreement is designed based on FPGA. In ZYNQ-7000 development platform, the audio decoding chip AUDU1761 sets up data communication with CPU by this circuit. A clock is designed for decoding chip separately to solve the problem of high CPU usage which provides the clock by CPU, it can reduce distortion at the same time. The circuit is proved to be correct by the function simulation, the function of audio data receiving and sending can be completed greatly.

I2S; FPGA; ZYNQ; clock

2016-03-12

广西自然科学基金(2013GXNSFAA019335)

李琦(1976-),男,内蒙古呼和浩特人,教授,博士,研究方向为功率器件、电路与系统。E-mail:lqmoon@guet.edu.cn

赵海亮,李琦.一种I2S音频数据处理电路的FPGA设计[J].桂林电子科技大学学报,2016,36(6):461-465.

TN492

A

1673-808X(2016)06-0461-05