一种新型GaAs基无漏结隧穿场效应晶体管

2016-12-21骆东旭李尊朝关云鹤张也非孟庆之

骆东旭,李尊朝,关云鹤,张也非,孟庆之

(1.西安交通大学软件学院, 710049, 西安;2.西安交通大学电子与信息工程学院, 710049, 西安)

一种新型GaAs基无漏结隧穿场效应晶体管

骆东旭1,李尊朝2,关云鹤2,张也非2,孟庆之2

(1.西安交通大学软件学院, 710049, 西安;2.西安交通大学电子与信息工程学院, 710049, 西安)

针对隧穿场效应晶体管开态电流较低的问题,提出了一种新型GaAs基无漏结隧穿场效应晶体管结构,并对其性能进行了研究。在该结构中,沟道和漏区采用具有相同掺杂浓度的N型InGaAs材料,实现沟道/漏区无结化,简化了制造工艺;同时为了提高开态隧穿电流,源区采用不同于沟道的P型GaAsSb材料,实现异质源区/沟道结构。该结构能有效增大关态隧穿势垒宽度,降低泄漏电流,同时增加开态带带隧穿概率,提升开态电流,从而获得低亚阈值斜率和高开关比。仿真结果表明,在0.4 V工作电压下,该新型GaAs基无漏结隧穿场效应晶体管的开态电流为3.66 mA,关态电流为4.35×10-13A,开关电流比高达1010,平均亚阈值斜率为27 mV/dec,漏致势垒降低效应值为126。

隧穿;场效应晶体管;平均亚阈值斜率;隧穿势垒

随着集成电路特征尺寸的继续减小,目前广泛应用的金属氧化物半导体场效应晶体管(MOSFET)将面临更加严峻的挑战,如短沟效应加剧、泄漏电流增大、开关电流比降低等[1]。隧穿场效应晶体管(TFET)具有较好的亚阈值特性和较小的泄漏电流,是有效解决以上问题的一种新型器件。

不同于MOSFET的漂移扩散工作机制,TFET基于量子力学的带带隧穿机制,载流子从源区隧穿到沟道,形成隧穿电流。通过栅压控制隧穿势垒的高度和宽度来调控电流,因而不受载流子热分布的影响,具有低亚阈值斜率、高开关比和低功耗的特点。在过去几年中,针对隧穿场效应晶体管的电学特性,国内外学者做了详细的研究。2005年,Nirschl等人对TFET的缩放特性进行了研究,证明了TFET在65 nm时仍具有良好的电学特性[2];2007年,Choi等人运用实验的方法,验证了SOI结构TFET的亚阈值斜率可达到53 mV/dec[3];2013年,Ghosh等人提出了无结隧穿场效应晶体管的概念,并运用仿真软件证明无结TFET可改善开态电流和亚阈值斜率,提高器件的开关电流比[4]。无结TFET在源区、沟道和漏区均采用相同材料和相同掺杂浓度,通过沟道上的控制栅和源区上的辅助栅来调节沟道和源区的能带。由于无结TFET不需要陡峭的掺杂浓度梯度,因此更有利于器件小型化时突变结的制造。但与此同时,源区上辅助栅的加入增大了器件的制造难度。2014年,Asthana等人提出了Ⅲ-Ⅴ族异质无结隧穿场效应晶体管[5],与无结TFET相比,为了提升开态电流,该异质无结TFET在源区和沟道采用不同的Ⅲ-Ⅴ族半导体材料。这是因为Ⅲ-Ⅴ族半导体材料具有禁带宽度窄和载流子隧穿质量小的特点,同时源区和沟道采用异质结可形成交错或断裂能带结构,能够有效减小隧穿势垒宽度,有利于提高载流子隧穿概率,进而提高器件开态电流[6-10]。仿真结果表明,Ⅲ-Ⅴ族异质无结TFET适用于超高速低功耗的应用场合。虽然源区和沟道使用不同的材料,但由于掺杂类型均为N型,源区能带仍需要辅助栅来调节,因此增大了器件的制造难度。

通过对以上研究的回顾发现,目前TFET的主要研究热点是提升开态电流和器件小型化,因此,本文提出一种新型GaAs基无漏结隧穿场效应晶体管。为了提升开态电流,该结构源区采用P型掺杂的GaAsSb材料,沟道和漏区采用N型掺杂的InGaAs材料。这是因为Ⅲ-Ⅴ族半导体材料InxGayAs和GaAsxSby具有较宽的带隙调节范围,通过调节各自的合金成分,使组成的异质(源/沟道)结可形成各种能带对齐结构,有利于提高隧穿器件开态电流[11-13]。同时,由于源区采用P型掺杂,因此源区能带不需要借助辅助栅调节,简化了器件结构,有利于器件小型化。通过数值仿真方法研究了本文器件的转移、输出、亚阈和短沟道等特性,并与常规P-I-N TFET性能进行对比,以验证其性能的优越性。

1 传统P-I-N TFET

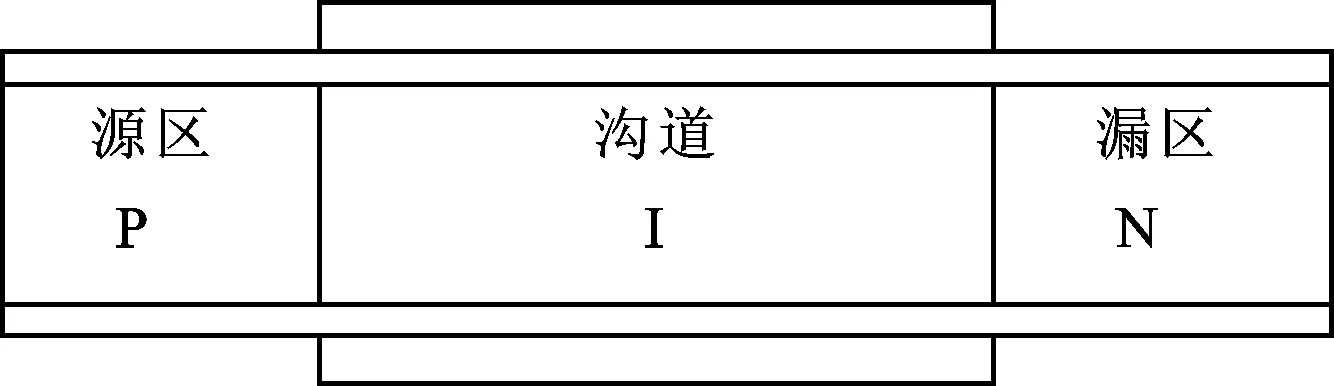

随着越来越多新结构的出现,TFET的性能得到了进一步的提升。这些新结构都是在传统P-I-N TFET的基础上进行结构和参数优化而得到的。传统P-I-N TFET的结构如图1所示,其源区为P型掺杂,沟道为I型掺杂,漏区为N型掺杂,沟道采用双栅控制。

图1 传统P-I-N TFET结构

传统P-I-N TFET的工作原理是电子通过带带隧穿的方式从源区价带隧穿到沟道导带。带带隧穿原理如图2a所示,在不加栅压的情况下,由于源区和沟道界面处存在较大的势垒宽度,只有极少的电子能从源区价带隧穿到沟道导带,因此漏电流极低;当栅压增大时的原理如图2b所示,源区和沟道界面处势垒宽度变窄,少量电子从源区价带隧穿到沟道导带,使得沟道导带自由电子变多;当栅压继续增大时的原理如图2c所示,越来越多的电子能隧穿到沟道导带,同时在漏电压VD的作用下形成正向漏电流。

图2 带带隧穿原理图

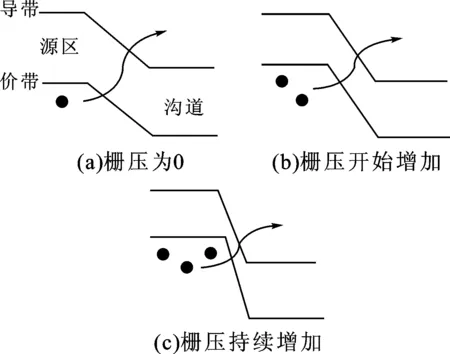

2 GaAs基无漏结TFET

LG:栅极长度;LD:漏区长度;Ls:源区长度;Tox:绝缘层厚度;Tch:沟道厚度图3 GaAs基无漏结TFET结构

新型GaAs基无漏结TFET(以下简称无漏结TFET)结构如图3所示,沟道和漏区采用N型InGaAs,通过选择栅材料的功函数调节沟道能带,实现沟道/漏区无结化,简化制造工艺;源区采用P型GaAsSb,实现异质源区/沟道结构,提高开态电流。

利用二维数值仿真软件Sentaurus TCAD对器件性能进行仿真研究。仿真中使用的主要参数:LG=20 nm,LD=LS=10 nm,绝缘层HfO2的厚度Tox=2 nm,P型源区采用GaAs0.35Sb0.65材料,源区掺杂碳原子浓度为5×1019cm-3,N型沟道和漏区采用In0.7Ga0.3As材料,掺杂硅原子浓度为1×1018cm-3,栅极材料为Au。

仿真中,加入了带带隧穿模型(band-to-band tunneling model);考虑到各网格隧穿电流取决于横截面的能带结构而不是电场,加入了非局部模型(nonlocal model);考虑到器件沟道重掺杂,加入了禁带宽度变窄模型(bandgap narrowing model);考虑到实际器件存在缺陷或陷阱,加入了Shockley-Read-Hall模型;加入Schenk’s陷阱辅助隧穿模型(Schenk’s trap-assisted tunneling model)以反映电子通过陷阱辅助隧穿机制;加入量子限制模型(quanturm confinement)以反映由于重掺杂和薄氧化层厚度所造成的表面陷阱效应和量子限制效应[14-17]。

为了反映新结构器件的性能提升,将其与传统P-I-N TFET进行性能对比。其中,P-I-N TFET的材料为GaAs0.35Sb0.65,P型漏区掺杂碳原子浓度为5×1019cm-3,N型漏区掺杂硅原子浓度为1×1018cm-3,弱P型沟道掺杂碳原子浓度为1×1017cm-3。

3 仿真结果分析

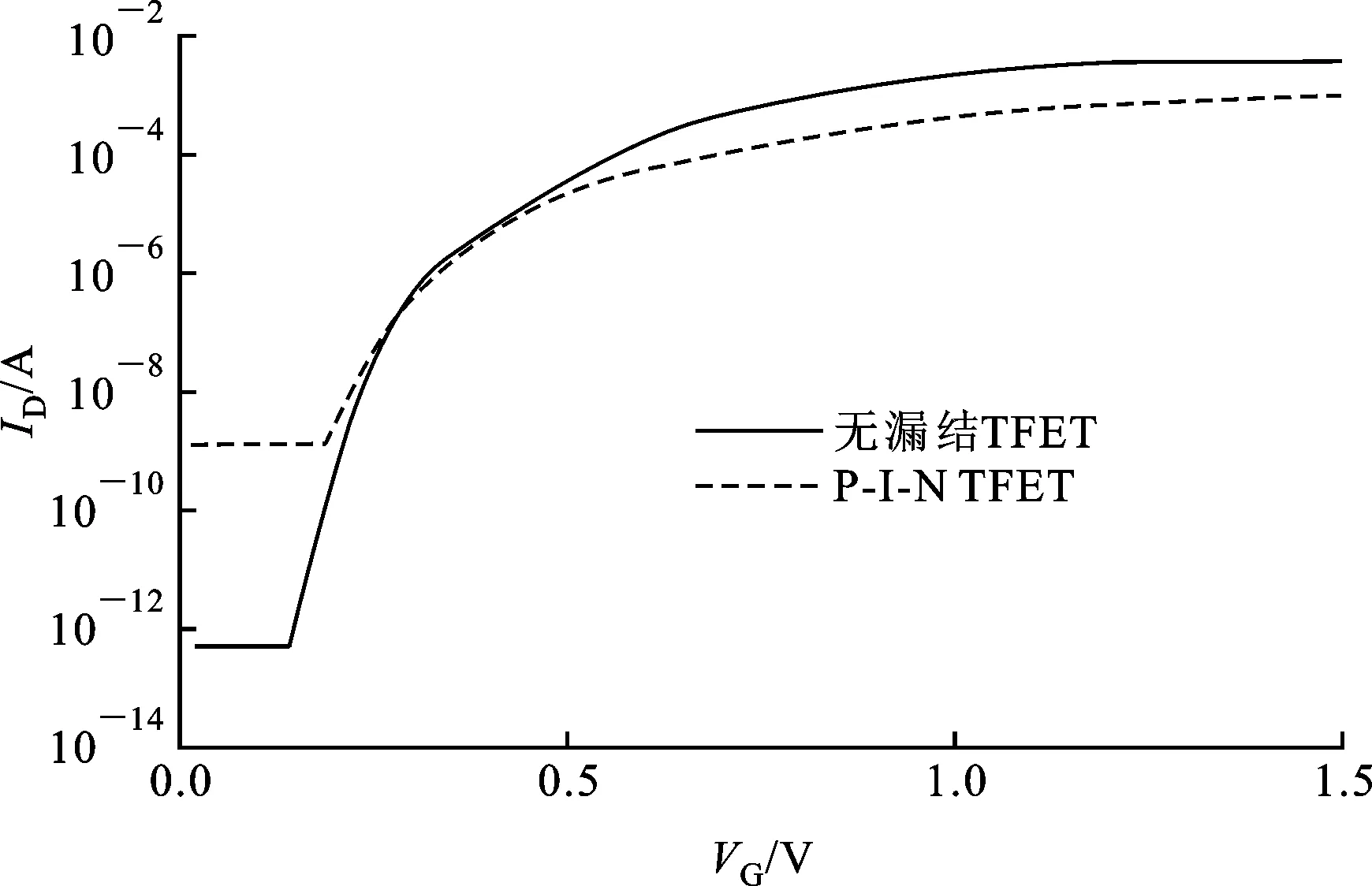

图4 2种TFET的转移特性曲线对比

常温下无漏结TFET在漏压为0.4 V时的转移特性曲线如图4所示。从图4可以看出,无漏结TFET的开态电流Ion为3.66×10-3A,关态电流Ioff为4.35×10-13A,开关电流比Ion/Ioff为1010;P-I-N TFET的开态电流Ion为9.49×10-4A,关态电流Ioff为1.21×10-9A,开关电流比Ion/Ioff为105。可见,无漏结TFET比 P-I-N TFET具有更高的开态电流、更低的关态电流和更高的开关比,因此无漏结TFET更适用于低压低功耗领域。

常温下无漏结TFET在栅压为1.0 V时的输出特性曲线如图5所示。可以看出,在相同栅压及漏压下,无漏结TFET的开态电流是传统P-I-N TFET的5倍多。

图5 2种TFET的输出特性曲线对比

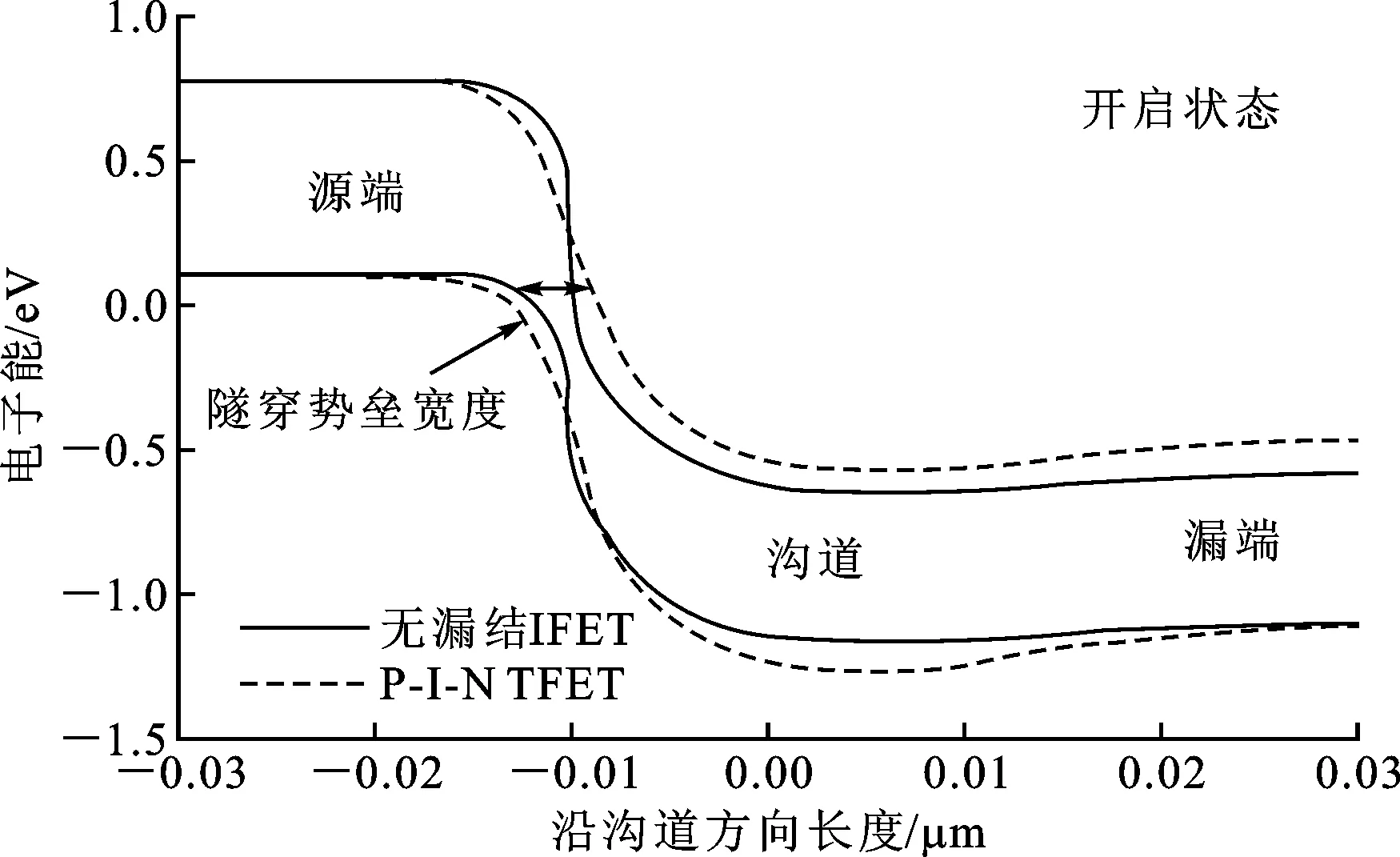

为了解释无漏结TFET性能提升的原因,图6给出了两种器件关态和开态时的能带结构图。

由于无漏结TFET的沟道和漏区同为N+掺杂,需要通过栅极的功函数来调节沟道的能带。本结构所使用的栅极材料是功函数为5.1 eV的Au。从图6a可以看到,栅极材料在几纳米的范围内将沟道的能带提升到恰当的位置使器件关断,而P-I-N TFET并不能通过掺杂获得如此陡峭的掺杂浓度梯度。在关闭状态时,无漏结TFET比P-I-N TFET具有更大的隧穿势垒宽度,源区价带的电子由于较宽的隧穿势垒宽度,不易通过带带隧穿机制隧穿到沟道的导带,所以关态电流比较小。

当器件处于开启状态时,带带隧穿主要发生在源区和沟道交界处。由于无漏结TFET的源区和沟道分别是GaAs0.35Sb0.65和In0.7Ga0.3As材料,因此形成交错能带[18-19]。从图6b可以看出,无漏结TFET源区和沟道间能带比P-I-N TFET更加陡峭,因而具有较小的隧穿势垒宽度,增大了带带隧穿概率,形成更大的开态电流。

(a)关闭状态能带结构

(b)开启状态能带结构图6 2种TFET的能带结构对比图

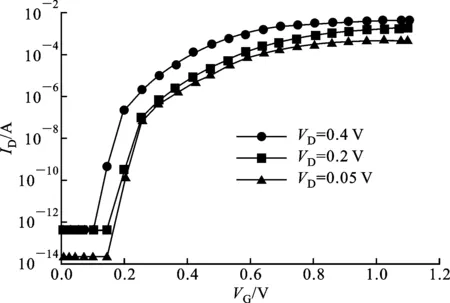

图7 不同漏压下的转移特性曲线

无漏结TFET在不同漏压下的转移特性如图7所示。可以看到,随着栅压的升高,开态电流增大。这是因为升高的栅压导致隧穿势垒宽度减小,增大了带带隧穿概率,使更多的电子从源区价带隧穿到沟道导带,增大了开态电流。当漏压为0.4 V时,无漏结TFET表现出优良的传输特性,Ion=3.66×10-3A,Ioff=4.35×10-13A,Ion/Ioff=1010。

TFET的亚阈性能可用平均亚阈斜率(ASS)描述

(1)

式中:Vt代表阈值电压;It代表阈值电压处电流;Vref代表参考点电压;Iref为参考点处的电流。

考虑图7漏压VD为0.4 V时的转移特性曲线,将电流开始突然增大时的栅压0.16 V作为参考点电压,参考电流Iref=3.1×10-13A,将电流达到1×10-5A时的栅压0.36 V取做阈值电压Vt。由式(1)计算达到的SASS为27 mV/dec。采用同样的方法可以得到P-I-N TFET的SASS为63 mV/dec。可见,新结构器件能有效降低平均亚阈值斜率,具有较高的开关转换速度。

漏致势垒降低效应(DIBL)可由以下公式计算[20]

(2)

式中:Vt|VD=0.4 V表示当VD=0.4 V时的阈值电压;Vt|VD=0.05 V表示当VD=0.05 V时的阈值电压。从图5可以计算出无漏结TFET的EDIBL为126。采用同样的方法可以得到P-I-N TFET的EDIBL为194。可见,无漏结TFET能有效抑制漏致势垒降低效应。

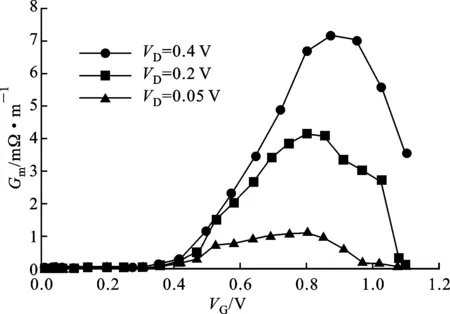

图8为无漏结TFET在不同漏压下的跨导Gm随栅压的变化曲线。Gm反映了栅压对漏电流的控制作用,Gm越大,增益越大。从图8中可以看出,随着栅压的增大,跨导先增大后减小。这是由于随着栅压增大,隧穿势垒宽度减小,从源区价带隧穿到沟道导带的电子数增加;当栅压继续增大时,隧穿势垒宽度减小速度变缓,并最终达到一恒定值,漏电流趋于饱和,因此跨导降低。

图8 不同漏压下跨导随栅压的变化曲线

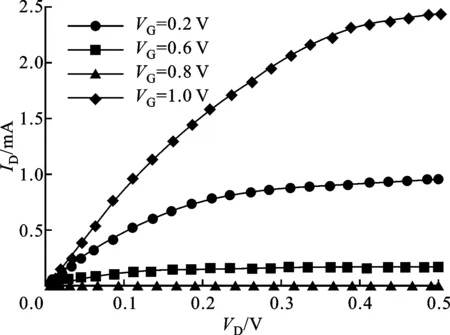

图9 不同漏压下输出特性曲线

图9为无漏结TFET在不同栅压下的输出特性曲线。从图9中可以看出,随着漏压增加,漏电流逐渐增加,并最终趋于饱和。在饱和区,输出特性曲线比较平直,表明该结构具有较弱的沟道长度调制效应。漏电流在饱和前表现出非线性,这是由非线性的隧穿机制所造成。

4 结 论

本文设计了一个沟道长度为20 nm的新型GaAs基无漏结隧穿场效应晶体管,根据仿真结果详细地分析了其电学性能。在本文设计的GaAs基无漏结TFET结构中,沟道和漏区采用N型InGaAs材料,源区采用P型GaAsSb材料,实现了沟道/漏区无结化和异质源区/沟道结构。该结构不仅能有效增大关态隧穿势垒宽度,减小泄漏电流,而且能提升开态带带隧穿概率,增大开态电流,从而获得低亚阈值斜率和高开关电流比。仿真结果表明,本文设计的新型GaAs基无漏结隧穿场效应晶体管的开关电流比高达1010,平均亚阈值斜率为27 mV/dec。

[1] 韩方忠. 隧穿场效应晶体管的模拟研究 [D]. 上海: 复旦大学, 2012.

[2] NIRSCHL T, SCHAPER U, EINFELD J, et al. Impact of mask alignment on the tunneling field effect transistor (TFET) [C]∥Proceedings of the 2005 International Conference on Microelectronic Test Structures. Piscataway, NJ, USA: IEEE, 2005: 43-46.

[3] CHOI W, LEE J, PARK B. Integration process of impact-ionization metal-oxide-semiconductor devices with tunneling field-effect-transistors and metal-oxide-semiconductor field-effect transistors [J]. Japanese Journal of Applied Physics, 2007, 46(1): 122-124.

[4] GHOSH B, AKRAM M W. Junctionless tunnel field effect transistor [J]. IEEE Electron Device Letters, 2013, 34(5): 584-586.

[5] ASTHANA P K, GHOSH B, GOSWAMI Y, et al. High speed and low power ultradeep submicrometer Ⅲ-Ⅴ heterojunctionless tunnel field-effect transistor [J]. IEEE Transactions on Electron Devices, 2014, 61(2): 479-486.

[6] BARDON M G, NEVES H P. Pseudo two dimensional model for double-gate tunnel FETs considering the junctions depletion regions [J]. IEEE Transactions on Electron Devices, 2010, 57(4): 827-834.

[7] 郭维廉. 共振隧穿二极管的物理模型 [J]. 微纳电子技术, 2006(4): 167-171. GUO Weilian. Physical model of resonant tunneling diode [J]. Micro-Nano-Electronic Technology, 2006(4): 167-171.

[8] MOHATA D, MAYER T, DATTA S, et al. Temperature dependent characteristics of a vertical tunnel FET [J]. IEEE Electron Device Letters, 2010, 31(6): 564-566.

[9] MIMURA T, ODANI K. GaAs microwave MOSFETs [J]. IEEE Transactions on Electron Devices, 1978, 25(6): 573-579.

[10]HINKLE C L, SONNET A M, VOGEL E M, et al. GaAs interfacial self-cleaning by atomic layer deposition [J]. Applied Physics Letters, 2008, 92(7): 071901.

[11]ZHU Y, HUDAIT M K. Low-power tunnel field effect transistors using mixed As and Sb based heterostructures [J]. Nanotechnology Reviews, 2013, 2(6): 637-678.

[12]BIMBERG D, KIRSTAEDTER N, USTIONV V M, et al. InGaAs-GaAs quantum-dot lasers [J]. IEEE Journal of Selected Topics in Quantum Electronics, 1997, 3(2): 196-205.

[13]徐会芳. 新型纳米器件的研究与建模 [D]. 合肥: 安徽大学, 2015.

[14]PAUSSA A, PALESTRI P, GEROMEL M, et al. Simulation of the performance of graphene FETs with a semiclassical model, including band-to-band tunneling [J]. IEEE Transactions on Electron Devices, 2014, 61(5): 1567-1574.

[15]SYNOPSYS Corporation. Sentaurus device user guide [EB/OL]. (2010-10-13)[2015-04-23]. http: ∥www. docin.com/p-351831400.html.

[16]SCHENK A. A model for the field and temperature dependence of Shockley-Read-Hall lifetimes in silicon [J]. Solid-State Electronics, 1992, 35(11): 1585-1596.

[17]HANSCH W, KIRCHNER R, VOGLSANG T, et al. Carrier transport near the Si/SiO2interface of a MOSFET [J]. Solid-State Electronics, 1989, 32(10): 839-849.

[18]KUMAR M J, SIVA M. The ground plane in buried oxide for controlling short-channel effects in nanoscale SOI MOSFETs [J]. IEEE Transactions on Electron Devices, 2008, 55(6): 1554-1557.

[19]MOHATA D K. Demonstration of MOSFET-like on-current performance in arsenide/antimonide tunnel FETs with staggered hetero-junctions for 300 mV logic applications [C]∥ Proceedings of IEEE International

Electron Devices Meeting. Piscataway, NJ, USA: IEEE, 2011: 33-37.

[20]BRESSON N, CRISTO S, LWAI H, et al. Integration of buried insulators with high thermal conductivity in SOI MOSFETs: thermal properties and short channel effects [J]. Solid-State Electronics, 2005, 49(9): 1522-1528.

(编辑 刘杨)

A Novel GaAs-Based Tunnel Field-Effect Transistor Without Drain Junction

LUO Dongxu1,LI Zunchao2,GUAN Yunhe2,ZHANG Yefei2,MENG Qingzhi2

(1. School of Software Engineering, Xi’an Jiaotong University, Xi’an 710049, China;2. School of Electronic and Information Engineering, Xi’an Jiaotong University, Xi’an 710049, China)

A novel GaAs-based tunnel field-effect transistor without drain junction is proposed to improve the on-state current and its performance is investigated. The transistor uses N-type InGaAs with the same doping concentration in the channel and drain to form junctionless channel/drain and to simplify the manufacture process, while P-type GaAsSb is used in the source to produce hetero junction source/channel and to increase the on-state current. The widened tunnel barrier in the off-state decreases the leakage current, and the promoted band-to-band tunneling probability in the on-state increases the driving current, so that both the low subthreshold slope and the high ratio between on-state current and off-state current are obtained. Numerical simulations show that the novel device achieves an on-state current of 3.66×10-3A, and an off-state current of 4.35×10-13A under 0.4 V voltage, and the ratio between on-state current and off-state current is 1010, and that an average subthreshold slope of 27 mV/dec and a DIBL of 126 are obtained.

band to band tunnel; tunnel field-effect transistor; average subthreshold slope; tunnel barrier

2015-09-06。

骆东旭(1990—),男,硕士生;李尊朝(通信作者),男,教授,博士生导师。 基金项目:国家自然科学基金资助项目(611760380)。

时间:2015-11-27

10.7652/xjtuxb201602012

TN386.6

A

0253-987X(2016)02-0068-05

网络出版地址:http:∥www.cnki.net/kcms/detail/61.1069.T.20151127.2115.004.html