基于CPLD的多电源上电时序的控制设计

2016-12-16株洲中车时代电气股份有限公司通信信号事业部马茗岗罗永升

株洲中车时代电气股份有限公司通信信号事业部 马茗岗 罗永升 孙 尚 陈 展

基于CPLD的多电源上电时序的控制设计

株洲中车时代电气股份有限公司通信信号事业部 马茗岗 罗永升 孙 尚 陈 展

随着高速数字信号的快速发展,对集成多核和高速接口的处理器的电源的上电时序的设计则越来越重要,严格的上电时序保证了器件免受损坏和进入良好的工作状态;基于CPLD的多电源上电时序的控制设计则更加可靠、稳定、精确。

电源;上电时序;CPLD

1 引言

随着高速数字信号的快速发展,对数字信号的处理方式也越来越丰富,而集成多核和高速接口的处理器为复杂的嵌入式系统的设计提供了便利和灵活;电源作为集成电路的食量,在整个设计中是不可或缺的,而上电时序的步步为营,正是开启各个集成电路模块之门的重中之重,严格的上电时序保证了器件免受损坏和进入良好的工作状态。而传统的上电时序由时序控制电路(延迟电路)来控制,这种方式很容易受外界环境的影响(如温度),基于CPLD控制的上电时序则更加可靠和稳定,比延迟电路更加精确。

2 多电源的上电时序

在集成电路的设计中,整个系统或者一块主板内部存在着多电源的供电,如5V、3.3V、1.8V、1.5V、1.2等,从开机上电、内核上电(CPU、FPGA、DSP)、IO上电,整个上电的过程都有严格的时序控制,这个控制上电的先后顺序就是上电时序。

图1 延迟电路控制多电源上电

大量的器件如CPU、FPGA和DSP相互之间的供电电压不同,上电时序不同;同一器件,内核和IO之间的上电时序也有严格的要求,而混乱的上电时序将会让整个系统崩溃或者器件损坏,严格的上电时序保证了器件免受损坏和进入良好的工作状态。

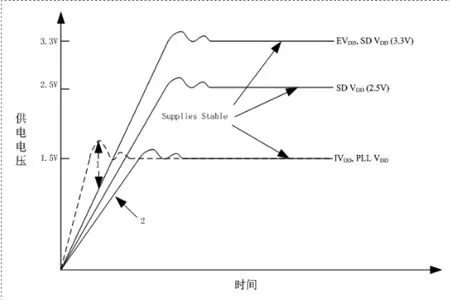

图2 CPU上电时序图

图2中描述了一款CPU上电时序图,其中EVDD是IO供电电压,SD VDD为SDRAM或者DDR供电电压,PLLVDD为锁相环供电电压,I VDD为CPU内核供电电压。

在传统的上电时序控制中,通过延时电路来控制,在设置延时电路时,数据手册则一般给出上电的软启动(soft-start)计算公式,根据公式来确定上电的时间,不同的电源模块则会有不同的计算公式。而延时电路的器件电容很容易受到温度的影响,使得上电时序不精确。

图3 CPLD控制多电源上电

图4 基于CPLD的多电源上电时序的控制设计流程图

3 基于CPLD的多电源上电时序的控制

为了达到更精确,更稳定的上电时序,在原有的上电时序的方式中,做出改进,通过CPLD来控制多电源的上电时序。在DC-DC线性稳压器模块中由“ON/OFF”或者“EN/SSN”引脚,用来使能电源模块的输出,而本文的设计就是利用CPLD来控制这些使能引脚,已达到精确的控制电源上电时序的目的,如图3所示

采用可编程逻辑器件CPLD的设计具有较强的灵活性,通过硬件描述语言对其进行编程设计。基于CPLD的多电源上电时序的控制设计流程图如图4所示。

首先禁止所有的电源模块输出,使能CPU、FPGA和DSP等器件的复位功能;通过CPLD的计数来控制延时输出使能信号,达到精确的控制上电时序的目的;使能信号使能电源模块输出各个电压,并检测各个电压的输出情况,当正确时,电压输出后使能时钟信号,然后结束复位,当不正确时触发报警复位等处理。

4 结束语

本文阐述了基于CPLD的多电源上电时序的控制的一种设计方案,并和利用延时电路来控制上电时序进行了了对比,而基于CPLD控制的上电时序则更加可靠和稳定,比延迟电路更加精确,因为CPLD能灵活和更准确的编程实现计数延时,并且CPLD受环境的影响相对较小。

[1]MCF548x ColdFire Microprocessor,Rev.4[Z].Freescale,2007.

[2]刘宝明,苏培培.高功耗嵌入式单板计算机的电源设计与实现[J].计算机工程与设计,2012,33(3):941-946.

[3]廖建兴.通信设备低压BUCK电源模块设计要求[J].应用分析,2015,1:46-50.

Supply Voltage Sequence Control Design Based on CPLD

MA Minggang,LUO Yongsheng,SUN Shang,Chen Zhan

(Signal & Communication Business Unit,Zhuzhou CRRC Times Electric Co.,Zhouzhou,Hunan 412001,China)

With the rapid development of high speed digital signal,the integration of multi cores and high speed interface processors on the supply voltage sequence is more and more important,strict sequencing could ensure the devices from damage and enter a better working condition;Supply voltage sequence control design based on CPLD is more reliable,stable and accurate.

Supply Voltage;Supply Voltage Sequence;CPLD

马茗岗(1989—),男,硕士研究生,主要从事列控车载信号的研究与应用。