基于高分辨率模数转换器的振动信号采集系统设计

2016-12-05俞乐丁国清

俞乐,丁国清

(上海交通大学 仪器科学与工程系,上海200240)

基于高分辨率模数转换器的振动信号采集系统设计

俞乐,丁国清

(上海交通大学 仪器科学与工程系,上海200240)

振动测量是了解工程机械工作状态的重要途径。为了实现振动信号采集需求,需设计一种基于高分辨率模数转换器和差分信号系统的数据采集系统方案。系统包含磁电式检波器、前置电路、高分辨率模数转换器和FPGA,可实现双通道同步数据采样,采样率可达53kSPS。同时以FPGA为控制单元,可以准确迅速的获得信号采样值,保证振动波形测量的准确性。经验证,该电路设计具有较好的实用性。

振动测量;数据采集;模数转换;差分信号处理

工业生产现场环境复杂,检波器输出的连接引线长,对内部噪声、现场干扰等比较敏感,而后期算法对于信号频率、幅值等特征的识别精度要求较高,因此信号采集模块的电路设计对振动信号的测量结果具有重要影响。针对这一现实,提出一种基于高分辨率工业模数转换芯片ADS1271的全差分信号调理采集电路的设计方法,该电路设计具有差分输入、高分辨率的特点,有效保障了数据测量的准确度,硬件电路与算法适合于测量固定频率或频率变化范围较小的机械振动。

1 总体设计

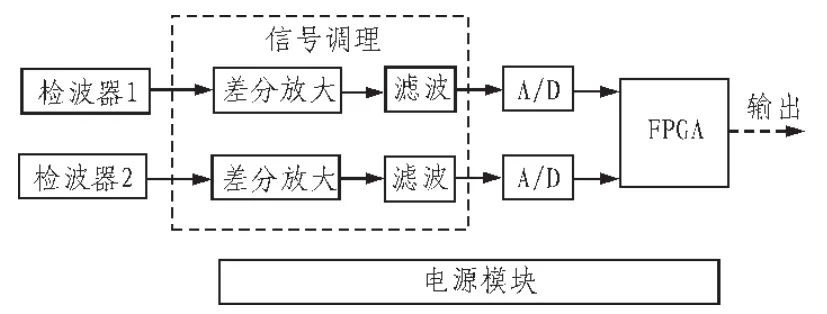

信号采集电路总体设计如图1所示,可分为A/D转换模块、信号调理模块、FPGA控制模块和电源模块。信号采集与处理实现过程为:检波器输出电压信号经前端信号调理电路后输出至高精度模数转换器。FPGA通过帧同步协议模式将转换得到的数字量读出,并可通过若干算法[1-4]得出振动波形的幅值、频率、相位等信息。数据可通过RS485接口向上位机传输。其中抗混叠滤波和放大调理电路配合ADS1271实现同步采集两路检波器信号。

图1 总体结构图

2 硬件设计

2.1差分信号系统

考虑到测量结果对来自系统内外部干扰非常敏感,本设计采用差分信号输入方式。差分信号系统具有以下几个优势[5-7]。第一,差分信号精确度与“地”无关。这是因为在差分信号系统中,使用者可将基准点定为两个输入端的平均信号。这样可以避免因为“地”的电压不一致导致信号系统的精确度下降。第二,差分信号对外部电磁干扰是高度免疫的。差分系统的信号值由两个输入端的的电压之差决定,干扰源对相邻的每一端信号的影响方式几乎相同。这样受到干扰而同时同样变化的信号成分就会互相抵消,输出的信号变化幅度极小。第三,单端信号由两个阈值电压判定输出信号的开关变化,理论上正确,但这容易受到工艺和现场温度变化的影响。在差分系统内,两个输入信号的交点决定了差分信号的开关变化,这样就降低了时序上的误差。

2.2A/D转换模块

传统的针对音频应用的Σ-Δ型ADC的偏移与漂移特性明显劣于可满足DC测量需求的同类型ADC,但是德州仪器生产的24位Σ-Δ型模数转换芯片ADS1271却具有优良的交直流特性[8-9]。在转换操作中,输入信号被内置调制器以超过最终输出数据速率64倍的高速率采样。调制器的量化噪声被移至高频范围内并由内部数字滤波器抽走。ADS1271合并了一个多级线形相位数字滤波器。在不同的输入频率下,线形相位滤波器呈现出常数延时。这个特性意味着从任何输入信号瞬时值到相同的输出数据瞬时值的延时是一个常数并且与输入信号频率无关[10]。这对于之后准确检测出两路传感器信号的相位差是非常重要的。综合考虑电路设计需求,本设计选用ADS1271作为模数转换芯片。

2.2.1工作模式设置

ADS1271可方便地通过引脚设置工作模式:

FORMAT引脚可通过置高、置低来选择数据输出接口协议。ADS1271支持SPI串行接口及帧同步串行接口。本设计将其配置为采用帧同步协议输出格式。

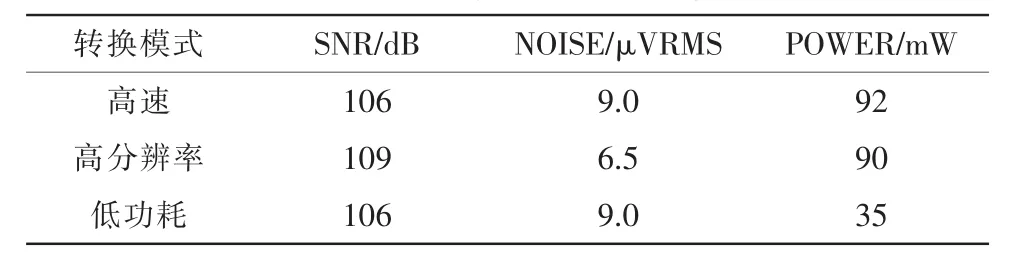

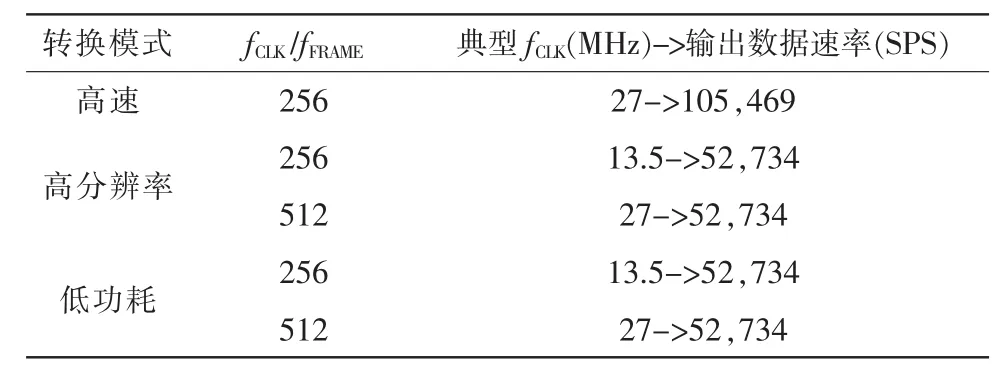

MODE引脚可通过置高、置低、浮空来选择芯片转换模式,ADS1271具有高速、高分辨率和低功耗3种转换模式,配合时钟CLK可确定采样率。本设计使用高分辨率转换模式。

表1 不同转换模式性能比较

表2 帧同步格式不同转换模式下的时钟比

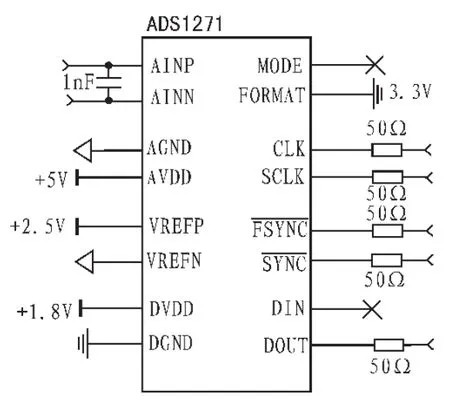

2.2.2输入输出连接

模拟信号通过差分输入对AINP/AINN输入,DOUT是对应的数据串行输出端。通过SYNC引脚可使多通道系统中多个芯片保持同步转换、SCLK为串行输出时钟、FSYNC是帧同步数据起始标志位,FPGA可通过上述接口与ADS1271实现数据交换。另一方面,对于24位的高分辨率A/D转换器,参考电源上的噪声和漂移将影响整个系统的特性。在很多应用场合,对于参考电源“准”的要求不如对其“稳”的要求高。因此需采用2.5 V精密基准源后接电压跟随器电路作为VREF引脚的参考电压。

2.3信号调理模块

模拟输入管脚需要差分驱动以实现ADC规定的特性,但是运放不宜直接驱动Σ-Δ型AD转换器。这是因为ADS1271使用开关电容电路测量输入电压,内部采样电容由输入信号充电和放电。采样电容从输入端采样,每次和运放并联的时候,会呈现低阻,和运放输出阻抗分压,造成电压下降,负反馈立刻开始校正,但运放的压摆率有限,不能立刻响应。于是造成瞬间电压跌落;采样接近完毕时,相当于高阻,运放输出电压上升,但同样是受压摆率限制运放来不及校正,结果是过冲,而这时正是最关键的采样结束时刻[11]。解决办法是在ADC的输入端并联一个小电容,同时在运放输出端与ADC输入端串联一小阻值电阻构成低通电路。电容为采样电容充放电提供瞬态电流,电阻隔离运放与采样电容。

图2 A/D转换模块

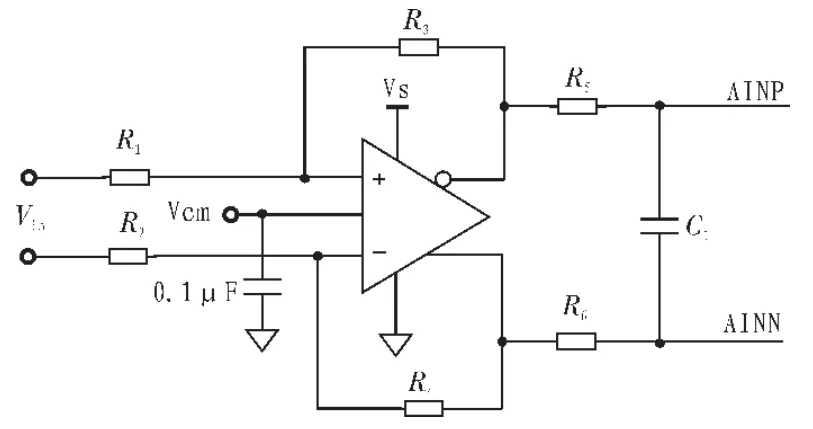

如图3所示,前置信号调理模块的核心是差分放大器LMH6550。R1=R2=1 kΩ,R3=R4=3 kΩ,R5=R6=56 Ω,C1=C2=39 pF。Vin为差分信号的输入端,2.5V共模电压由Vcm引脚接入。R1和R3、R2和R4设定信号增益为3,R5和R6用于把ADC的电容性负载同放大器隔离并确保稳定性。C1能起到平滑电容尖峰作用,同时R5和C1、R6和C1构成低通滤波电路进一步抑制噪声干扰[12]。

图3 差分信号调理电路

2.4FPGA控制模块

Altera公司生产的Cyclone III系列芯片是一款低功耗、高性能、低成本的FPGA。本设计使用EP3C25E144作为主控芯片[13],以实现初始化ADC、接收ADC数字输出、频率幅值计算及结果输出的功能。将ADS1271的模式选择引脚MODE、输出格式选择引脚FORMAT分别与FPGA的通用I/O相连,在数据采集开始前,通过FPGA完成ADC的初始化。同时通过FPGA 给ADS1271输出时钟,精确控制各个通道的同步采样频率。

2.5电源模块

高分辨率ADC易受电源波动影响转换精度,因此采用了开关电源和线性稳压器结合的办法产生多种电压。外部输入电源+24 V先通过开关稳压器降为6 V,继而通过开关稳压器及LDO降为+5 V、+3.3 V、+2.5 V、+1.8 V和+1.2 V。其中+5 V是ADC的模拟电源和放大器的供电电压、并通过基准电压芯片转换为+2.5 VA作为ADC参考电压。+2.5 V、+1.2 V作为数字电压供给FPGA。+3.3 V作为数字电压驱动FPGA 和ADC的I/O口。+1.8 V是ADC的数字电源。为降低电源噪声,所有操作电源输入都使用一个10 μF的钽电容和一个0.1 μF的旁路陶瓷电容就近放置于管脚处。为进一步限制数字模块对模拟器件的干扰,电路的数字地、模拟地和电源地严格隔离且通过磁珠单点连接。

3 软件设计

3.1读操作软件设计

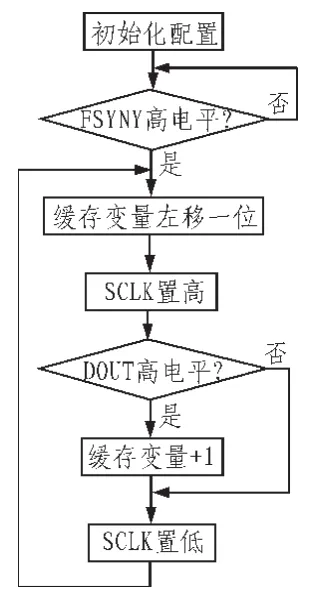

本设计中ADS1271输出采用帧同步方式,数据总线与主时钟要求严格的相位同步,可根据时序图直接通过管脚配置。利用SCLK控制读操作时序,通过直接读取输出管脚DOUT的状态进行数据采集。在高分辨率转换模式下,必须满足要求tSCLK=tFSYNC/128,tFSYNC=tCLK×512。图4所示为一位数据的读取流程。

图4 一位数据读取流程

3.2算法设计

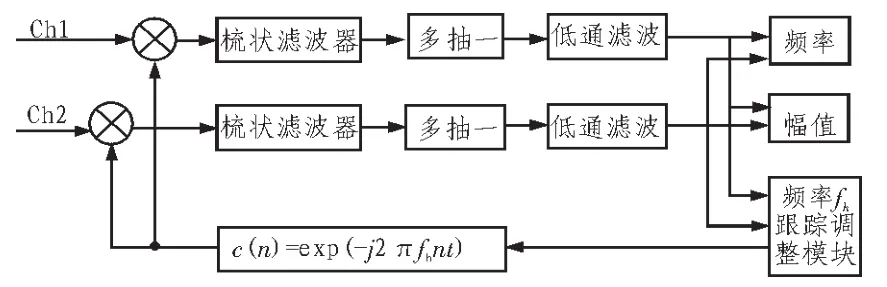

附录14提出了一种用数字锁相环方法处理振动信号的方案,数字锁相环构成如图5所示。

图5 数字锁相环构

任意一路输入信号经采样量化后先与一频率为fh的复数信号相乘,若fh等于被检振动频率,则信号频率移至DC(实际fh可看成是信号频率的近似);用梳状滤波器滤去谐波;这时再通过多抽一环节减少计算量、降低采样频率;最后通过3个FIR低通滤波器滤去剩余干扰,同时根据输出幅值来对跟踪频率fh进行调整[15]。

4 试验结果

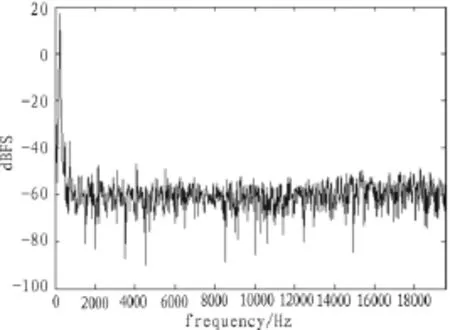

利用 QUARTUS II的Signal Tap II工具可方便地获得FPGA接收的 A/D转换数据。输入差分模拟信号频率约240 Hz。图6为其中一路A/D转换值经过软件处理后获得的信号功率谱。图中可以看出信号功率远大于噪声功率,说明系统能够较好完成传感器信号采集工作。

图6 一路A/D转换值信号功率谱

5 结束语

文中介绍了一种适用于测量固定频率或频率变化范围小的机械振动的信号采集与处理系统设计方法,包含差分信号放大器、A/D转换模块、FPGA主控单元。该系统能快速、准确地采集到磁电式检波器信号,并使用数字锁相环算法计算实际频率值和幅值。通过实验验证,本设计能够较好地采集实际的检波器差分信号,符合设计预期。

[1]So,H C.Time-delay estimation for sinusoidal signals[J].IEE Proceedings-Radar,Sonar and Navigation,2001,148(6): 318-324.

[2]Cho,Nam Ik,Chong-Ho Choi,Sang Uk Lee.Adaptive line enhancement by using an IIR lattice notch filter[J].IEEE Transactions onAcoustics,Speech and Signal Proce-ssing,1989,37(4):585-589.

[3]Chicharo,Joe F,Mehdi T Kilani.A sliding Goertzelalgorithm[J].Signal Processing,1996,52(3):283-297.

[4]牛鹏辉,涂亚庆,张海涛.格型陷波器和DTFT科氏流量计信号处理方法[J].重庆大学学报:自然科学版,2008,30 (11):54-58.

[5]王征宇,章少云.差分信号的测量方法[J].电子与封装,2013 (1):17-29.

[6]蔡国发,章杰,林培杰,等.差分对信号完整性分析[J].电子测量技术,2012,35(1):38-41.

[7]宋正勋,谭宝华.低压差分信号技术[J].长春光学精密机械学院学报,2000,6(2):33-36.

[8]Texas Instruments.24-Bit,Wide Bandwidth Analog-to-Digital Converter[EB/OL].[2015-07].http://www.ti.com.cn/cn/ lit/ds/symlink/ads1271.pdf

[9]黄菁,刘青春.基于Σ-Δ型模数转换器的动态数据采集系统设计[J].仪表技术,2011(7):28-30.

[10]李灵华,何丽君.24位高带宽Δ-Σ模/数转换器ADS1271的原理及应用[J].现代电子术,2007,30(16):4-6.

[11]ADI公司.ADI放大器应用笔记[M].北京:北京航空航天大学出版社,2011.

[12]Texas Instruments.Differential,High-Speed Operational Amplifier[EB/OL].[2015-07].http://www.ti.com.cn/cn/lit/ds/symlink/lmh6550.pdf

[13]ALTERA.Cyclone III Device Datasheet[EB/OL].[2015-07]. https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/cyc3/cyc3_ciii52001.pdf

[14]Belvin S Freeman,Asheville N C.Digital phase locked loop signal processing for Coriolis mass flowmeter.US.Patent No. 580474[P].1998-9-8.

[15]徐科军,徐文福.基于数字锁相环的科氏质量流量计信号处理方法[J].计量学报,2003(4):122-128.

Design of the vibration detection system based on high-resolution A/D converters

YU Le,DING Guo-qing

(Depertment of Instrument Science and Engineering Shanghai Jiao Tong University,Shanghai 200240,China)

Vibration detection is an important way to monitor the status of mechanism.Acircuit based on high-resolution A/D converters and the differential signal processing system is introduced in this paper in order to meet the signal acquisition requirement of mechanical vibration.The system contains magneto-electric sensors,24 bit A/D converter module and FPGA,which can accomplishtwo-channel synchronous data acquisition.FPGA is the main control unit.It will acquire the sample data quickly and precisely.The experiment shows that this circuit has strong practicability.It can be adopted to improve the accuracy of vibration detection.

vibration detection;data acquisition;analog-to-digital converter;differential signal processing

TN06

A

1674-6236(2016)22-0187-03

2015-11-14稿件编号:201511127

俞 乐(1990—),男,上海人,硕士研究生。研究方向:智能仪器设计。