应用于音频设备的14-bit Sigma-delta 调制器的设计

2016-12-05代田慧彭晓宏

代田慧,彭晓宏

(北京工业大学 北京100124)

应用于音频设备的14-bit Sigma-delta 调制器的设计

代田慧,彭晓宏

(北京工业大学 北京100124)

文中针对AUDIO CODEC IP核项目的实际需求,设计了一款应用于音频设备的14-bit Sigma-delta调制器。采用过采样率(OSR)为256倍的2阶1-bit CIFB结构,应用了包含电路级噪声和非理想因素影响的simulink模型进行行为级仿真。在华力HLMC 55 nm CMOS工艺下,Sigma-delta调制器采用开关电容积分电路来实现,各级积分器采用特殊的开关控制以减小电容大小,从而减小芯片面积,其测试结果可以达到SNDR=84.1dB(ENOB=13.67 bits)。

音频设备;Sigma-Delta调制器;过采样;开关电容

随着消费类音频设备在市面上大量使用,例如:数字电视,手机多媒体等[1-4]。为了能够满足消费需求以获得更好的声音质量,高分辨率的模数转换器(ADC)得到了十分广泛的应用。ADC可分成两种类型:Nyquist采样率ADC和过采样ADC[5-6]。传统的Nyquist采样率ADC,是用两倍或略大于两倍截止频率的采样频率对模拟输入信号进行采样,对所采样的幅值均匀量化,并用二进制编码来表示所需量化的电平[7]。由于电路元件在工艺实现上很难达到较高的精度,所以传统Nyquist采样的ADC要提高分辨率将会变得非常困难。

一般在高精度ADC核心电路的前端,往往需要过渡带较窄的抗混叠滤波器和采样保持电路,对模拟电路的设计提出了更高的要求,设计不好还会引入谐波失真[8]。除了正常ADC转换电路的噪声,前置电路本身也会引入噪声,为了尽可能的降低这些噪声所带来的影响,就不得不增加积分器的电容值,这样一来,系统的功耗就会跟着增加,而且电容的面积在版图中是较大的,增加功耗的同时又增加了芯片的面积[9]。可见,传统的Nyquist ADC不适合用于要求高分辨率的数字音频应用领域。

然而,过采样的Sigma-delta ADC己经是现今CMOS工艺中实现高精度转换器的主流方法,由于其结构中拥有数字抽取滤波器部分,很好的契合了现今CMOS大规模集成的条件,从而可以将模拟调制器部分比较方便地和数字电路集成[10]。而Sigma-delta调制器是Sigma-deltaADC中最为核心的模块,其主要作用是通过过采样和噪声整形两大技术将音频信号范围(20 Hz~20 kHz)之内的噪声推向高频,从而降低带内噪声,以实现高精度的模数转换功能。可见Sigma-delta调制器设计的好坏直接决定了整个ADC的性能。

1 调制器的simulink建模及仿真

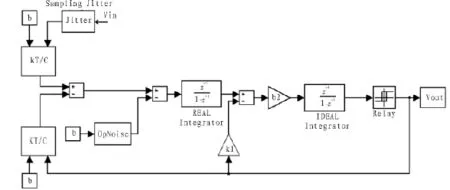

为了有效指导调制器电路的设计,在Simulink/Matlab的环境下,对sigma-delta调制器进行了带有非理想因素影响的模型建立,如图1所示。经过反复优化调整,模型中的系数最终设定k1=b2=1/2,b=1/4。在这里,二阶调制器系统中我们主要考虑了第一级积分器非理想因素的影响[11],其中包括运放的增益、带宽、摆率以及运放本身的噪声,采样开关的热噪声、采样开关的时钟抖动等,下面将调制器所设定的非理想因素模块参数写于表1中。由于第二级积分器对系统性能影响很小,所以采用的是理想积分器(IDEAL Integrator)模型。

整个Sigma-delta调制器系统的采样频率FS=12.5 MHz,过采样率OSR=256,输入频率Fin=5 kHz。在考虑电路设计中所包含的非理想因素影响的情况下,调制器的信噪失真比SNDR=94.1 dB,有效位数ENOB=15.34 bits。

图1 二阶调制器模型

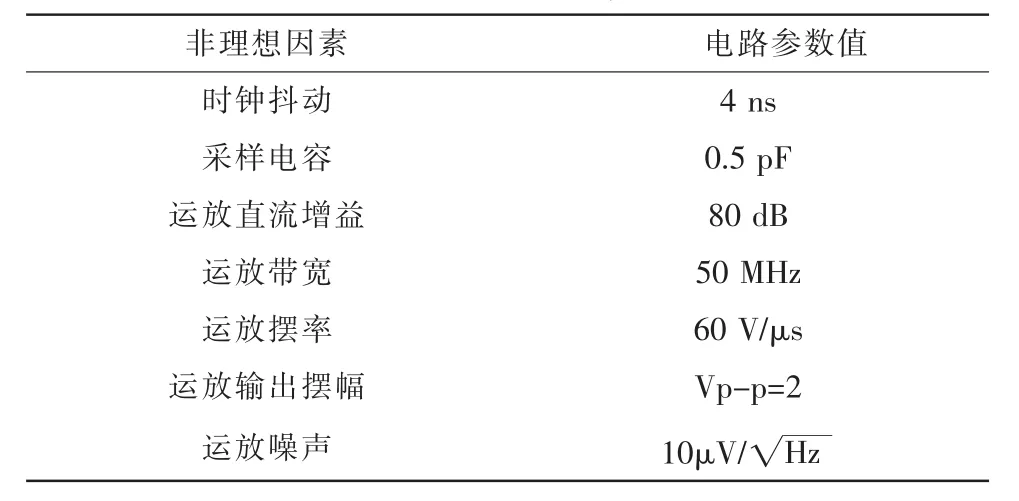

表1 非理想因素模块参数设定

2 调制器电路的设计

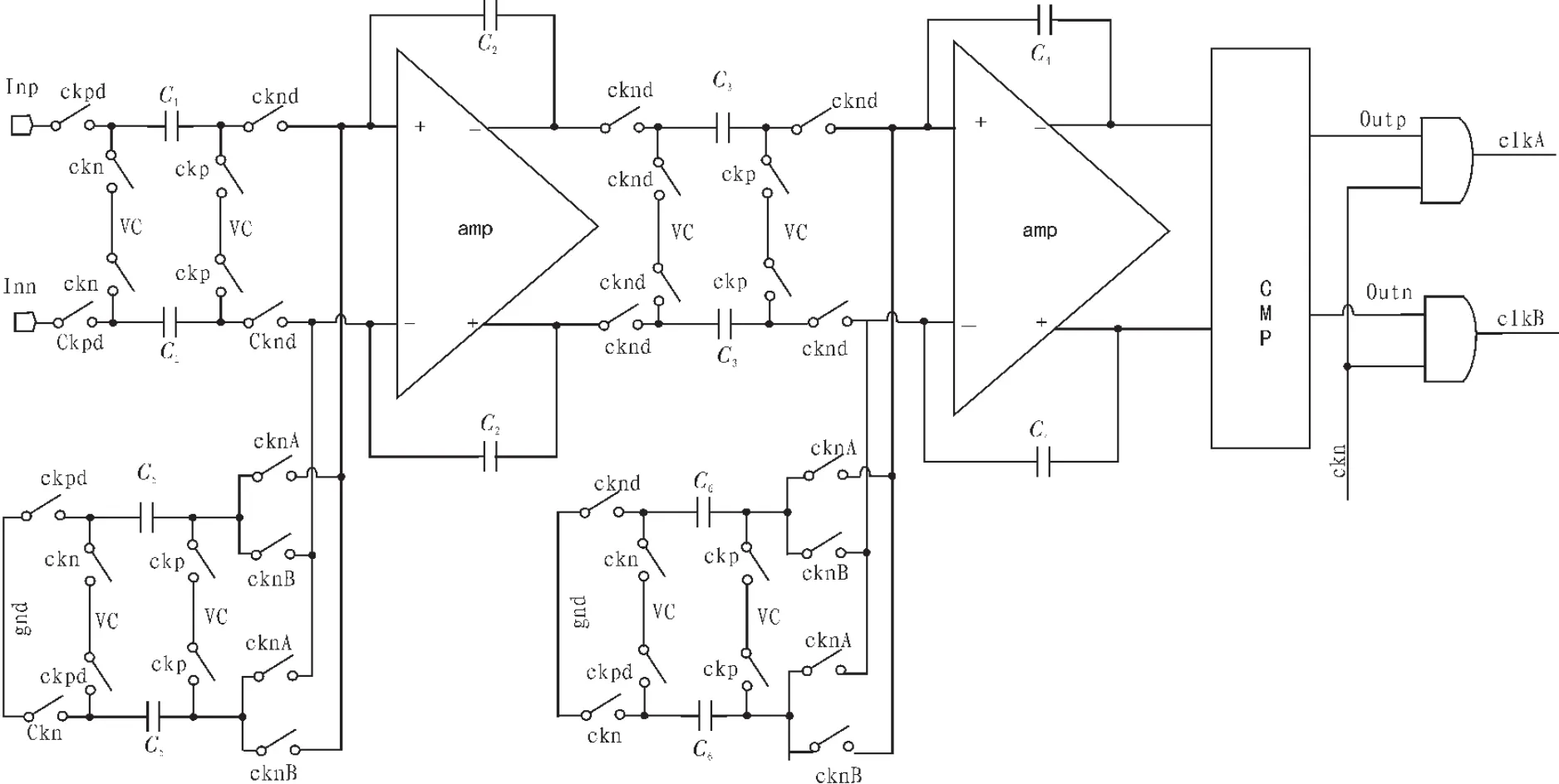

基于开关电容积分器本身所具备的优点:动态范围大、线性度高并且易于CMOS工艺实现[12]。故本设计采用的是全差分开关电容积分器电路来实现2阶1-bit量化CIFB的sigmadelta调制器拓扑结构,结构电路如图2所示。全差分结构可以有效的消除偶次谐波失真,还能抑制电路中的共模噪声,提高电源抑制比并且增加输出摆幅。

从图2的时序开关电路可以看出,该积分器受到两相不8交叠时钟ckn和ckp的控制,这里,信号通路和反馈通路区分开来,以免参考电平受到输入信号的影响。对于输入信号而言,ckp为采样相位,ckn为积分相位。为了消除前面所提到的开关电荷注入效应,图2采用了下极板采样的技术,时钟ckn和ckp较cknd和ckpd稍微提前关断,这样使得采样电容的右端没有了通路,保证了在下一次导通之前,采样电容上的总电荷不会发生变化,而且其他开关的电荷注入或者其他形式的干扰不会对输入信号产生影响,电路的工作性能不会因为开关的动作而发生变化。还有,因为ckp开关是与共模电平相连的,当其断开的时候不会与输入信号产生联系,所影响的只是采样电容上的直流偏移量,这个偏移量可以通过全差分电路中正负通路相减而被相互抵消,从而并不会引起谐波失真[13]。

图2 调制器拓扑图

在电路实现过程中,采样电容值C1大小的选取是尤为重要的。这里参照文献[14-15]中的推导和计算方法可知,两路开关和电容所引起的热噪声在信号带宽内的总功率(Sn)为:

计算得到的积分器的采样电容大约为C1=0.25 pF,基于实际电路噪声抑制的考虑,本设计中给出C1=0.5 pF。由于调制器的系数是根据无源器件电容之间的比值来实现的,所以确定了采样电容值后,积分电容值也就确定了。第一级的系数b=1/4,故积分电容C2=2 pF。由于二阶sigma-delta调制器第二级的系数b2=k1=1/2,故图2中C3=C1=0.5 pF,C4=C2=2 pF,C5=C6=0.25 pF。C5和C6的值之所以不是0.5 pF,是因为在输入信号进行采样的时,C5(C6)上已经贮存了vc·C5的电荷,在积分相时,恰好是2倍的vc·C5电荷转移到积分电容上,其效果相当于C5和C6为0.5pF直接反馈得到的结果。这样的开关控制的目的就是为了减小电容的大小进而减小所占用的芯片的面积。

3 电路仿真及芯片测试

同样在输入信号 Fin=5 kHz,采样时钟频率为 Fs=12.5 MHz,对过采样率OSR=256的2阶1-bit量化的sigma-delta调制器进行仿真。最终的输出时域波形如图3所示,在TT工艺角下,所提取的数字码流在音频信号频率范围内经过FFT分析处理后得到的信噪失真比SNDR=86.6 dB。

图3 调制器输出码流

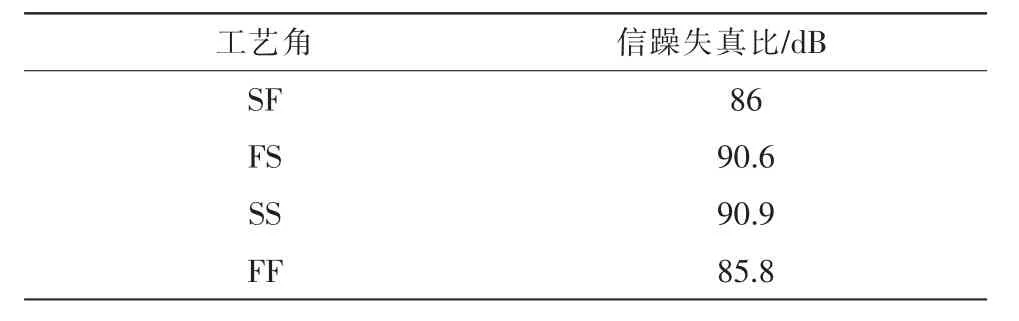

表2给出了在不同工艺角下对调制器输出做FFT分析的结果,可以看出,在不同的工艺偏差下,其性能均能满足设计需求。

表2 不同工艺角的FFT分析

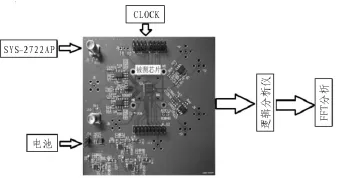

本设计是在华力HLMC 55 nm CMOS工艺成功流片并进行测试的,其测试平台示意图如图4所示。图中被测芯片为整个AUDIO CODEC的测试片,这里只对sigma-delta调制器的精度进行考量。其中用到的外围芯片有串转并芯片(AD8138)和LDO(TPS74701)芯片,电路板是5 V供电,芯片内部供电为3.3 V(模拟部分)和1.2 V(数字部分)。

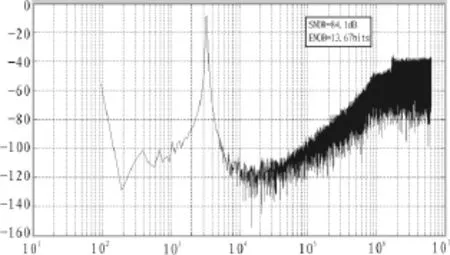

为了确保测试的准确性,测试的输入激励必须保证能够达到更高精度,这里采用的是低失真低噪声的SYS-2722 Audio Precision设备来提供高精度输出正弦信号,其在20 kHz带宽内,1 kHz THD+N能够小于-112 dB。最终对输出数据在音频信号频率范围内做FFT分析,可以达到信躁失真比SNDR=84.1dB(13.67 bits),如图5所示,测试结果与仿真结果非常接近,满足设计需求。

图4 测试平台示意图

图5 输出数据FFT分析

4 结 论

针对AUDIO CODEC IP核项目设计的实际需求,文中设计了一种应用于音频设备的14bit Sigma-delta调制器,采用过采样率OSR为256倍的2阶1-bit CIFB结构。为了使其结构能够更好的达到实际电路设计的性能需求,我们在电路设计之前要考虑实际电路设计中存在的诸多非理想因素对sigma-delta调制器性能的影响,所以在Matlab环境下,给出了带非理想因素的simulink模型的仿真结果,并以此为参考完成电路的设计。在华力HLMC 55nm CMOS工艺下,完成了对Sigma-delta调制器电路的设计,电路设计中的各级积分器采用特殊的开关控制以减小电容的大小,从而减小了芯片使用面积。并且开关的有效控制还可以降低系统噪声,防止寄生效应。在输入信号Fin=5 kHz,采样时钟频率为Fs=12.5 MHz的情况下,对芯片进行测试,其信噪失真比SNDR=84.1 dB (13.67 bits),和调制器的仿真结果非常接近,达到了设计的指标。

[1]刘益成罗维炳.信号处理与过抽样转换器[M].北京:电子工业出版社,1997:1-215.

[2]Wu R,Huijsing J H,Makinwa K A.A 21b±40mv range read -out ic for bridge transducers[C]//Solid-State Circuits-Conference Digest of Technical Papers(ISSCC),2011 IEEEInternational,IEEE,Year:110-2.

[3]Michel F,Steyaert M.A 250mV 7.5μW 61dB SNDR CMOS SC ΔΣ modulator using a near-threshold-voltage-biased-CMOS inverter technique[C]//Solid-State Circuits Conference Digest of Technical Papers(ISSCC),2011 IEEE International,IEEE,Year:476-8.

[4]NANDI T,BOOMINATHAN K,PAVAN S.A continuoustime ΔΣ modulator with 87dB dynamic range in a 2MHz signal bandwith using a switched-capacitor return to zero DAC[C]//IEEE CICC.San Jose,CA,USA.2012:1-4.

[5]Moussavi S,Leung B.High-order single-stage single-bit oversampling A/D converter stabilizedwith local feedback loops[J].IEEE Transactions on Circuits and S ystems11,1994:19-25.

[6]赵福菊.16位具有前馈结构的三阶 Delta-Sigma ADC设计[D].哈尔滨:哈尔滨工业大学,2010.

[7]杨骁,杨静,凌朝东,等.ADSL中宽带ΔΣ调制器的系统设计[J].信号处理,2011,27(2):309-312.

[8]T.Salo,S.Lindfors,and K.Halonen.An 80-MHz bandpass ΣΔ modulator for 100-MHz IFreceiver[J].IEEE Solid-State Circuits,2002,37(7):798-808.

[9]沈戈,基于IP核的Soc设计方法及其应用的研究[M].西安:西北工业大学,2002.

[10]Donghyun K,Matsuura T,MURMANN B.A continuoustime,jitter insensitive ΔΣ modulator using a digitally linearized Gm-C integrator with embedded SC feedback DAC [C]//IEEE Symp VLSI Circ.Honolulu,HI,USA.2011:38-39.

[11]Gray R.Spectral analysis of quantization noise in a singleloop sigma-delta modulator with dc input[J].IEEE Transi.On Communications,1989(37):588-599.

[12]Lee K L,Meyer R G.Low-distortions witched-capa-citor filter design techniques[J].IEEE Solid-State Circuits,1985,SC-20(6):1103-1112.

[13]PAN Hui,Abidi A A.Spectral Spurs due to Quan-tization in Nyquist ADCs[J].IEEE Trans.On CAS-I:regulator papers,2004,51(8):1422-1439.

[14]Daniel Marco,David L.Neuhoff,“The Validity of the Additive Noise Model for Uniform Scalar Quantinizers”,IEEE trans.on information theory.Pp1739-1755,Vol.51,May 2005.

[15]Allen P E,Holberg D R.CMOS Analog IC Design[M]. Oxford University Press.2002:535-536.

Design of 14-bit Sigma-delta modulator applied for audio device

DAI Tian-hui,PENG Xiao-hong

(Beijing University of Technology,Beijing 100124,China)

For the actual demand of AUDIO CODEC IP program design,this work is devoted to the realization of a 14-bit Sigma-delta modulator,which employed 2-order 1-bit CIFB topology whose over sampling ratio(OSR)is equal to 256,applied for audio devices.The circuit level noise and non-ideal factor effects are also taken into account with a Simulink model. The proposed modulator is realized by employing switched-capacitor in HLMC 55nm technology and the special control for switches ofintegrator can reduce the capacitance and then reduce chip consumption.Test results of this proposed sigmadeltamodulatorcan reach SNDR=84.1 dB(ENOB=13.67 bits)resolution.

audio device;Sigma-delta modulator;over sampling;switched-capacitor

TN302;TN432

A

1674-6236(2016)22-0043-04

2016-03-22稿件编号:201603296

国家自然科学基金(61204040,60976028);北京市自然科学基金(4123092);教育部博士点基金(20121103120018)

代田慧(1992—),女,河南洛阳人,硕士研究生。研究方向:模拟集成电路设计。